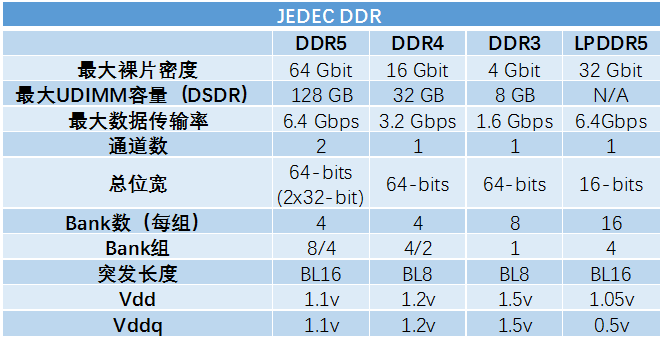

电子发烧友网报道(文/周凯扬)7月15日,JEDEC正式公布了全新的DDR5标准,剑指下一代高性能计算系统。据JEDEC声称,DDR5是为了满足高效率高性能的多种需求所设计的,不仅包括客户端系统,还有高性能服务器,为未来的数据中心和计算机改革提供全新的内存技术。

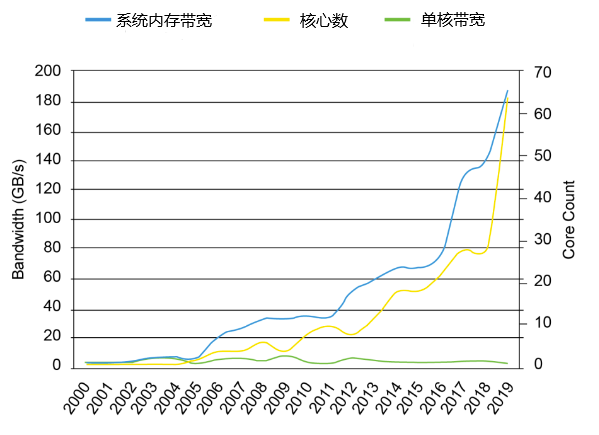

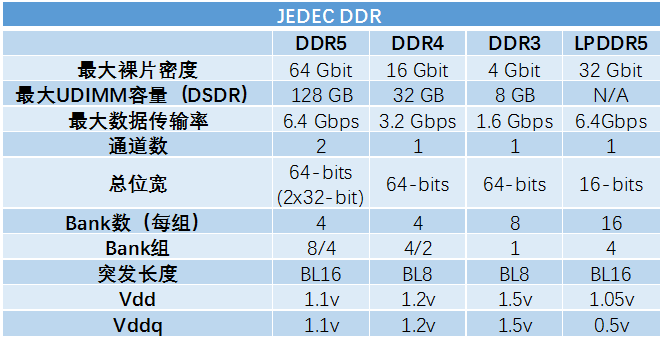

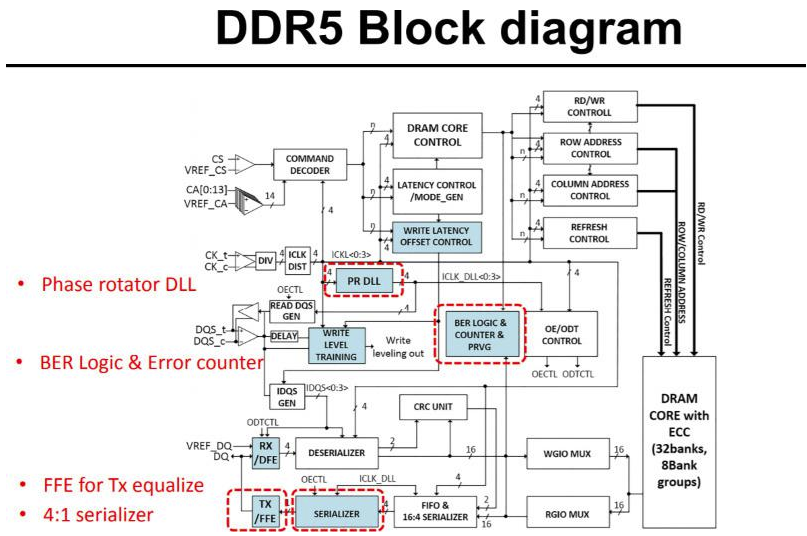

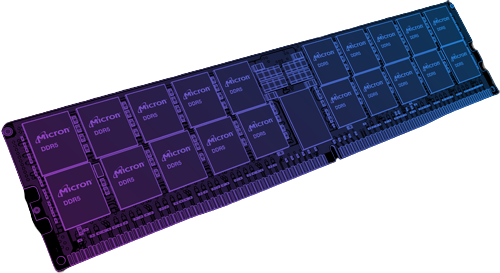

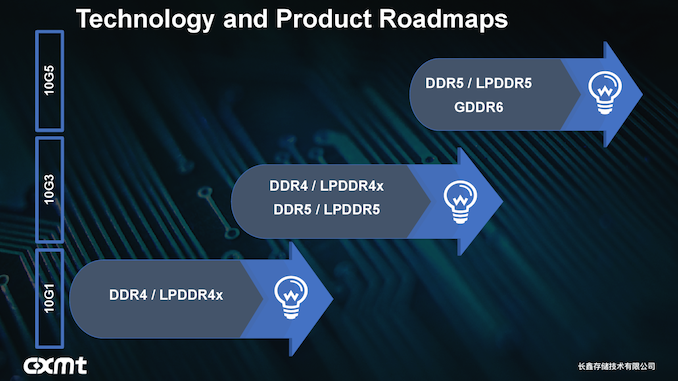

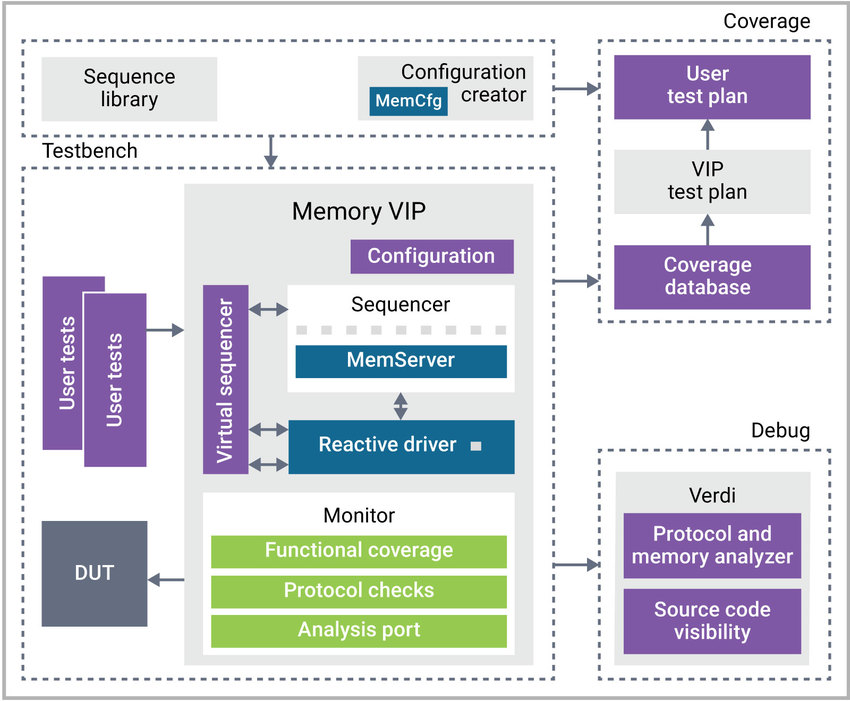

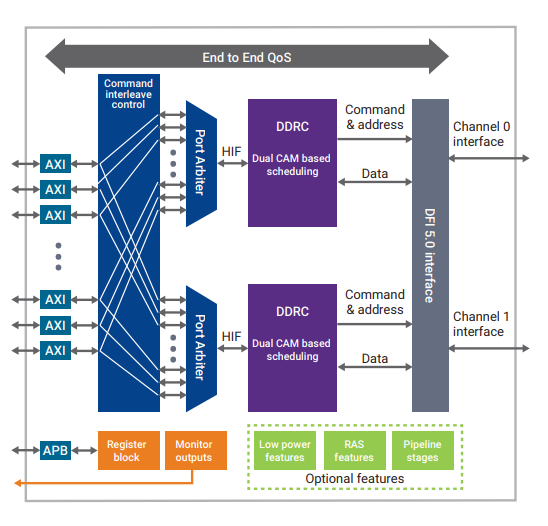

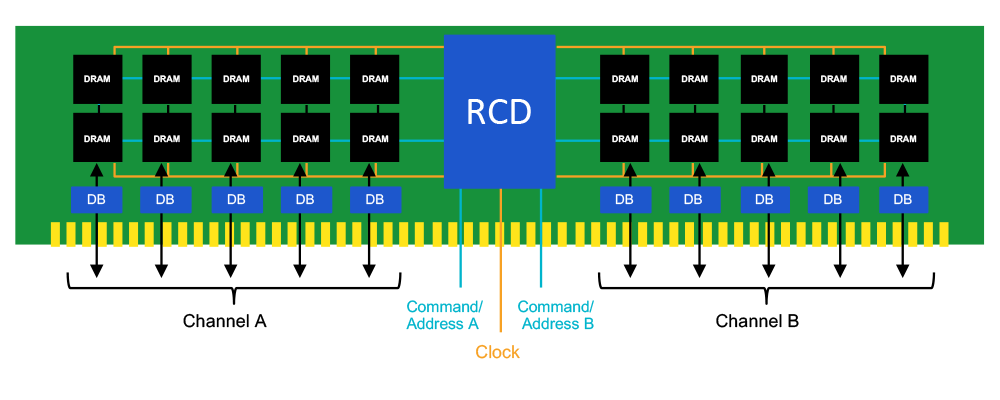

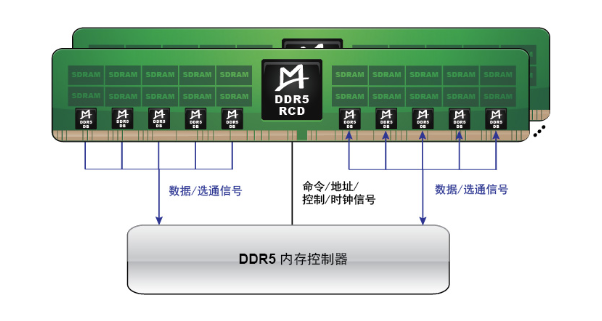

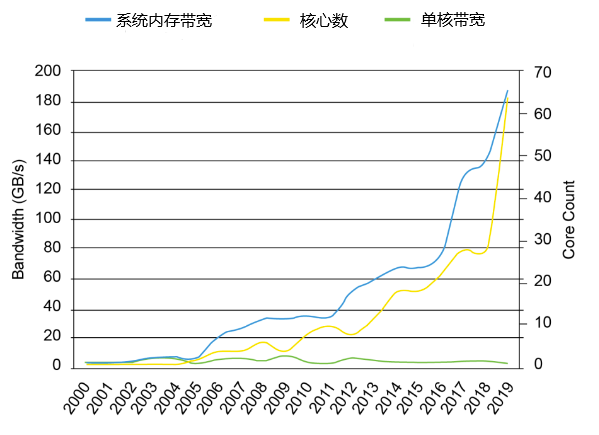

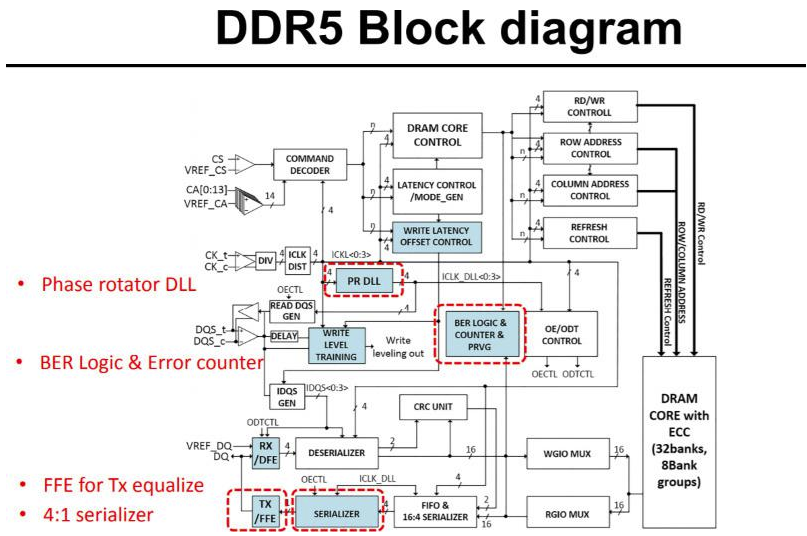

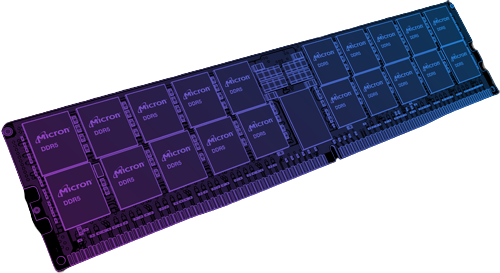

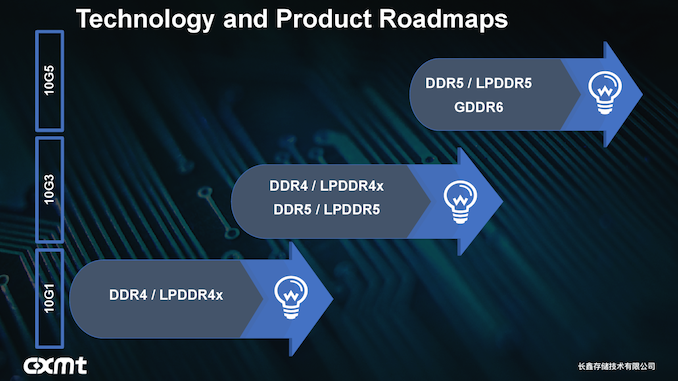

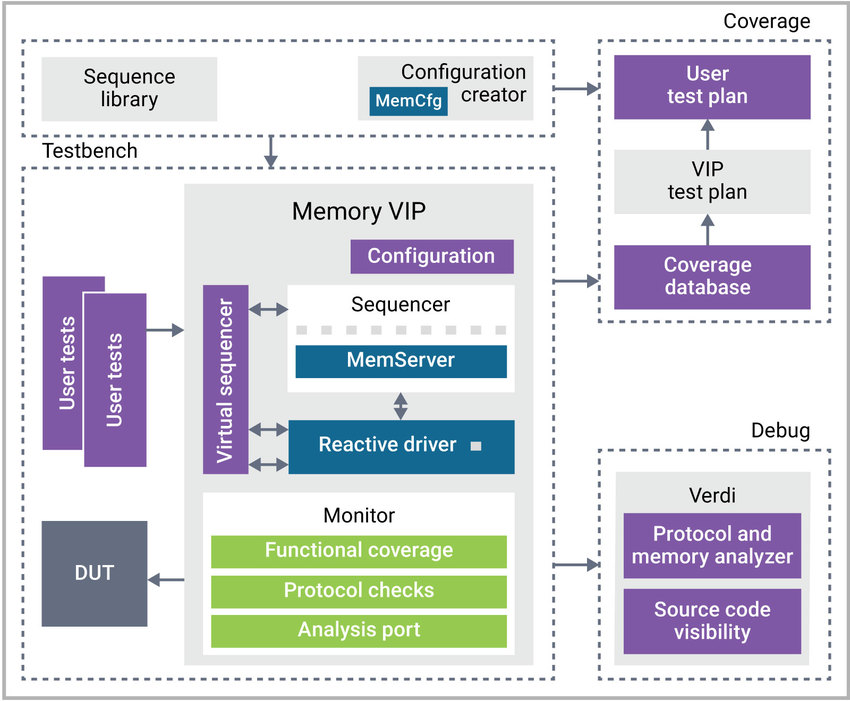

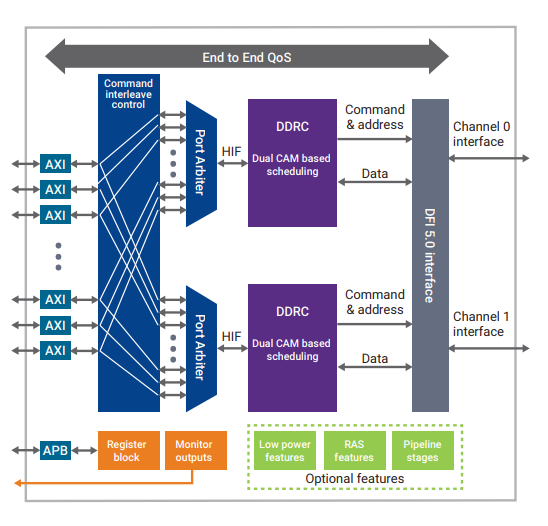

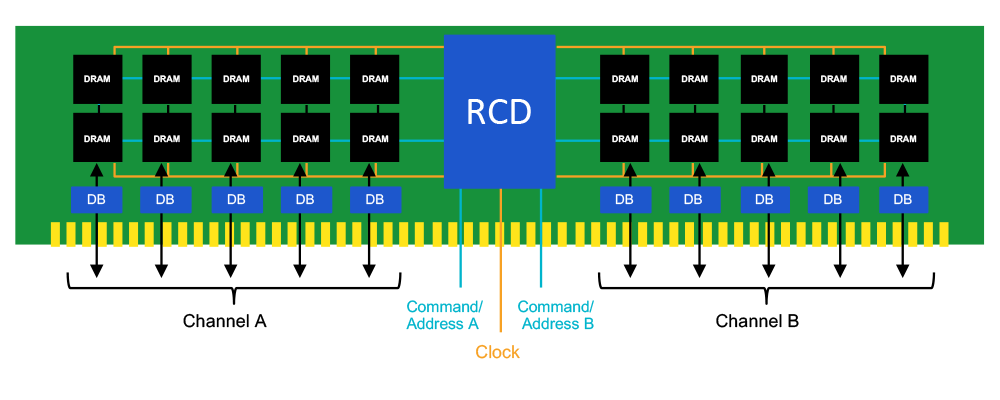

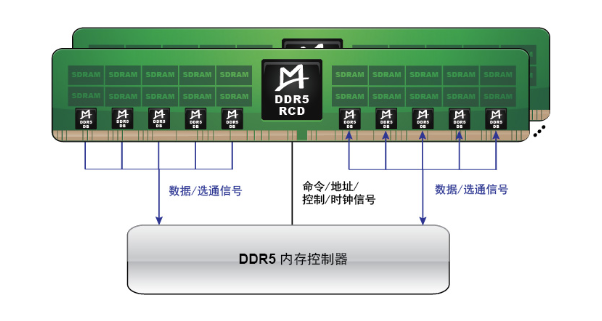

据IDC调研数据显示,针对DDR5的需求将从2020年开始逐步增长,并于2021年占据22%的DRAM市场,在2022年的市场占有率达到43%。在算力飞速发展的时代,CPU制造商仍在提高核心数。以往PC用户使用的是四核CPU,现在大多数CPU制造商都已经在消费者市场提供六核,乃至十二核的高端芯片。在服务器应用上,CPU的核心数量已经高至64核。而DDR4这样的服务器内存解决方案,已经开始难以满足多核心CPU的带宽需求。信号完整性,功率输出以及布局复杂度都限制了每个CPU核心上的带宽。因此发挥下一代CPU的真实性能就需要新的内存架构,这也是DDR5的设计初衷之一。单有内存还不够,对于桌面级以及服务器级别的应用,CPU的内存控制器支持也是至关重要的。去年华为俄罗斯在一次会议中泄露了Intel的产品规划路线图,该图指出Intel将在2021年发布的Sapphire Rapids微架构Xeon处理器中支持DDR5和PCIe5。AMD资深副总裁Forrest Norrod在去年的某次采访中明确表示,2020年下半年发布的Zen3架构 Milan芯片依然仅支持DDR4。据GamersNexus收到的内幕消息,AMD将于2022年发布的Zen4架构CPU和Zen3+ APU会支持DDR5。DDR5可以实现更高的数据传输率、更低的功耗和更高的密度。数据传输率上,DDR5的最大传输速率可达6400 MT/s,是DDR4的两倍,SK海力士也已经开始研制8400MT/s的DDR5内存。与DDR4-3200相比,DDR5-6400可以做到两倍以上的带宽。为了提高内存的传输速率,DDR5有这么几个新特色:1.多抽头判决反馈均衡器(DFE):通过开放了设备中的数据眼图,DFE减轻了高速率下的码间干扰(ISI)2.占空比调节(DCA)电路:该电路可以为内部的读取路径调整DQ和DQS占空比。当这些信号在设备和PCB中传输时,这一功能可以修正自然发生的小型占空比失真,最终优化控制器收到的DQ和DQS信号占空比。3.DQS间歇振荡器电路:该电路可以让控制器监控由于电压和温度漂移,在DQS时钟树上引起的延时。这样的话,控制器设计可以主动决定是否或何时进行重训练,从而优化写入时机。4.具有独立模式寄存器的读取训练模式:相关的数据模式包括默认的可编程串行模式,一个简单的四种模式,以及一个线性反馈移位寄存器生成的模式,为高数据传输率提供更加充足的时间间隙。5.内部参考电压:控制与地址引脚与芯片选择引脚的参考电压。DQ引脚的内部参考电压改善了DQ接收器上的电压裕度,而这几个引脚的内部参考电压分别改进了对应接收器上的电压裕度,让设备可以实现更高的数据传输率。三星在今年年初公布了自己在DDR5上的规划。三星的DDR5采用了最新的TSV 8层技术,让一个DDR5芯片拥有DDR4两倍的栈。每个DIMM也可以提供512GB的容量。三星也将在下一代DRAM上全面利用EUV光刻工艺,先从第四代10nm(D1a)和先进的14nm制程开始。除此之外,三星决定其在韩国平泽市的P2晶圆厂将与下半年开始生产,该厂原定用于“生产下一代高端DRAM”。三星预计基于D1a的16Gb DDR5和LPDDR5将于明年开始量产。2018年11月,SK海力士就成功研制出了第一款达到JEDEC标准的16Gb DDR5 DRAM。10nm级的16Gb DDR5高速高容量内存,将成为他们的主打产品,并将于今年开始量产。SK海力士的DRAM产品规划部门主管Sungsoo Ryu说:“第四次工业革命中,打头阵的是5G、自动驾驶、AI、AR、VR和大数据等应用,而DDR5 DRAM可以用于下一代高性能运算(HPC)和基于AI的数据分析。DDR5也可以为16Gb甚至是24Gb内存提供更加广泛的密度选择,以满足云服务客户的需求。”除了已经提到的性能和功耗差异外,SK海力士也提到了DDR5使用的新技术ECC和ECS。这两大技术可以解决内部的单位错误,同时降低成本。ECS会记录DRAM的缺陷,并为主机提供错误计数,进一步提升服务器系统的透明性,增强其稳定性、可用性以及服务性能(RAS)。美光于今年1月宣布开始筛选DDR5的DIMM,并基于业界领先1znm的制造工艺。美光称DDR5能为下一代服务器在内存性能上带来85%以上的提升。美光计算与网络部门的主管和高级副总裁Tom Eby指出:“随着各种模拟应用的数据快速增长,数据中心的负载也在慢慢濒临挑战,而解决方案就是高性能、高密度和高质量的内存。”随着DDR5标准的正式公布,美光也随之公布了自己的DDR5技术支持计划,提供技术资源、产品以及生态合作伙伴,加入这一计划的公司包含Cadence、Renesas、Synopsys、Montage和Rambus。长鑫研发出了首颗量产的国产DDR4内存芯片,其8GB和4GB的DDR4内存产品也已经上市。其DDR4产品使用长鑫的10G1(19nm)工艺,相同工艺也将用于今年下半年投产的LPDDR4X产品。据其产品规划图显示,长鑫将开发基于10G3工艺(17nm)的DDR4、LRDDR4X、DDR5和LPDDR5产品,未来还有基于10G5的DDR5/LPDDR5和GDDR6。目前长鑫存储已经建成了第一座12英寸晶圆厂并投产,并计划再建两座晶圆厂。DDR5标准公布后,Synopsys也公布了业界首个兼容该标准的DDR5 DRAM/DIMM 验证IP(VIP)。用于DDR5的Synopsys VC VIP以易用性、快速集成能力以及高性能实现了下一代内存设备的设计与验证,进一步加速了验证这个过程。此外Synopsys DesignWare的DDR5/4 PHY和控制器IP也可以在高至6400 Mb/s的速率下运行,支持DDR5标准的各种特性。DesignWare DRR5/4控制器多端口AXI配置 / SynopsysRambus的DDR5服务器DIMM缓冲芯片组是业界首个为下一代DDR5开发的半导体。该芯片组可以提升内存容量,同时保持DIMM的峰值性能。这些增益对于未来对数据密集的应用来说非常关键。DDR5数据缓冲器(DB)和寄存时钟驱动器(RCD)用在DDR5的服务器内存RDIMM和LRDIMM中,与未缓冲的DIMM相比,前者可以实现更高的的带宽、性能和容量。RDIMM和LRDIMM减少了CPU的负载,改善了控制/地址总线上的信号完整性。更重要的是,DDR5 DB将减少数据总线上的有效负载,如此一来可以在模块上加入更大容量的DRAM。以内存接口芯片为主营业务的澜起科技也公布了自己的DDR5接口芯片,包括DB芯片M88DR5DB01和RCD芯片M88DR5RCD01,支持DDR5-4800。据其公司投资者关系记录称,澜起于2019年已完成了符合JEDEC标准第一子代的DDR5 RCD和DB芯片工程样片的流片,并于去年下半年送样给客户和合作伙伴测试评估,计划在2020年完成第一子代DDR5内存接口量产芯片的研发。JEDEC预计DDR5的总体推广曲线与以往的DDR标准相近,因此我们也许得在12到18月后才能看到DDR5的内存出现在设备中。但随着科技产业的逐渐成熟,JEDEC同时预计DDR5的货架寿命会比DDR4要长。照各大厂商目前的开发速率,未来一段时间内我们必会陆续看到他们的DDR5样品和商用DIMM,相信明年的服务器市场和客户桌面端市场会迎来新的转变。管破解智能识别+AI测温防疫关键

[ 新闻来源:电子发烧友网,更多精彩资讯请下载icspec App。如对本稿件有异议,请联系微信客服specltkj]

全部评论