数字化和云服务的快速部署推动了全球数据中心的增长。数据中心消耗全球近 1% 的电力,这一数字预计还会增长。元宇宙、增强现实和虚拟现实等行业趋势将继续消耗超出地球可持续生产的能源。虽然增加可再生能源是朝着正确方向迈出的一步,但这还不够,由于服务器及其冷却系统消耗着近 40% 的数据中心运营成本,能效成为需要重点关注的另一个领域。

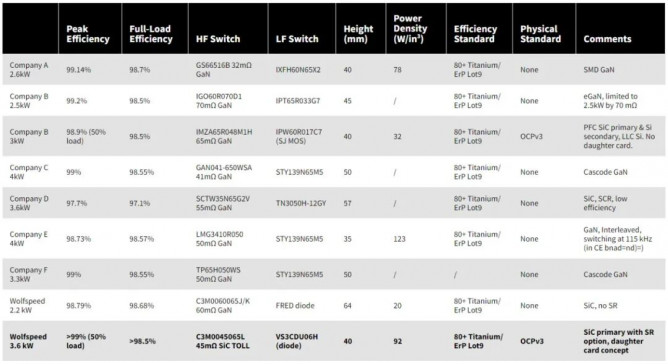

数据中心电源的全球标准也继续朝着更高效率的方向发展。开源计算项目(OCP)3.0 进一步优化硬件来降低能耗,80 Plus 白金和钛金认证要求以及欧盟的(ErP)Lot 9 法规也在不断发展(表 1)。Lot 9 的下一次更新已经安排在 2026 年 1 月。

▲ 表1:Lot 9 和 80 Plus 的要求类似,80Plus 钛金应用要求 PFC 峰值效率超过 98.5%

电源架构演变

随着处理器和服务器功率的增加,数据中心每个机架也将使用更多的电源。随着更高功率密度的发展趋势,数据中心每个模块在 2-4 kW。在第一代 12 V 系统中,这一功率意味着必须处理更高的电流。向服务器提供 1 kW 的功率,传统的 12 V 架构需要提供 83 A 的电流。为了控制 I2R 损耗和解决安全问题,需要在此类系统的线束中使用更多的铜。

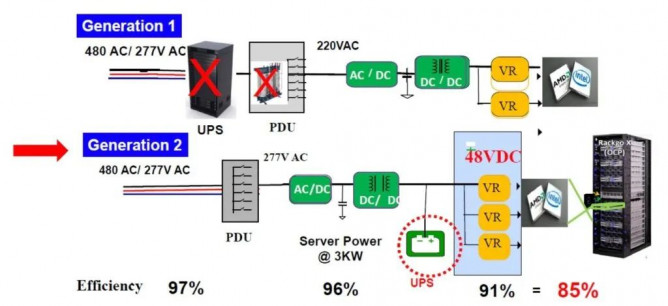

效率提升 1% 可使数据中心节省数千瓦功率,第二代电源架构采用 48 V(图 1),I2R 损耗降低至十六分之一,同时仍低于 UL-60950-1 标准 60 V DC 安全超低电压(SELV)限制,超过该限制需要采取额外的绝缘和测试。为了满足新的能效要求,企业数据中心电力部门因此开始采用 48 V 架构。

第二代机架系统通常采用单独的 2-4 kW 电源模块构建,每个机架使用通过 48 V DC 电源充电的更小型不间断电源(UPS),取代了第一代大规模高压 UPS 和配电单元(PDU)。AC-DC 和 DC-DC 电源不仅为每块服务器主板供电,还会为 UPS 电池充电。由于将第一代中的负载共享和冗余移除,这便要求每个电源在接近满负荷(100%)的情况下运行。

▲ 图1:第二代电力架构节省的全球能源相当于 27 座 1 吉瓦核电厂发电量。来源:Fred Lee,新一代数据中心电源架构

服务器 PSU 面临的挑战

除了上述变化带来的挑战之外,值得注意的是,OCP 3.0、开放式机架 V.2(ORV)和比特币/矿机电源单元(PSU)需要从 2 kW 转至 3-4 kW 范围。由于机架制造商继续要求采用 40 mm(高)尺寸。因此电源供应商需要通过提高开关频率,减小被动元器件体积来提高功率密度、以更高效率减小功率损耗,且更低成本的散热管理满足系统散热要求。

在考虑使用半导体器件技术解决这些挑战时,必须注意带隙、临界电击穿、电子迁移率和热导率方面的差异,所有这些因素都会影响系统的峰值工作温度、电压、效率和热管理要求。

半导体解决方案

尽管硅(Si)是最常见的技术,但与氮化镓(GaN)和碳化硅(SiC)等宽禁带材料相比,硅的带隙较小,这限制了硅的工作温度,其较低的击穿电场限制了硅在较低电压下的使用,而较低的热导率也限制了功率密度。

为满足数据中心电源所需的高效率,功率器件的开关损耗和传导损耗都非常重要。当漏源导通电阻(RDS(ON))较低, 并且随温度变化较小时,传导损耗(即器件的 I2R 损耗)较低。

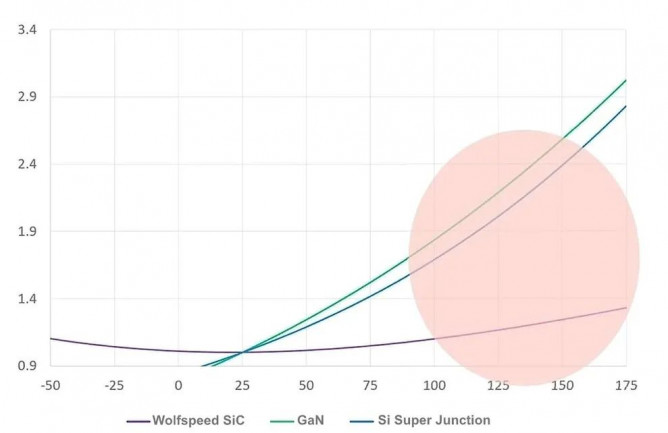

图 2 显示了归一化 RDS(ON) 与温度的关系曲线,许多设计人员都考虑使用这些技术来满足第 2 代数据中心 PSU 要求,包括 SiC、GaN 和 Si 超级结(SJ)。有趣的是,GaN 和 SJ 器件在 25 °C 时都有较低的 RDS(ON),对于数据中心电源而言,这一温度不太实际。由于 GaN 和 SJ 器件的数据手册通常规定 RDS(ON) 在 25 °C 时的值,这可能会误导工程师,让他们误以为该 RDS(ON) 是系统工作时的导通电阻。

▲ 图2:通用图表显示典型 MOSFET RDS(ON)(归一化)随温度发生的变化

图 2 中需要注意的另一个有趣特性是 RDS(ON) 随温度发生的变化。SiC 的曲线几乎保持平坦,但是其他技术的器件显示 RDS(ON) 显著增加,但这一变化对 GaN 来说尤其明显。由于设计人员必须在 120 °C 至 140 °C 的实际结温下使用 RDS(ON),因此 60 mΩ SiC 器件的 RDS(ON) 将达到 80 mΩ,而 40 mΩ Si SJ 或 GaN 器件的 RDS(ON) 将远远超过 80 mΩ。

GaN 的低开关损耗 ≠ 低总损耗

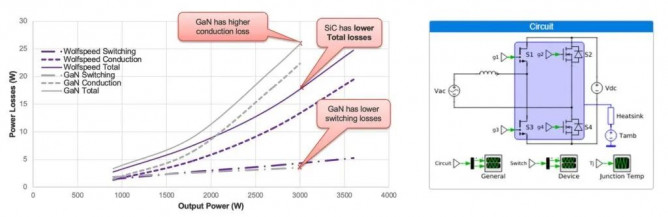

GaN 的高电子迁移率特性使其在非常高的开关频率下具有出色的效率,这点已经得到公认。在本文讨论的技术中,GaN 的开关损耗最低(图 3)。

▲ 图3:在图腾柱 PFC 仿真中比较 Wolfspeed 60 mΩ SiC 与 50 mΩ GaN 器件的研究。功率损耗与输出功率(左)、电路(右)的关系

Wolfspeed 在图腾柱 PFC 仿真中将 60 mΩ SiC 器件与 50 mΩ GaN 器件进行了比较,发现尽管 GaN 在整个功率范围内的开关损耗略低,但这一优势都被随功率增加及之后结温升高而增加的导通损耗所抵消。

由于器件存在功率限制,GaN 测试不得不在 3 kW 停止。该研究清楚地表明,在更高功率下SiC 的总损耗显著降低。图 4 对三种半导体技术的各种器件级性能规格进行了比较。

▲ 图4:SiC 在高电压、高功率和高温应用(例如数据中心电源)中表现出色

乍看之下,我们注意到 GaN 的优势是:在连续导通模式(CCM)同步整流器中,反向恢复电荷 Qrr 最低,开关损耗最低;在低死区时间、高频率和高效率下,时间相关的输出电容 Coss(tr) 最低;在硬开关拓扑中,能量相关的输出电容 Coss(er) 最低,开关损耗最小。请注意,SiC 在这些属性上紧随 GaN 之后,而 Si 则明显落后。

硅优势包括结壳热阻 Rthjc 最低(可提供更好的热性能)和阈值电压 Vth 最高(可提供更好的抗噪能力,使 Si 器件更易于驱动)。注意,GaN 具有极低的 Vth。

最大结温 Tj_max 和雪崩能量、单脉冲 Eas 表明器件的稳定性。如图所示,SiC 最稳定,而 GaN 不具备 Eas 能力。SiC 在整个温度范围内的 RDS(ON) 变化最小,因此高温时的传导损耗较低。在这种情况下,GaN 会显著滞后,从而抵消低开关损耗带来的所有优势。

总之,SiC 的优势有助于在更高的功率水平下,为企业数据中心和类似要求苛刻的应用中提供最高的效率和功率密度。

从封装角度来看

由于 Wolfspeed 开发的 SiC 技术成功从 Si 过渡而来,因此许多常见的表贴和通孔封装也可用于 SiC 产品。然而,GaN 面临封装标准化带来的独特挑战。

例如,GaN 通孔封装并不常见,因为产品需要具有较低的寄生效应,并允许使用超高频开关以最大程度利用材料的优势。GaN 通常采用大型 QFN 或定制封装。大型 QFN 存在电路板级可靠性问题,定制封装缺乏多源可用性,分包商加工能力也不足。

GaN 带来的功率器件封装挑战不止于此。其他常见问题包括:

开尔文源引脚在 SiC 中广泛采用,可减小驱动回路杂散电感,实现更好的开关控制,但在共源共栅 GaN 中并不可行,因为其内部电容以及级联的低压 MOS 等寄生参数无法考虑在内。共源极无法消除,共源共栅 GaN 仅限于 TO-247-3(三引脚)封装,其中栅极振荡的脆弱性限制了开关速度。

市场上的一些定制封装非常薄,限制了散热器的可用空间。

市场上的另一种定制封装具有顶部冷却,这需要使用具有高导热性的热界面材料(TIM)实现器件散热。

另一种用于 GaN 的无引线(TOLL)封装将栅极和开尔文源极放置在不同于标准 Si 的方向上,这使得从后一种技术的过渡变得很麻烦。

▲ 图5:Wolfspeed 的 TOLL 封装明显小于标准 TO-263,并且支持低成本表面贴装

随着市场转向高功率密度设计和更严格的空间限制,无引线(TOLL)封装具有高度低、尺寸小的优势,其无引线封装会降低引线电感,否则这在高频操作中会成为一个问题。这种封装的漏极焊盘面积更大,解决了小封装散热性能问题。

对于数据中心和服务器电源市场而言,TOLL 是一种相对较新的封装方式。然而,Wolfspeed 正在从事这一方面的产品开发,为市场提供支持,例如面向数据中心和服务器电源的新 TOLL 封装。

系统级比较

与基于 Si 的 H 桥相比,基于 SiC 的 CCM 图腾柱 PFC 不仅具有更高的效率,而且在相同或更低的成本下具有更高的功率密度。不同技术之间的效率比较清楚地表明,虽然基于 SiC 和 GaN 的 CCM 图腾柱 PFC 可以实现 99% 以上的效率,但 GaN 仅在非常轻的负载下具有效率优势。如前所述,GaN 的 RDS(ON) 随温度的变化要大得多(图 2),这导致其效率曲线在较高功率/负载下急剧下降。因此,在数据中心等需要全天候或接近全天候满负荷运行的应用中,GaN 无法满足效率要求。

另一方面,SiC 在半负载时的效率与 GaN 相似,在满负载时效率更高(图 6)。

▲ 图6:碳化硅是图腾柱 PFC 的最佳选择,尤其是对于高可靠性应用而言更是这样

从更广泛的角度来看,包括 SiC 和 GaN 基于 CCM 图腾柱 PFC 的功率密度、元件数量和相对成本(表 2),我们注意到在高功率密度应用中,SiC 不仅在效率方面优于 GaN,而且在栅极驱动复杂性、控制和成本方面也优于 GaN。

▲ 表2:SiC 和 GaN 基无桥 PFC 的拓扑和元件分析

在对不同公司的宽禁带器件设计的另一项比较中,Wolfspeed SiC 显示出明显优势(表 3)。需要注意的一些要点是:

许多现有的参考设计要求实现不切实际的散热管理,并限制了设计的灵活性。

由于 RDS(ON) 的温度系数较高,基于 GaN FET 的图腾柱设计在满负载时效率较低。

正如预期的那样,SiC 的低 RDS(ON) 温度系数使 Wolfspeed 的设计从半负载到满负载呈现出近乎平坦的效率曲线。

虽然 SiC 和 GaN 可满足 2-4 kW 范围内的无桥 PFC 要求,但高传导损耗使 GaN 散热设计在 4 kW 以上面临挑战。

为满足 CE 的 EMI 要求,参考设计的系统频率限制在 45-47 kHz 和 60-67 kHz 范围内,将谐波保持在 150 kHz 以下,这就否定了 GaN 的低开关损耗优势。

▲ 表3:市场上宽禁带参考设计的竞争分析

Wolfspeed 的 3.6 kW 解决方案

Wolfspeed 的全新 3.6 kW 图腾柱 PFC 参考设计(表 3,最后一行)旨在解决数据中心和服务器电源挑战,在半负载时效率超过 99%,满负载时效率超过 98.5%,达到 80 Plus 钛金和 ErP Lot 9 要求。

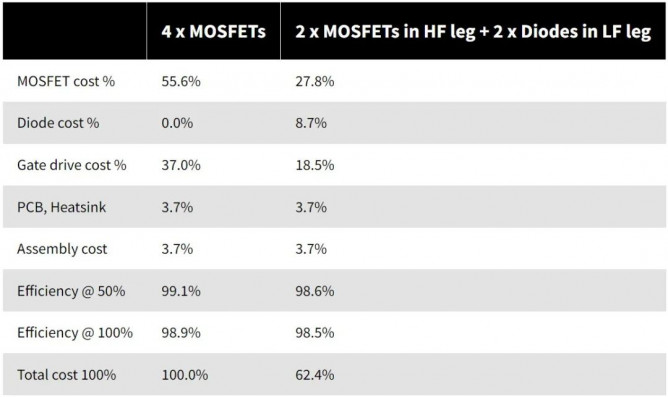

▲ 表4:Wolfspeed 的 3.6 kW 设计中四 MOSFET 和双 MOSFET 选项的效率和成本比较

该设计还提供了一定的灵活性,可以牺牲部分高效率以降低成本,但同时仍能满足上述效率标准(表 4)。低成本选项用二极管取代设计中的低频(LF)管脚的两个 MOSFET,同时保留高频 (HF )管脚的两个 MOSFET。

双子板设计概念使客户能够根据其系统设计优先级灵活选择正确的选项。

在开发此类解决方案时,Wolfspeed 利用其丰富经验,开发出市场上经过最广泛现场测试的 SiC 和碳化硅基氮化镓(GaN on SiC)各类解决方案产品组合。Wolfspeed 的半导体团队最为了解这两种技术的优势和未来潜力,只有 Wolfspeed 才能开发出最适合任何特定应用的技术。