近日,复旦大学、北京大学和清华大学团队在存储芯片上创下新突破。

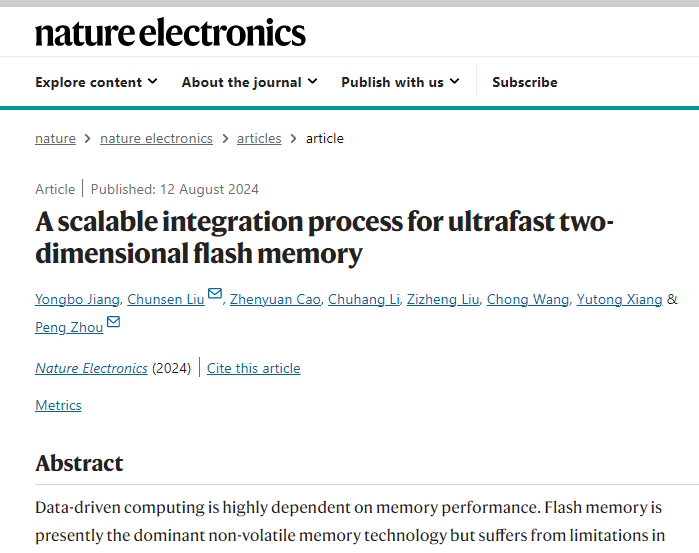

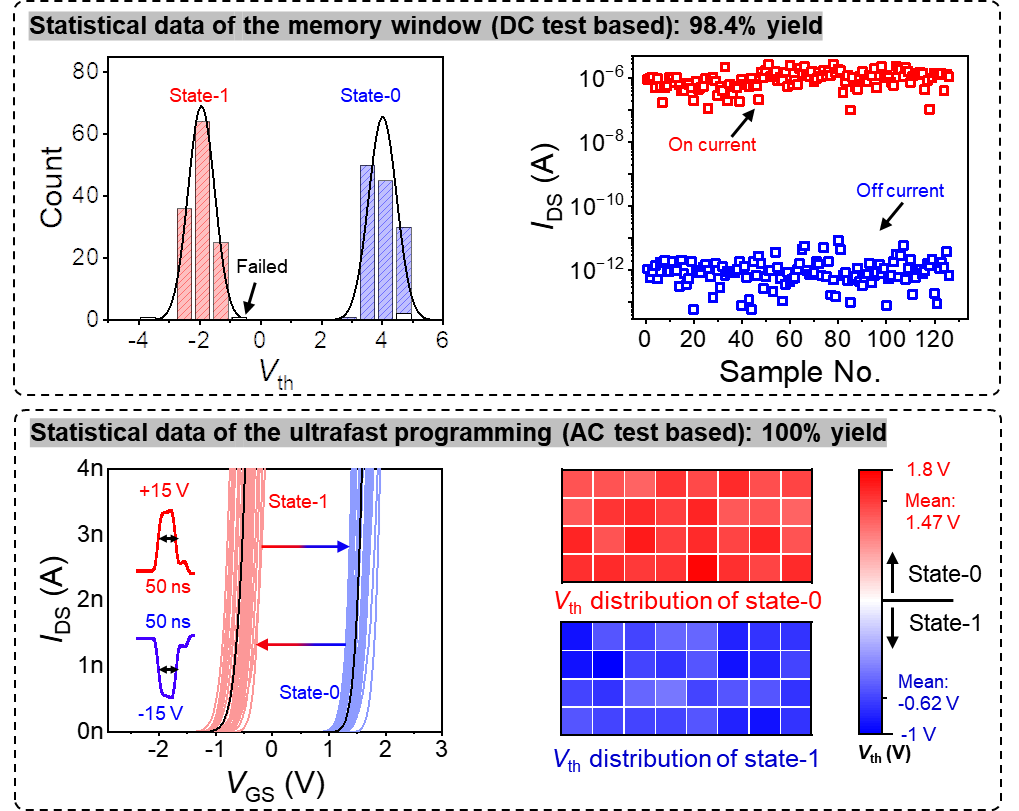

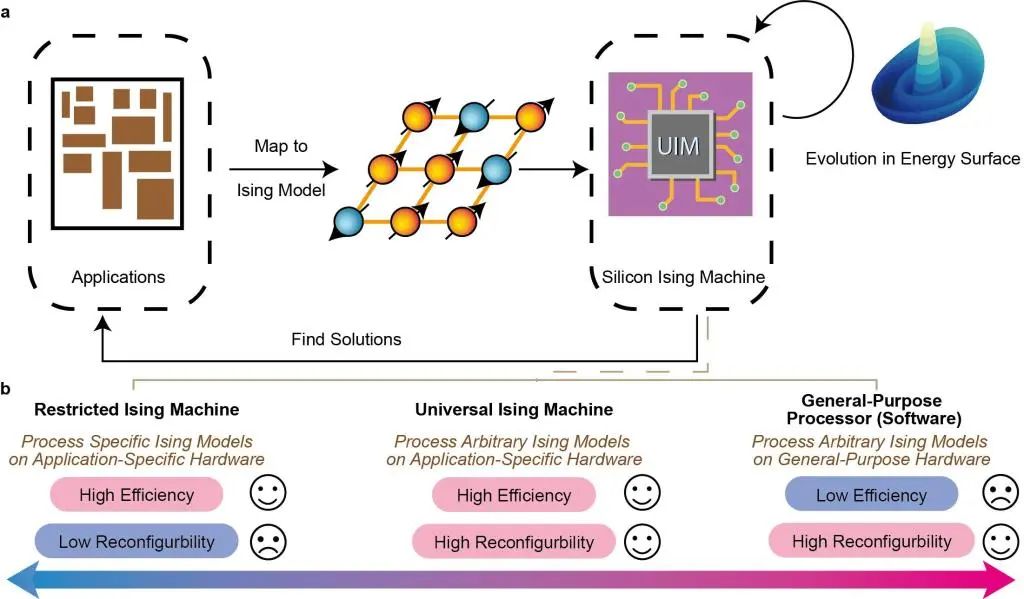

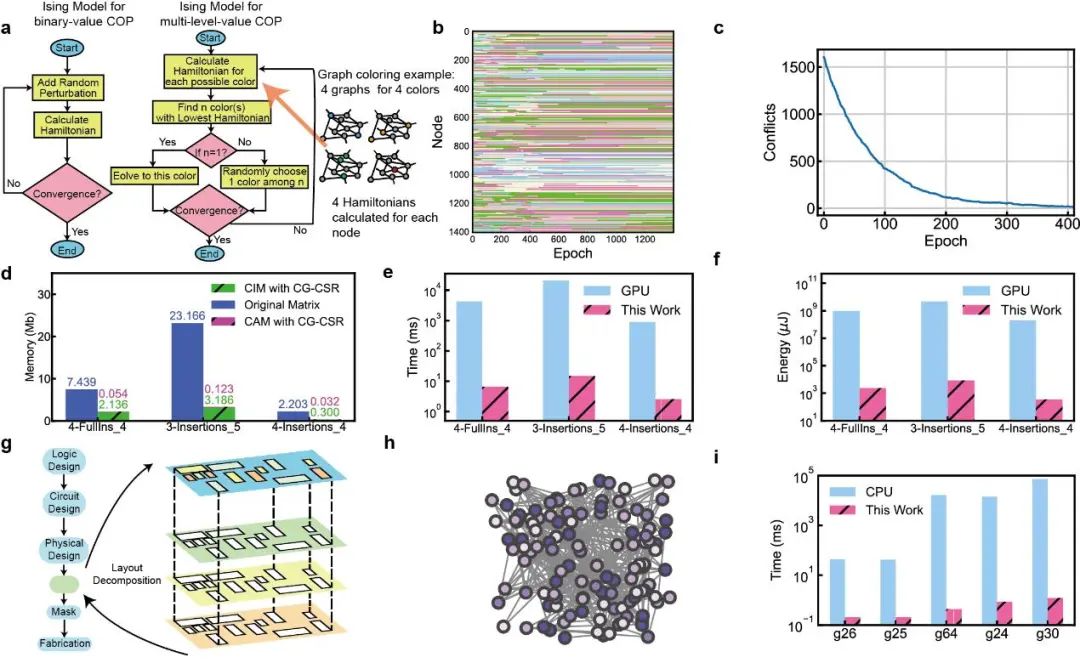

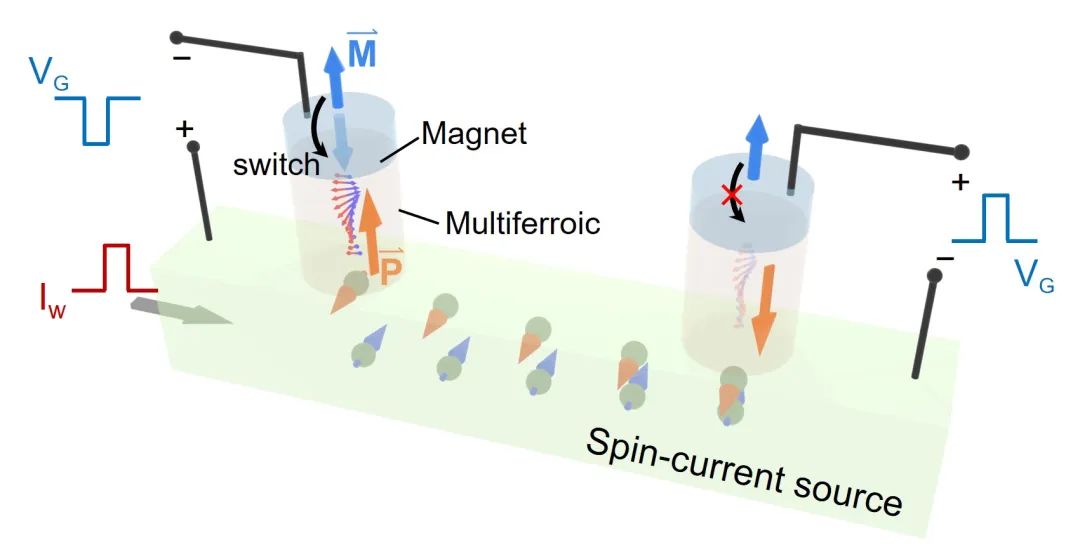

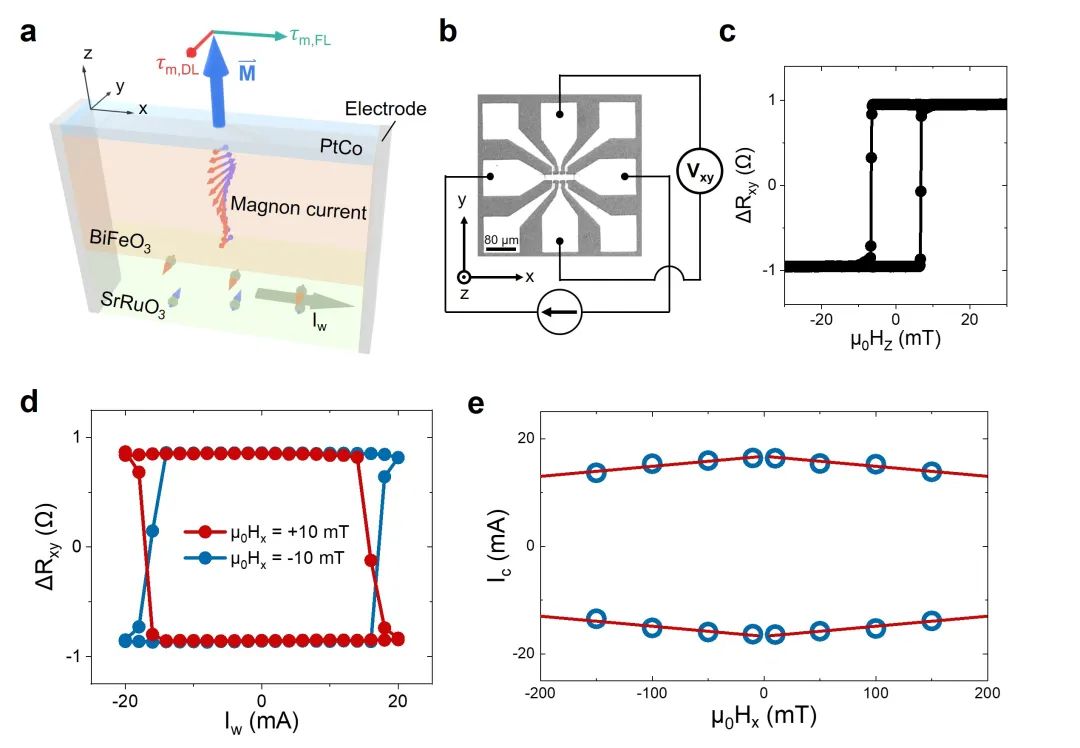

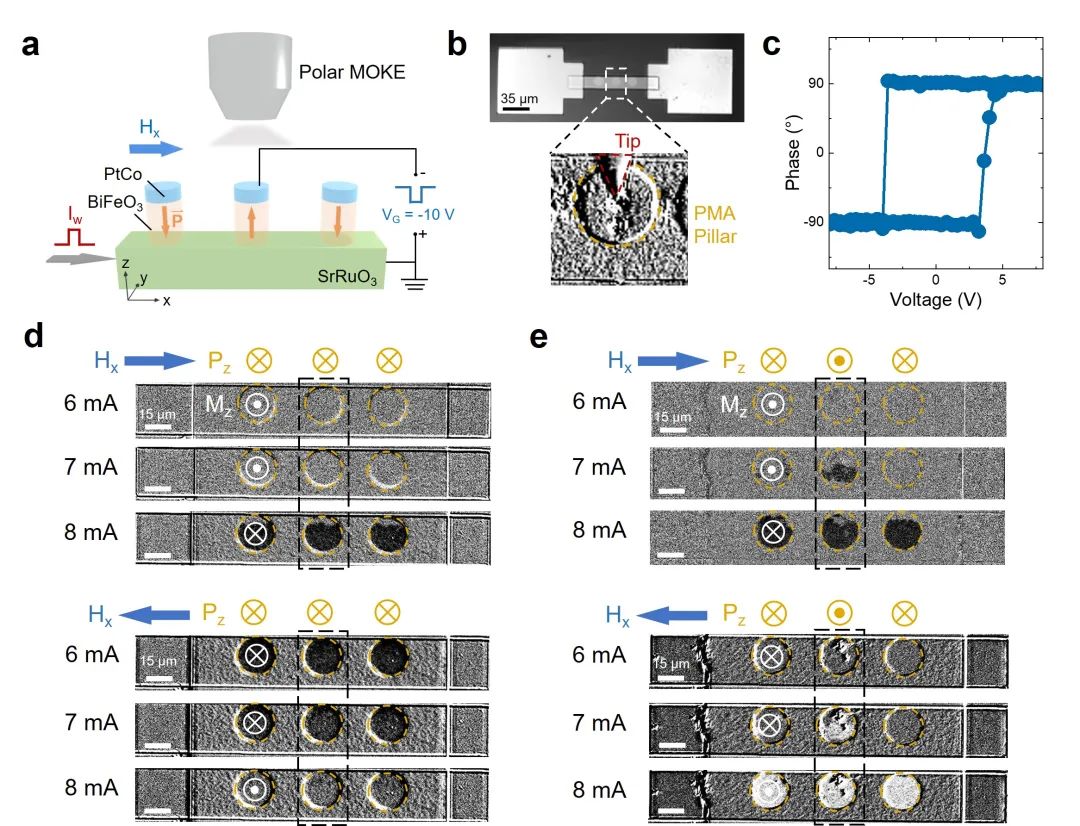

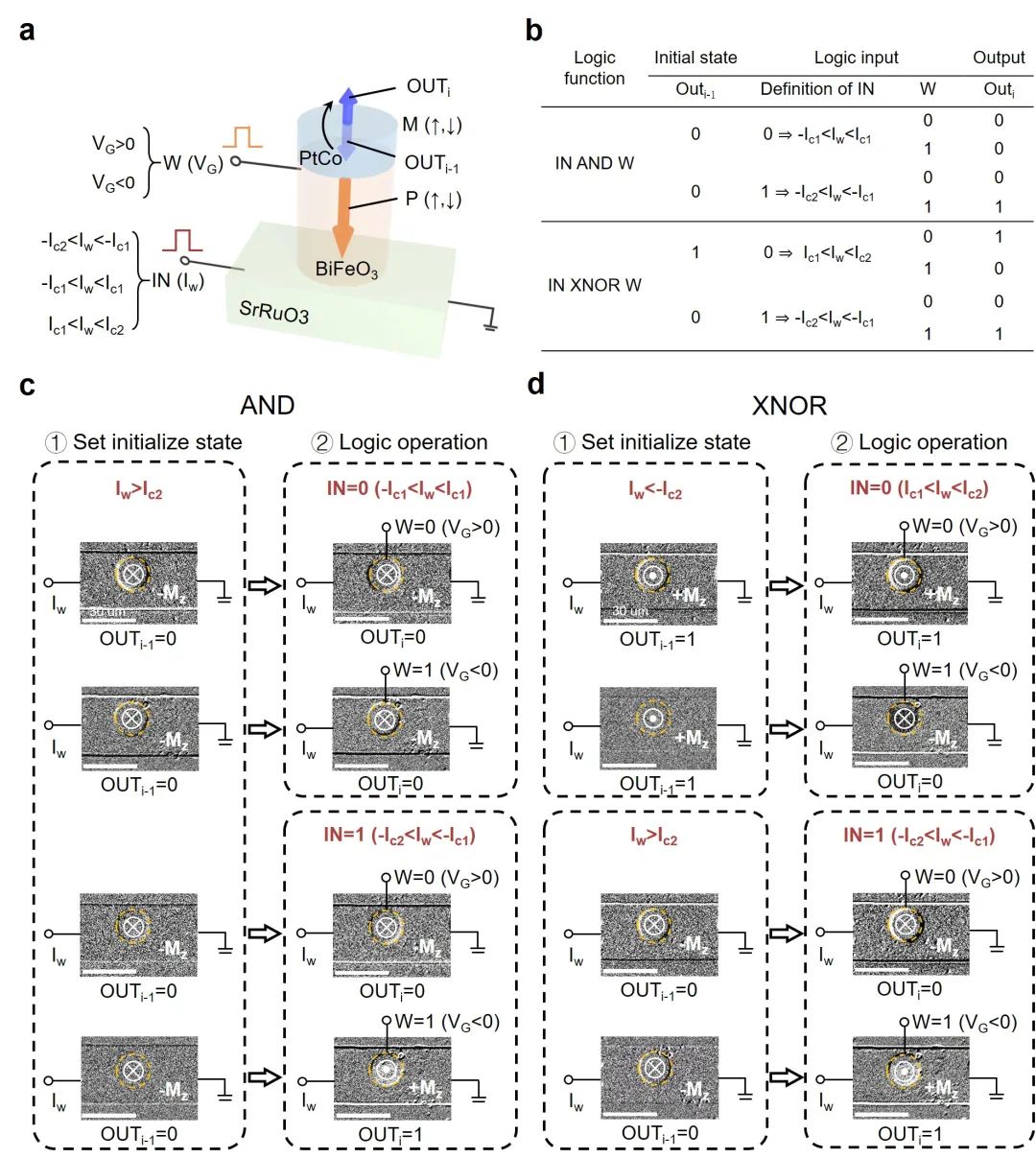

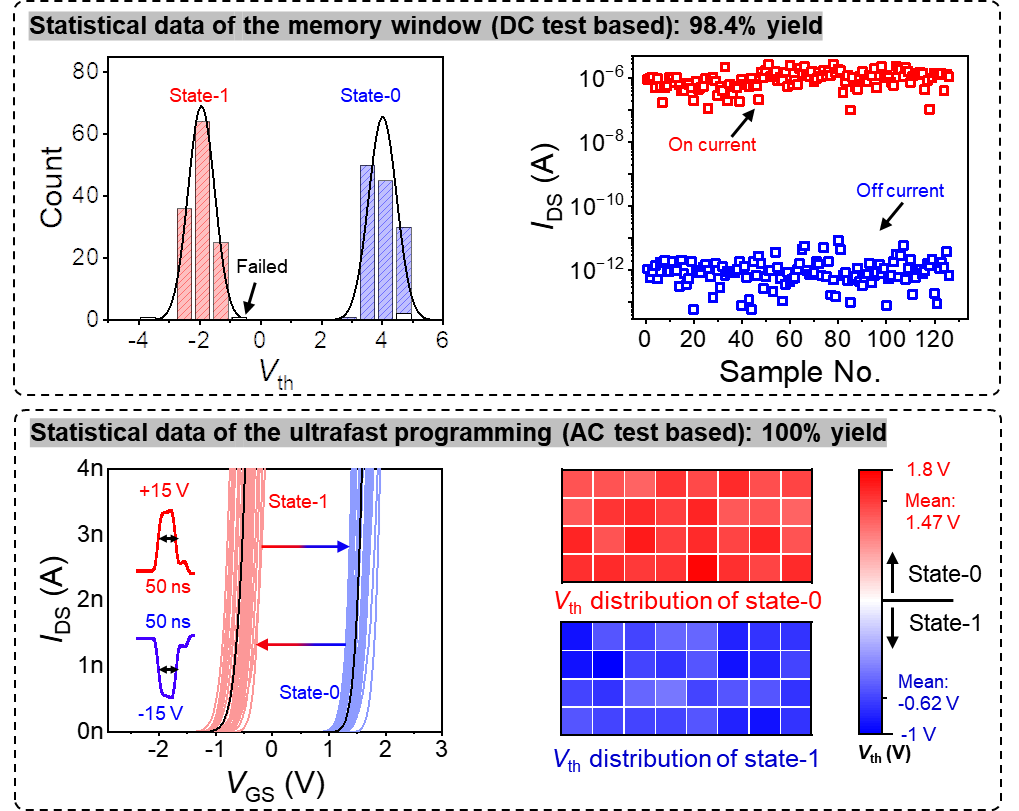

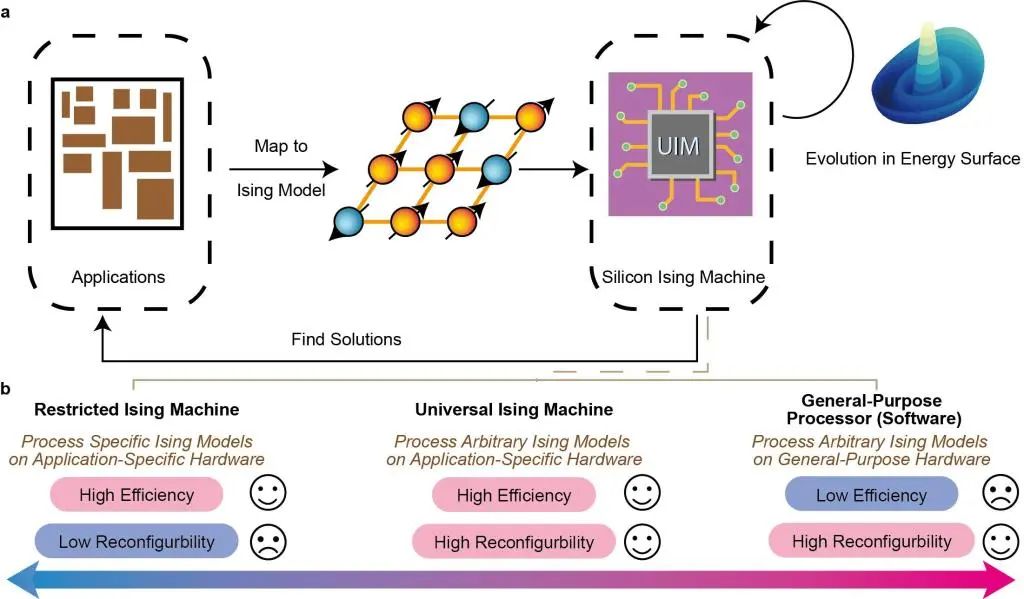

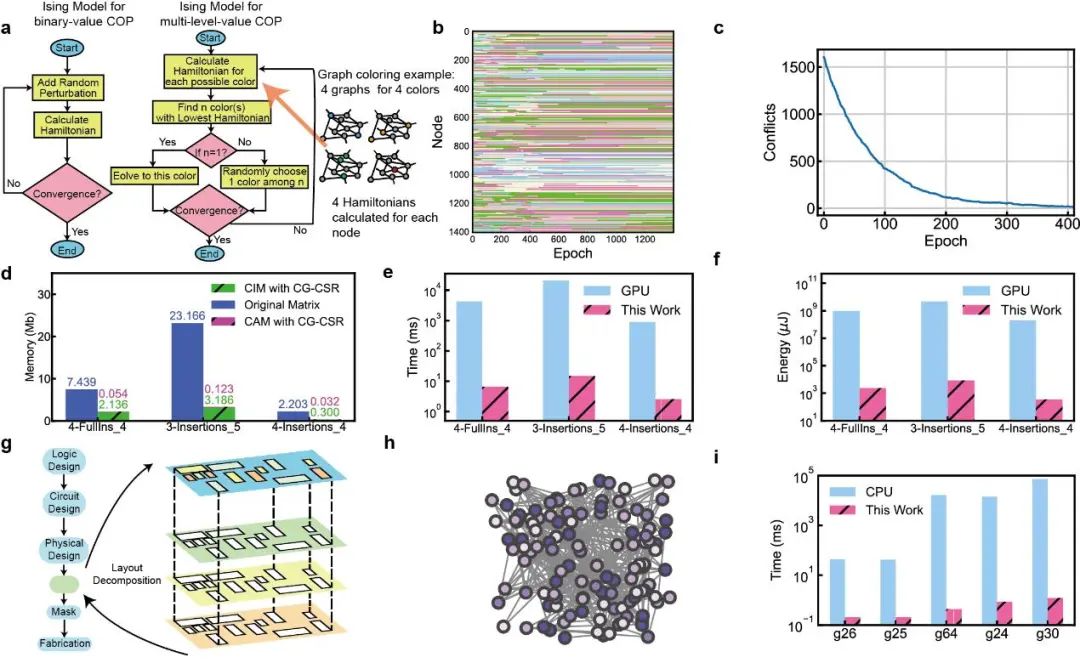

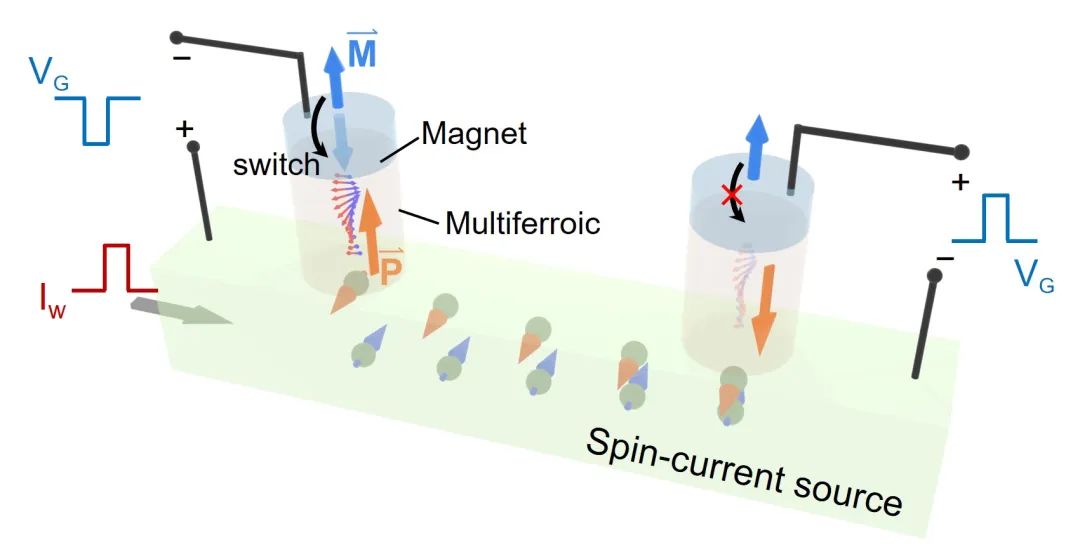

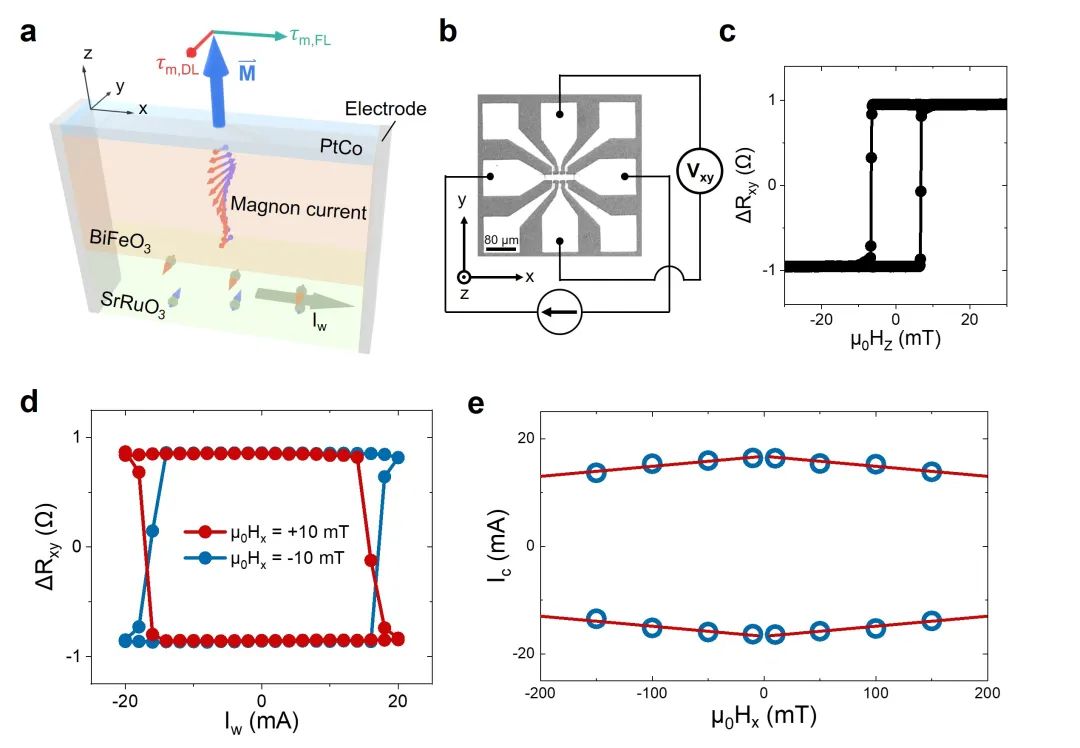

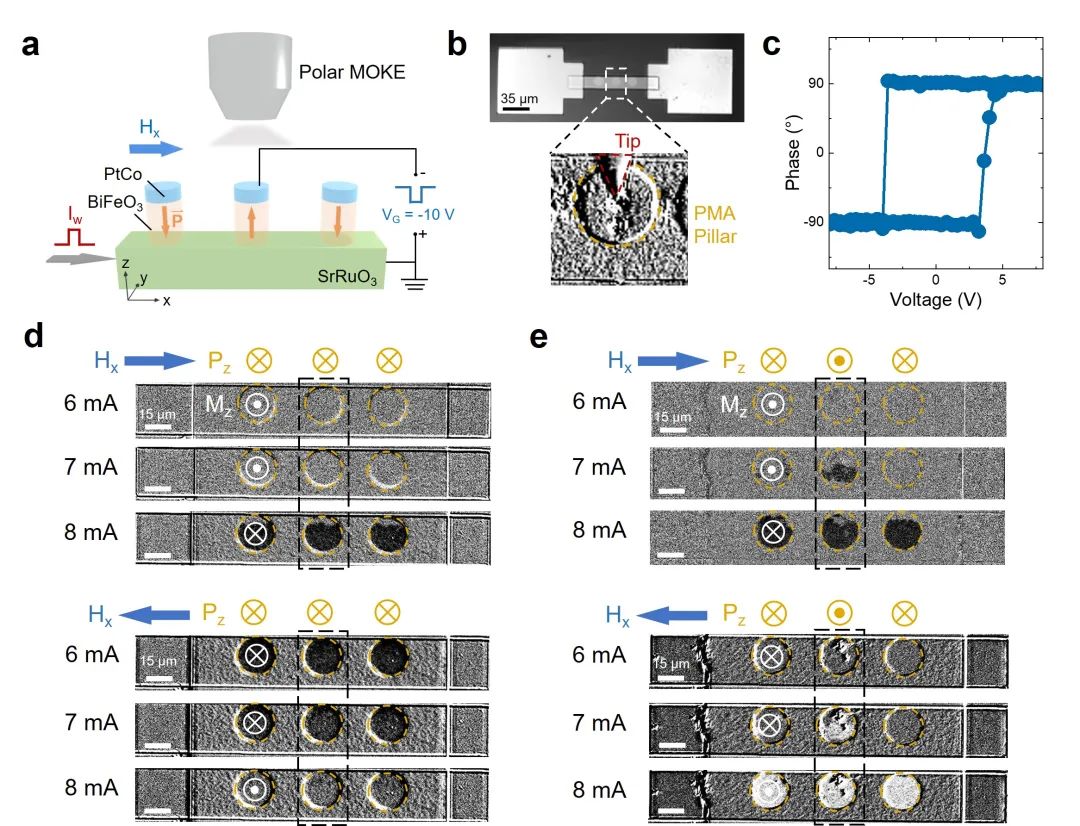

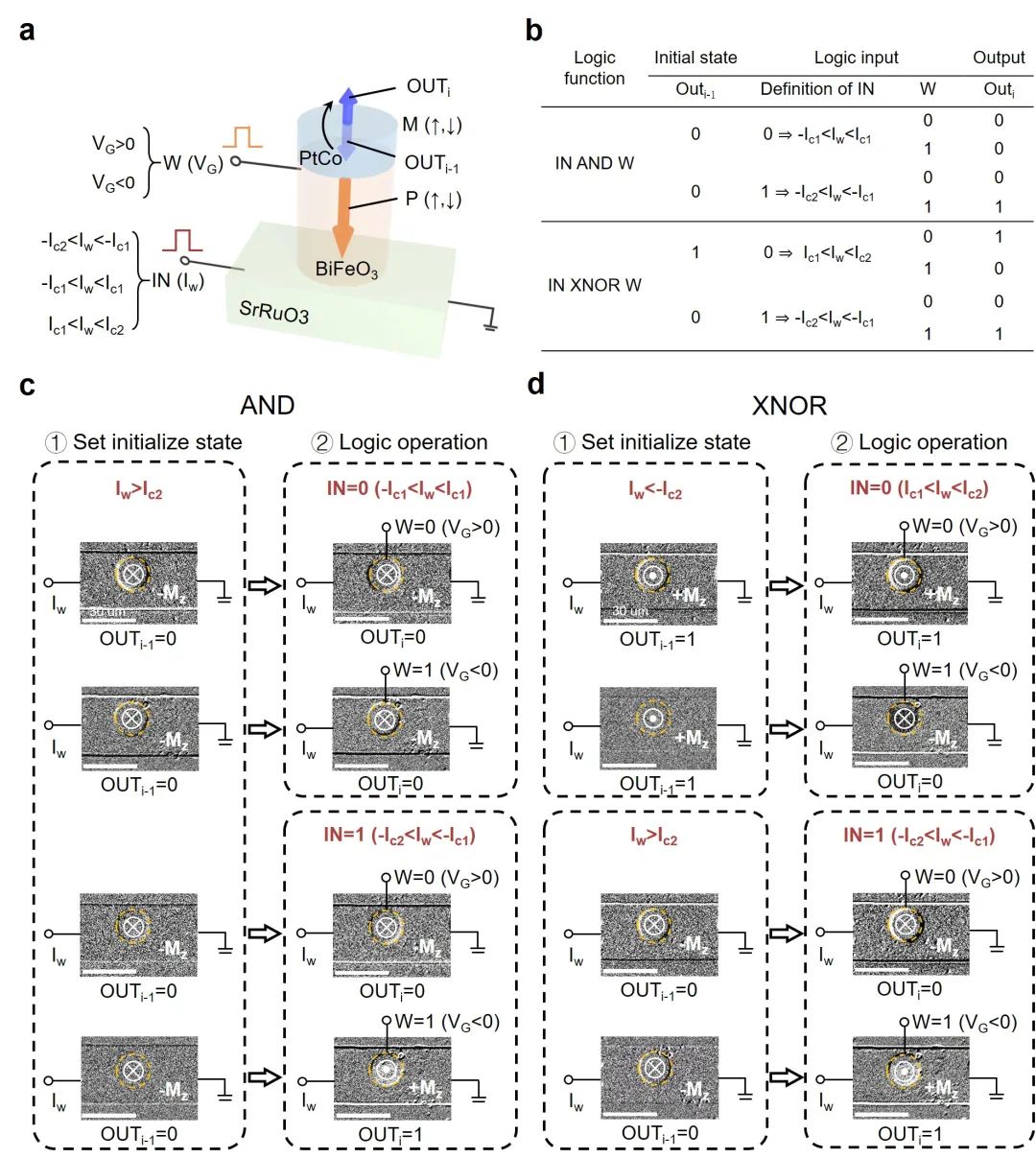

复旦大学周鹏-刘春森团队开发了一种二维超快闪存的规模集成工艺,可实现20纳秒超快编程、10年非易失、十万次循环寿命和多态存储性能,将推动超快颠覆性闪存技术的产业化应用进程。北京大学黄如-杨玉超课题组在忆阻器存算一体通用伊辛机芯片研究中取得新突破,首次实现了能够处理任意伊辛图结构的通用伊辛机,为伊辛机芯片的实用化奠定了重要基础。清华大学南天翔课题组及合作者则提出一种基于磁振子的新型逻辑器件,利用电压原位控制铁酸铋异质结构中的多铁磁振子自旋力矩,从而实现可重构逻辑存储器。人工智能的飞速发展迫切需要高速非易失存储技术。常见的非易失性存储器包括闪存(Flash Memory)、只读存储器(ROM),以及一些新技术如磁性随机存储器(MRAM)、铁电随机存储器(FeRAM)、相变存储器(PCM)等。其中闪存是目前占主导地位的非易失性存储器技术,但在速度方面受到限制。据复旦大学微电子学院官方消息,近日,复旦大学周鹏-刘春森团队《二维超快闪存的规模集成工艺》(“A scalable integration process for ultrafast two-dimensional flash memory”)论文发表于国际顶尖期刊《自然-电子》(Nature Electronics)上,该团队报告了一种可扩展的超快2D闪存集成过程,可用于集成1,024 个闪存设备,产率超过98%。该团队前期研究表明二维半导体结构能够将这一速度提升一千倍以上,实现颠覆性的纳秒级超快存储闪存。这进一步证实了以二维材料生产超快闪存的产业化可能性,将极大地推动超快颠覆性闪存技术的产业化应用进程。然而,如何实现规模集成、走向实际应用极具挑战。而此次研究成果中,该团队开发了超界面工程技术,在规模化二维闪存中实现了具备原子级平整度的异质界面,证实了二维闪存在1Kb存储规模中,纳秒级非易失编程速度下良率高达98%,这一良率已高于国际半导体技术路线图对闪存制造89.5%的良率要求。同时,研究团队研发了不依赖先进光刻设备的自对准工艺,结合原始创新的超快存储叠层电场设计理论,成功研发出沟道长度为8纳米的超快闪存器件,是当前国际最短沟道闪存器件,并突破了硅基闪存物理尺寸极限(约15纳米)。在原子级薄层沟道支持下,这一超小尺寸器件具备20纳秒超快编程、10年非易失、十万次循环寿命和多态存储性能。有望推动超快颠覆性闪存技术产业化。据北京大学集成电路学院官方消息,近日,北京大学黄如-杨玉超课题组《A scalable universal Ising machine based on interaction-centric storage and compute-in-memory》论文发表于国际顶尖期刊《自然-电子》(Nature Electronics),该团队在忆阻器存算一体通用伊辛机芯片研究中取得新突破。该团队与北方集成电路技术创新中心(北京)有限公司合作,基于自主研发的先进忆阻器集成工艺,设计研制了高能效存内伊辛计算芯片,并利用独创的数据映射方法完成了对任意伊辛图的组合优化问题求解。该工作开创了伊辛计算芯片的新范式,在伊辛机的实际应用方面实现了突破。通用伊辛机的运行范式展现出高能效与高可重构性的特点伊辛机是一种用于求解组合优化问题的退火处理器。它通过在芯片中模拟伊辛图所代表的物理模型演化来实现对于组合优化问题的求解。目前大多伊辛机都利用芯片上固定的电路结构代表伊辛图中的自旋节点。现有研究缺乏针对任意伊辛图结构的通用处理技术,这限制了伊辛机进一步应用于更通用的组合优化问题求解。针对上述关键难题,研究团队首次提出了一种基于存内计算、以连接为中心的通用伊辛机。该工作首次实现了能够处理任意伊辛图结构的通用伊辛机。研究团队与北方集成电路技术创新中心合作开发了40nm制程嵌入式忆阻器工艺,并设计研发了基于该工艺的忆阻器芯片。利用该芯片的伊辛机在最大割问题求解中相比于GPU可以达到4.56-7.32倍加速,在图着色问题求解中达到442~1450倍加速,在能效方面相比通用GPU可以实现4.1X105~6.0X105倍提升。此外,近日清华大学集成电路学院南天翔课题组及合作者提出利用电压原位控制铁酸铋异质结构中的多铁磁振子自旋力矩,从而实现可重构逻辑存储器。目前相关研究成果已经以“电压调控多铁磁振子力矩实现可重构逻辑存储器”(Voltage control of multiferroic magnon torque for reconfigurable logic-in-memory)为题,在线发表在《自然-通讯》(Nature Communications)上。内存计算利用能够在同一设备内同时执行信息存储和实现逻辑运算的非易失性存储器,有望在显著降低能耗的同时增强人工智能传输,而这一过程不可避免地会产生焦耳热。近期的研究发现磁振子可以在亚铁磁和反铁磁绝缘体中传输自旋而不涉及电荷运动,在作为信息载体处理和传输信息时不产生明显的热耗散,是开发低耗散自旋逻辑-存储设备的有效途径。非相干磁振子可以在直流电路中被电(或者热)激发,使其与当前的半导体技术兼容。另一方面,在实际应用中,通过施加栅极电压来实现磁振子逻辑运算也十分重要。然而,目前在室温下操纵磁振子流传输的技术主要依赖于通过施加磁场来重新调整磁性序或调节磁畴结构。该研究将多铁性材料与磁振子存储器相结合进行电路设计,利用多铁性材料实现对磁振子力矩的非易失性调控,并提出了一种栅极电压调控可重构磁振子逻辑存储器。该逻辑存储器包括多个位于同一个电流通道上的铁磁/多铁性铁酸铋BiFeO3存储单元。通过在电流通道中施加电流脉冲,可以在多铁性材料中产生非相干磁振子流,并通过磁振子力矩将自旋信息并行地、非易失性地写入多个存储单元。通过原位施加栅极电压脉冲翻转铁电极化,实现了对磁振子自旋传输的非易失性控制。研究团队进一步提出并演示了一种基于多铁性磁振子自旋力矩的可重构逻辑存储器。这赋予了该逻辑存储器在不改变电路拓扑的情况下,可以被重构实现16种布尔代数运算的能力。该器件减少了中间计算参数复制的必要性,显著降低了内存区域开销和功耗,并消除了断电后重新加载数据的需要。这些特点凸显了多铁性磁振子器件在低功耗存内计算方面的潜力。"添加小助手申请进群"

(icspec——规格书查询、免费发ic供应/采购)

[ 新闻来源:芯极速,更多精彩资讯请下载icspec App。如对本稿件有异议,请联系微信客服specltkj]

全部评论