图腾柱功率系数校正电路一直是个构想,许多工程师都在寻找能够有效实现这一构想的技术。如今,人们发现 SiC FET 是能让该拓扑结构发挥最大优势的理想开关。了解应对方式。

这篇博客文章最初由 United Silicon Carbide (UnitedSiC) 发布,该公司于 2021 年 11 月加入 Qorvo 大家庭。UnitedSiC 是一家领先的碳化硅 (SiC) 功率半导体制造商,它的加入促使 Qorvo 将业务扩展到电动汽车 (EV)、工业电源、电路保护、可再生能源和数据中心电源等快速增长的市场。

我们不知道是谁创造了 “无桥图腾柱功率系数校正级” 这个术语,但这肯定诞生于某个奇思妙想、灵感迸发的时刻。在 AC/DC 电源中,该电路可实现功率系数校正,同时因为无需使用交流线路桥式整流器,可在低压线路中有效地提高多达 2% 的效率。下面我们将进一步研究,并将其简称为 “TPPFC”,以精简篇幅。

TPPFC 架构于 2011 年前后首次得到证实,通过使用理想开关和低损耗磁性元件,理论上该电路可达到 100% 的效率。不过这是一个超前想法,因为到目前为止,用于制造高频升压开关的半导体仍然不够理想。问题是要在传导损耗和开关损耗之间进行权衡,为降低导通电阻和传导损耗,我们需要扩大有效晶粒面积,但这会提高器件电容和动态损耗。另一个问题是,TPPFC 必须在中等功率水平以上的 “硬开关” 连续导通模式下运行,以保持峰值电流可控,且这需要恢复开关体二极管中存储的电荷。当使用硅 MOSFET 时,电荷相当大,由此产生的耗散也很高,使得任何小小的净增益对电路来说意义都不大,尤其是还需要考虑开关驱动和控制的成本和复杂性。

使用宽带隙半导体有助于我们实现目标

尽管 2% 的理论效率增益非常具有吸引力,但 “80+Titanium 标准” 等服务器效率标准要求在 230VAC 和 50% 负载下,AC/DC 电源的端对端总损耗仅为 4%。

图 4:Si/SiC 共源共栅

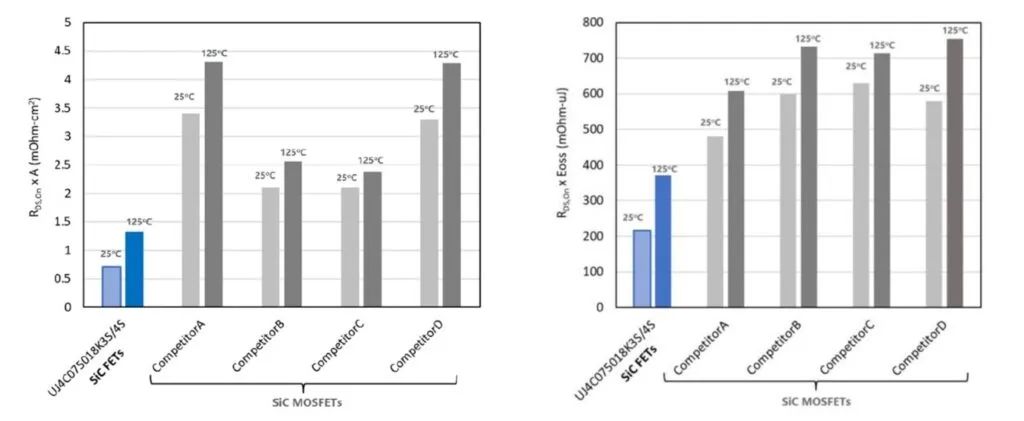

由于通常 2% 要分配给 AC 前端,所以必须使用新技术来重新改进 TPPFC,以提高其性能,而随着宽带隙开关的发展,这一情况发生了改变。碳化硅和氮化镓都是备选的技术,与硅相比,SiC MOSFET 的反向恢复电流降低了 80%,而 GaN 则没有反向恢复电流。此外,它们的输出电容也比硅 MOSFET 更低,因为在相同电压等级下,WBG 晶粒通常比硅晶粒更小。这归功于 WBG 材料具有更高的临界电场,在处理相同峰值电压时所需的电压支撑区域更薄,且掺杂也更高,因此具有更低的导通电阻。SiC 和 GaN 的低损耗优势可归结为品质因数RDS(on)x A 和 RDS(on)x EOSS,前者表示导通电阻与晶粒面积之间的权衡,而后者则表示导通电阻与输出电容导致的开关损耗之间的权衡。

WBG 器件让 TPPFC 级的实现成为可能,相关电路目前已经普及,但也并未十全十美,因为 SiC 和 GaN 的那些显著优势也隐藏着一些实际问题。不可否认,SiC MOSFET 的恢复电荷较低,但体二极管的正向压降却非常高,这样就会增加一些额外损耗。此外,栅极驱动对阈值迟滞和可变性比较敏感,且为实现全面提升所需使用的高电压也非常接近绝对最大值,这非常危险。相反,GaN 器件具有较低的栅极电压阈值,因此在开关瞬变时可能存在杂散和灾难性导通的风险。这可以通过将关断驱动电压设为负值来缓解,但会导致器件在通道增强之前的反向传导过程中,产生非常高的压降,从而增加损耗。并且 GaN 的成本仍相对较高。

不过,我们还有另一种选择,即半导体制造商在数十年前就知道的 “共源共栅” 技术,该技术将高电压开关与低电压开关组合在一起,以实现传导损耗和开关损耗优势。在使用了宽带隙的产品中,将常开 SiC JFET 与低电压硅 MOSFET 相搭配,可得到一个具有非临界栅极驱动、低损耗体二极管以及 WBG 器件所有优势的常闭器件。UnitedSiC 提供的 “SiC FET” 采用这种设计思路,实现了非常快的开关速度,以及小巧的晶粒尺寸,从而实现低电容和低动态损耗。JFET 可以有效地设置传导损耗,即使采用较小尺寸的晶粒,其简单的垂直结构也可以实现较低的导通电阻。下图中的品质因数很好地证明了其优势。图 1显示了750V SiC FET与650V SiC MOSFET 的比较情况。

图 1:在关键品质因数方面,SiC FET 优于 SiC MOSFET

图腾柱 PFC 电路中的 SiC FET 不仅可以获得预期的效率增益,而且还非常易于实施。可以说,拓扑结构和 SiC FET 开关的组合就是 “图腾”,即最佳可实现电路的象征。