关注公众号,点击公众号主页右上角“ · · · ”,设置星标,实时关注功率半导体生态圈最新资讯

关注公众号,点击公众号主页右上角“ · · · ”,设置星标,实时关注功率半导体生态圈最新资讯

来源:盛况, 董泽政, 吴新科. 碳化硅功率器件封装关键技术综述及展望[J]. 中国电机工程学报, 2019, 39(19): 5576-5584.

传统硅基半导体由于自身物理性能不足,逐渐不适应于半导体行业的发展需求,在此背景下第三代半导体应运而生。SiC作为第三代半导体材料具有优越的性能,相比于前两代半导体材料,碳化硅具有禁带宽度大、击穿电场强度高、热导率高、电子饱和速率高以及抗辐射能力强等特点,已成为目前应用最广、市占率最高的第三代半导体材料。碳化硅器件相较于硅基器件,具有优越的电气性能,如耐高压、耐高温和低损耗。随着新能源汽车渗透率不断提升,叠加800V高压平台的逐步实现,SiC器件市场将高速增长。

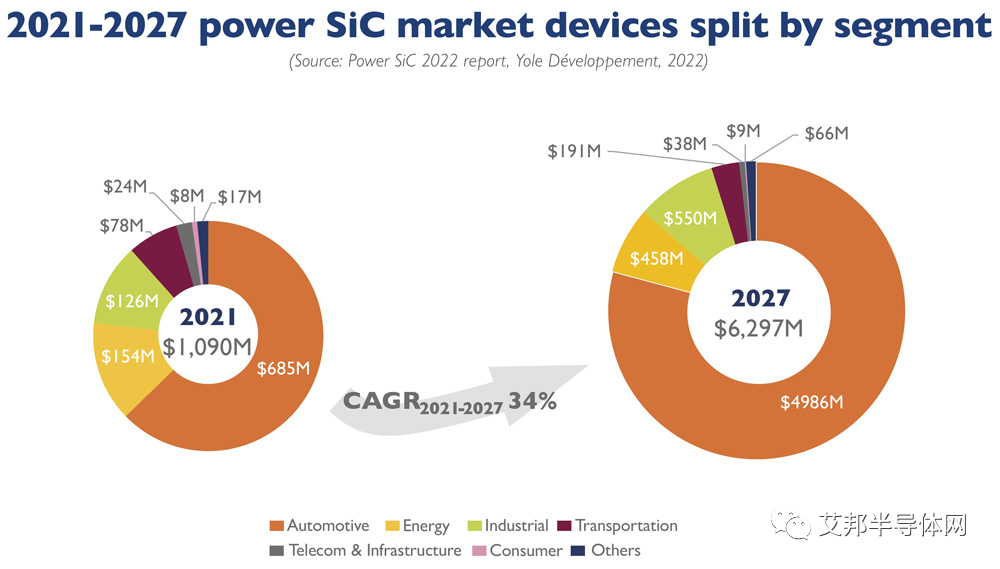

根据Yole数据,2021-2027年,全球SiC功率器件市场规模将由10.9亿美元增长到62.97亿美元,CAGR为34%;其中新能源车用SiC市场规模将由6.85亿美元增长到49.86亿美元,CAGR为39.2%,新能源车(逆变器+OBC+DC/DC转换器)是SiC最大的下游应用,占比由62.8%增长到79.2%,市场份额持续提升。

一、碳化硅功率器件封装技术的挑战

碳化硅器件的这些优良特性,需要通过封装与电路系统实现功率和信号的高效、高可靠连接,才能得到完美展现,如何充分发挥碳化硅器件的这些优势性能则给封装技术带来了新的挑战:

1.降低杂散电感

传统封装杂散电感参数较大,难以匹配器件的快速开关特性。碳化硅器件的结电容更小,栅极电荷低,因此,开关速度极快,开关过程中的 dv/dt 和 di/dt 均极高。虽然器件开关损耗显著降低,但传统封装中杂散电感参数较大,在极高的 di/dt 下会产生更大的电压过冲以及振荡,引起器件电压应力、损耗的增加以及电磁干扰问题。在相同杂散电容情况下,更高的 dv/dt 也会增加共模电流。

2.器件高温工作时,封装可靠性降低

除开关速度更快外,碳化硅器件的工作温度可达到 300℃以上。而现有适用于硅器件的传统封装材料及结构一般工作在 150℃以下,在更高温度时可靠性急剧下降,甚至无法正常运行。解决这一问题的关键在于找出适宜高温工作的连接材料,匹配封装中不同材料的热性能。

3.模块的多功能集成封装与高功率密度需求

多功能集成封装技术以及先进的散热技术在提升功率密度等方面起着关键作用。

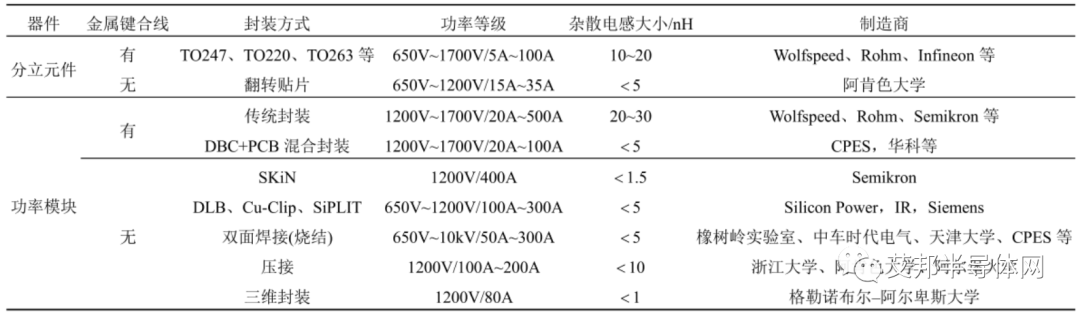

二、碳化硅功率器件的封装技术

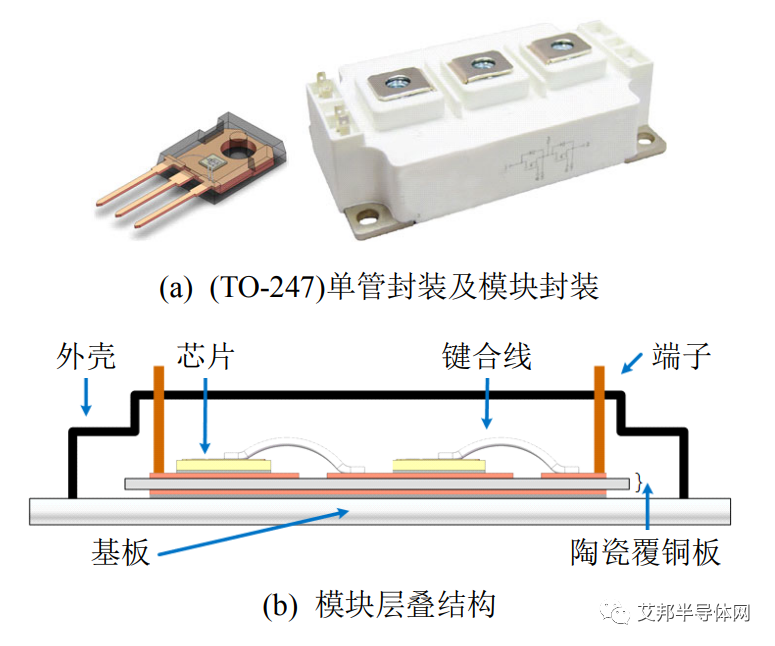

目前已有的大部分商用 SiC 器件仍采用传统 Si 器件的封装方式,首先通过焊锡将芯片背部焊接在基板上,再通过金属键合线引出正面电极,最后进行塑封或者灌胶。传统封装技术成熟,成本低,而且可兼容和替代原有 Si 基器件。

图1传统封装技术

传统封装结构导致其杂散电感参数较大,在碳化硅器件快速开关过程中造成严重电压过冲,也导致损耗增加及电磁干扰等问题。而杂散电感的大小与开关换流回路的面积相关。其中,金属键合连接方式、元件引脚和多个芯片的平面布局是造成传统封装换流回路面积较大的关键影响因素。

为充分发挥 SiC 器件的优势,提高功率密度,消除金属键合线连接是一种趋势。通过采用各种新型结构,降低模块回路寄生电感值,减小体积是推进电力电子走向高频、高效、高功率密度的保证。

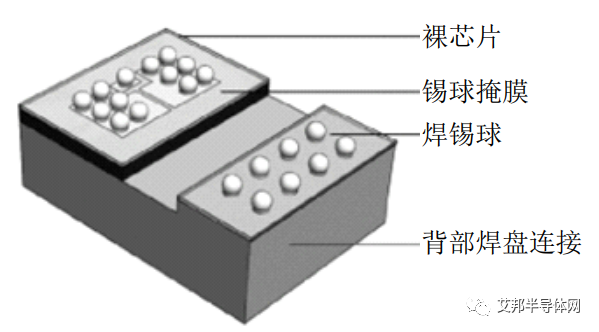

1.单管翻转贴片封装

阿肯色大学团队借鉴 BGA 的封装技术,提出了一种单管的翻转贴片封装技术,如图 2 所示。该封装通过一个金属连接件将芯片背部电极翻转到和正面电极相同平面位置,然后在相应电极位置上植上焊锡球,消除了金属键合线和引脚端子。相比于 TO-247 封装,体积减小了 14 倍,导通电阻减小了 24%。

图2单管贴片封装

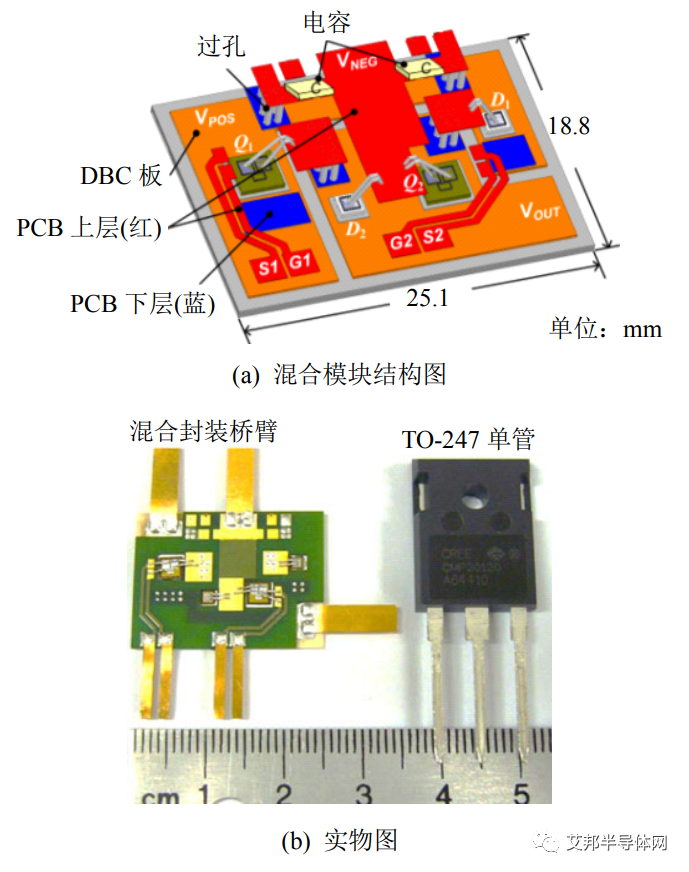

2.DBC+PCB混合封装

传统模块封装使用的敷铜陶瓷板(direct bonded copper-DBC)限定了芯片只能在二维平面上布局,电流回路面积大,杂散电感参数大。CPES、华中科技大学等团队将 DBC 工艺和 PCB 板相结合,利用金属键合线将芯片上表面的连接到 PCB 板,控制换流回路在 PCB 层间,大大减小了电流回路面积,进而减小杂散电感参数,可将杂散电感可控制在 5nH 以下,体积相比于传统模块下降 40%。

图3DBC+PCB混合封装

柔性 PCB 板结合烧结银工艺的封装方式也被用于商业模块中。如图 4 所示为 Semikron 公司利用 SKiN 封装技术制作的 1200V/400A 的 SiC 模块。该混合封装方式结合了 2 种成熟工艺的优势,易于制作,可实现低杂散电感以及更小的体积。但 PCB 板的存在限制了上述封装方式高温运行的可靠性。

图4Semikron公司的SKiN封装

3.芯片正面平面互连封装

除采用柔性 PCB 板取代金属键合线外,还可使用平面互连的连接方式来实现芯片正面的连接。图 5 为 Silicon Power 公司采用端子直连(direct lead bonding,DLB)的焊接方法,类似的还有 IR 的 Cu-Clip IGBT,Siemens 的 SiPLIT 技术等。平面直连的封装工艺通过消除金属键合线,将电流回路从 DBC 板平面布局拓展到芯片上下平面的层间布局,显著减小了回路面积,可实现低杂散电感参数,还拥有更出色的温度循环特性以及可靠性。

图5DLB互连技术

用于 SiC 芯片的埋入式封装也可认为是一种芯片正面的平面直连封装。如图 6 所示,该方法将芯片置于陶瓷定位槽中,再用绝缘介质填充缝隙,最后覆盖掩膜两面溅射金属铜,实现电极连接。通过选择合理的封装材料,减小了模块在高温时的层间热应力,并能在 279℃的高温下测量模块的正反向特性。

图6埋入式封装

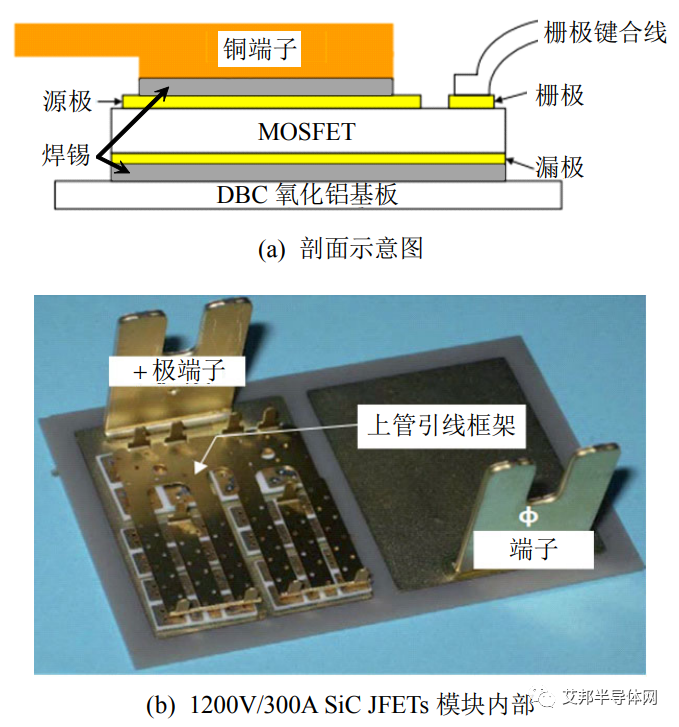

4.双面散热封装技术

双面封装工艺由于可以双面散热、体积小,较多用于电动汽车内部 IGBT 的封装应用。图 7 为一典型的双面散热封装 SiC 模块,该模块上下表面均采用 DBC 板进行焊接,所以可实现上下表面同时散热。

图7SiC双面散热封装模块

该工艺的难点在于,芯片上表面需要进行溅射或电镀处理使其可焊接,并且在芯片上表面增加金属垫片、连接柱等来消除同一模块中不同高度芯片的高度差。再加上 SiC 芯片普遍面积小,如何保证在上表面有限面积范围内的焊接质量是该工艺过程中的关键。得益于上下 DBC 的对称布线与合理的芯片布局,该封装可将回路寄生电感参数降到 3nH 以下,模块热阻相比于传统封装下降 38%。国内如株洲中车时代电气、天津大学等团队都对此类双面封装模块进行了热、电气、可靠性等多方面的研究

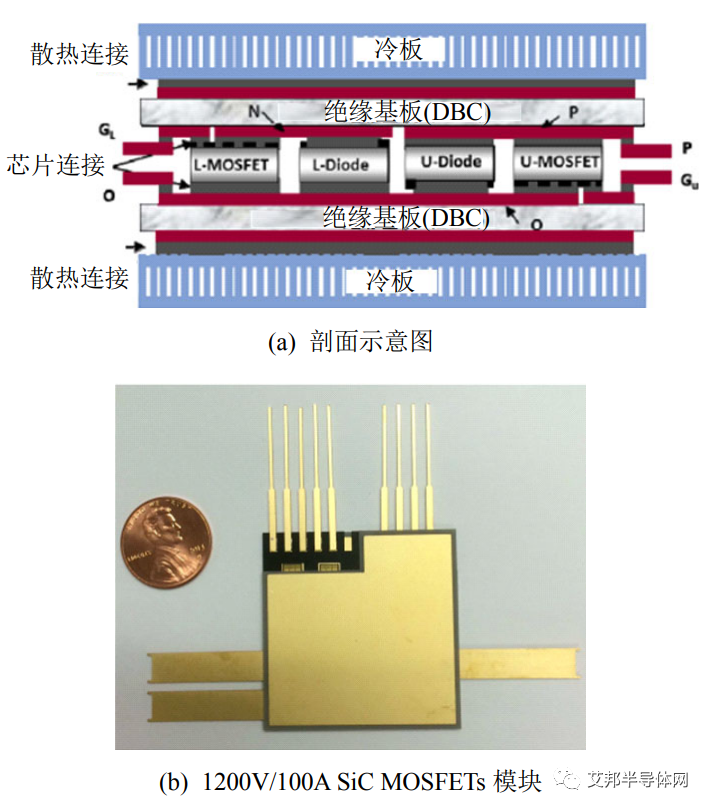

图810kV/54ASiCMOSFET模块

CPES 针对 10kV 的 SiC MOSFET 采用了如图 8 所示的封装设计。使用银烧结技术将芯片和敷铝陶瓷板(direct bonded aluminum,DBA)、钼片相连接。其中芯片下部采用两层 DBA 板叠加,并将中间层连接到母线中间电压,一方面可以减小板子边缘的场强,另一方面减小了桥臂中点对地的寄生电容,降低 EMI。该模块可以采用双面散热,也可将瓷片电容焊接在芯片上部 DBA 板上,减小回路寄生电感到小于 5nH。

图9SiCMOSFET压接模块

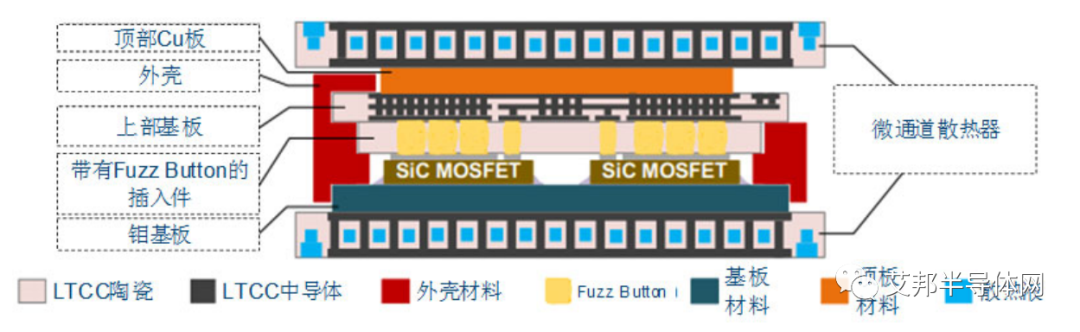

图 9 为浙江大学和阿肯色大学合作提出的一种用于 SiC MOSFET 的双面压接模块。该模块使用低温共烧陶瓷(LTCC)工艺和带有弹性的 Fuzz Button 取代传统 DBC 板和金属键合线实现芯片互联以及散热设计,回路寄生电感参数仅为 4.3nH。不足之处在于 LTCC 导热系数低,而且压接模块的特性对外部压力反应敏感。

5.三维(3D)封装技术

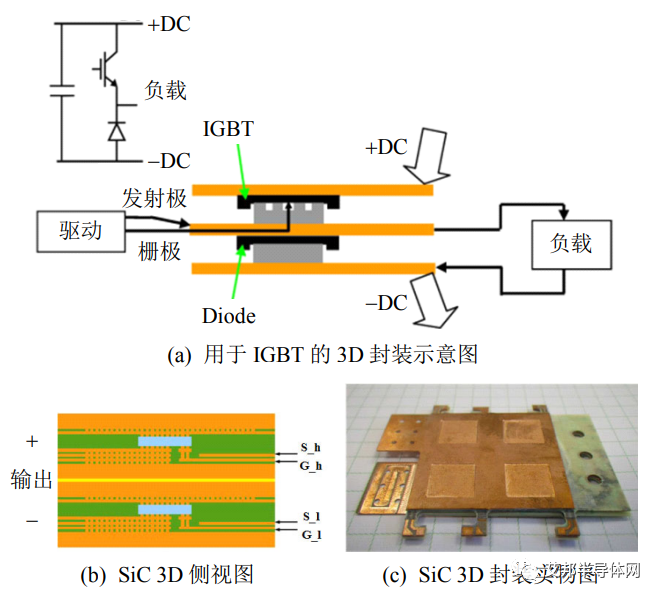

三维封装技术利用了 SiC 功率器件垂直型的结构特点,将开关桥臂的下管直接叠在上管之上,消除了桥臂中点的多余布线,可将回路寄生电感降至 1nH 以下。Vagnon 于 2008 年即提出了利用金属片直连的模块单元,如图 10(a)所示,并基于此封装制作了 Buck 变换器模块。实验测试表明,该 3D 封装模块基本消除了共源极电感,而且辐射电磁场相比于传统模块大大减小,共模电流也得到了很好的抑制。

图103D封装技术

另有研究将 SiC MOSFET 芯片嵌入 PCB 内部,形成如图 10(b)所示的 3D 封装形式。芯片表面首先经过镀铜处理,再借由过孔沉铜工艺将芯片电极引出,最后使用 PCB 层压完成多层结构,图 10(c)为实物模块。得益于 PCB 的母排结构,模块回路电感仅有0.25nH,并可同时实现门极的开尔文连接方式。该封装的功率密度极高,如何保证芯片温度控制是一大难点,外层铜厚和表面热对流系数对芯片散热影响很大。除功率芯片之外,无源元件如磁芯,电容等均可通过适当的方式嵌入 PCB 当中以提高功率密度。

4.高温封装技术

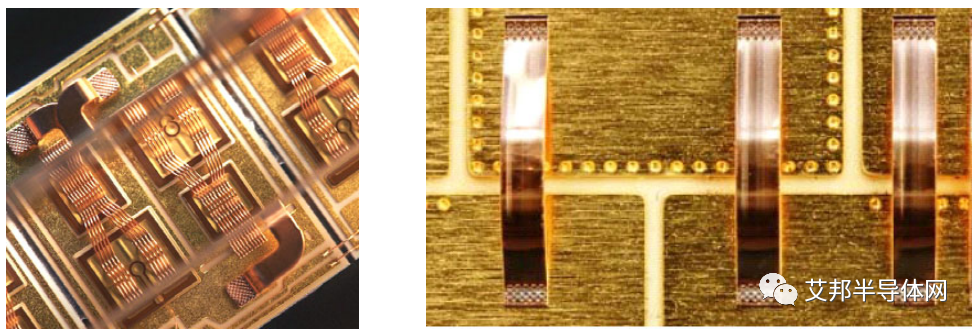

1)铜带连接工艺

在进行芯片正面连接时可用铜线替代铝线,消除了键合线与 DBC 铜层之间的热膨胀系数差异,极大地提高模块工作的可靠性。此外,铝带、铜带连接工艺因其更大的截流能力、更好的功率循环以及散热能力,也有望为碳化硅提供更佳的解决方案。图 11 所示分别为铜键合线、铜带连接方式。

图11铜线(左)及铜带(右)连接工艺

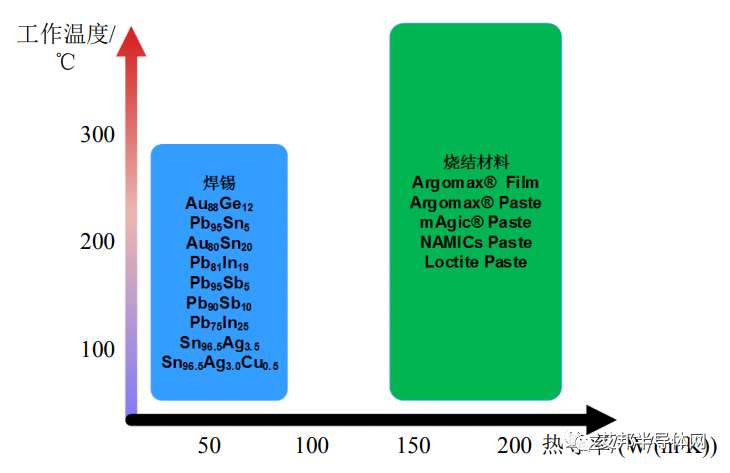

2)烧结银连接技术

烧结银连接技术凭借其极高的热导率(~200W/(m·K)),低烧结温度,高熔点等优势,有望取代焊锡成为 SiC 器件的新型连接方法。银烧结工艺通常是将银粉与有机溶剂混合成银焊膏,再印刷到基板上,通过预热除去有机溶剂,然后加压烧结实现芯片和基板的连接。图 12 给出了一些典型的焊锡和烧结材料的热导率和工作温度对比图。

图12典型焊锡及烧结材料对比图

3)高导热、高可靠封装材料

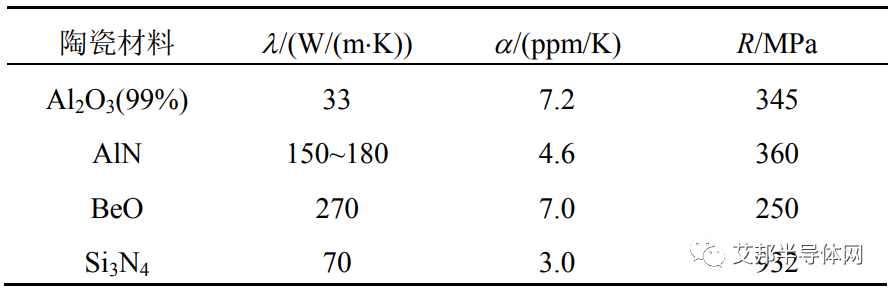

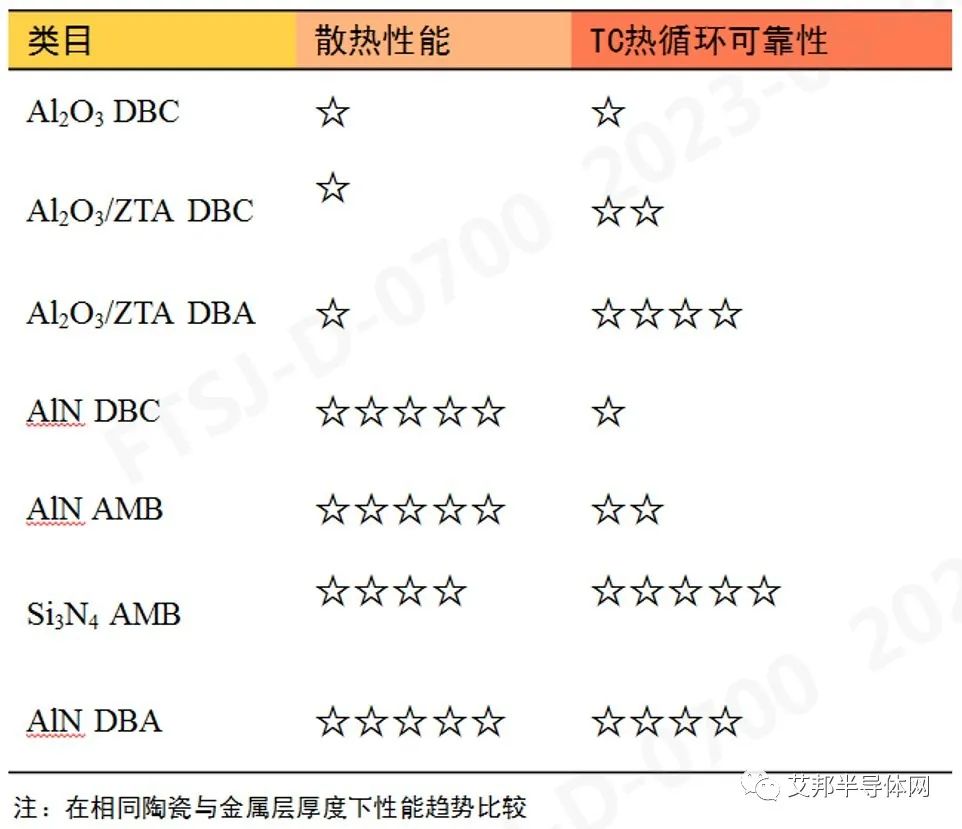

导热系数高、线性膨胀系数和碳化硅材料(3.7ppm/K)相近的材料是提高封装可靠性和关键所在。氮化铝(AlN)导热系数高,热膨胀系数接近 SiC,成本合适,是目前较为理想的碳化硅器件的基板材料。氮化硅(Si3N4)热膨胀系数最接近 SiC,而且抗弯强度大,在热循环中更不容易断裂,也是一种适合碳化硅器件高温工作的绝缘材料。

为提高陶瓷基板覆铜层的可靠性,直接敷铝陶瓷基板(Direct Bonded Aluminum,DBA)以及活性金属钎焊(Active Metal Brazing;AMB)等工艺也受到人们越来越多的关注。

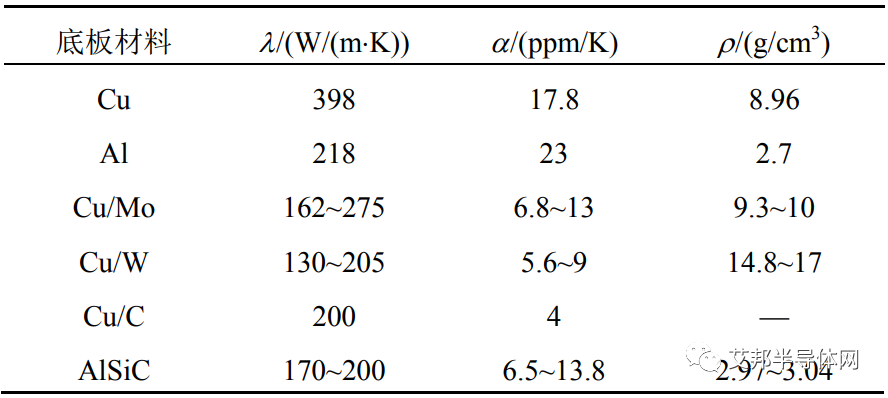

Cu 作为底板材料热导率最高,但其与基板之间热膨胀系数相差较大。Al 作为底板,成本低,还可显著降低整体重量,但在热导率和热膨胀系数匹配方面均表现较差。Cu 基合金如 Cu/Mo,Cu/W,Cu/C 等在热导率和热膨胀系数方面性能均较为优越,但其密度和成本均较高。AlSiC 的成本、密度、热膨胀系数均十分理想,但缺点在于热导率较低。具体使用情况需要结合实际情况综合决定。

5.多功能集成封装技术

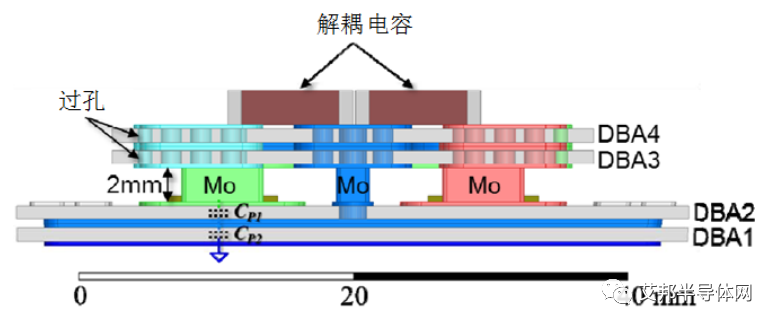

1)多功能集成封装技术

碳化硅器件的出现推动了电力电子朝着小型化的方向发展,其中集成化的趋势也日渐明显。瓷片电容的集成较为常见,但目前瓷片电容不耐高温,所以并不适宜于碳化硅的高温工作情况。

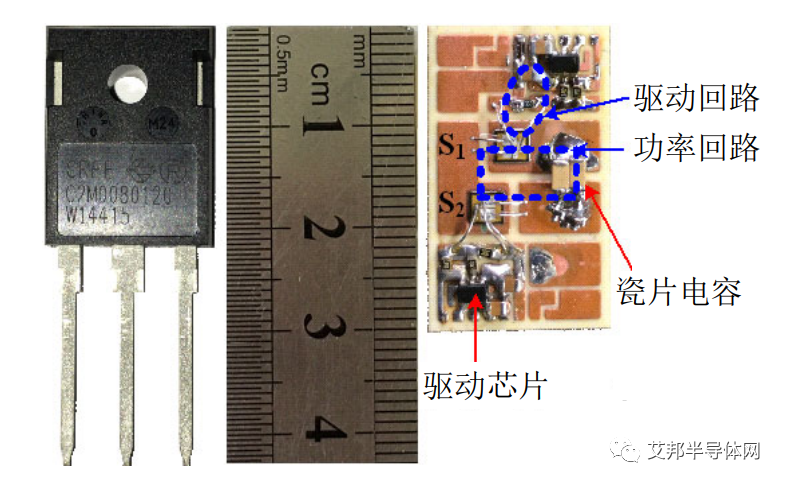

图13 集成母线瓷片电容和驱动的SiC半桥模块

驱动集成技术也逐渐引起了人们的重视,三菱、英飞凌等公司均提出了 SiC 智能功率模块(intelligent power module,IPM),将驱动芯片以及相关保护电路集成到模块内部,并用于家电等设备当中。如图 13 所示,浙江大学团队通过将瓷片电容、驱动芯片和 1200V SiC 功率芯片集成在同一块 DBC 板上,使半桥模块面积仅为 TO-247 单管大小,极大地减小了驱动回路和功率回路的寄生电感参数。

此外,还有 EMI 滤波器集成,温度、电流传感器集成、微通道散热集成等均有运用到碳化硅封装设计当中。

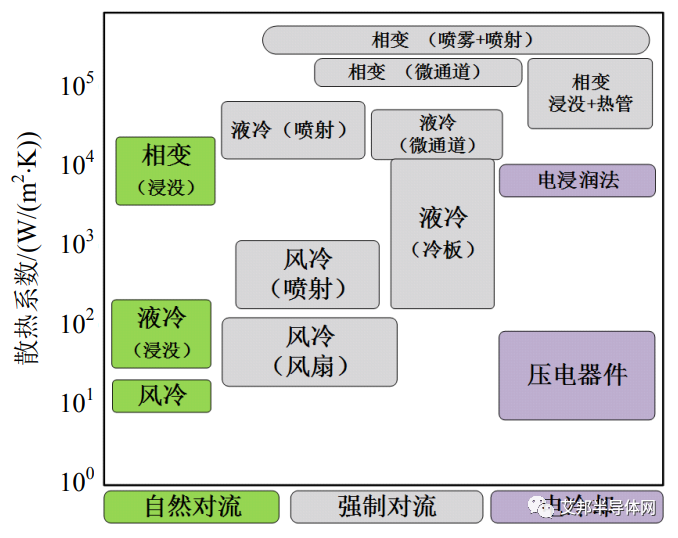

2)散热技术

散热技术也是电力电子系统设计的一大重点和难点。设计中,通常是将单管或模块贴在散热器上,再通过风冷或者液冷进行散热。微通道散热技术也被用于芯片的直接散热,这种直接作用于芯片的散热技术消除了模块多层结构的限制,可以极大提高芯片的散热效率。相变散热技术如热管、喷雾等方式相比于单相气冷、水冷等具有更高的热导率,非常高效,也为 SiC 器件的散热提供了一种解决思路。

图14不同散热技术之间的对比

【免责声明】文章为作者独立观点,不代表功率半导体生态圈。如因作品内容、版权等存在问题,请于本文刊发30日内联系功率半导体生态圈进行删除或洽谈版权使用事宜。