长江存储(YMTC)自2016年成立以来一直是头条新闻。

作为中国领先的NAND存储器集成器件制造商(IDM),YMTC发展迅速。在2018年的闪存峰会(FMS)上首次推出了Xtacking 1.0架构,随后于2019年推出了Xstacking 2.0。

正如许多科技公司一样,2022年对长江存储(YMTC)来说是做了一年过山车。首先是苹果计划将YMTC的128L芯片纳入其产品的广泛消息,然后是美国政府对YMTC实施限制后的迅速转变。与此同时,YMTC发布了新闻稿,称Xtacking 3.0现已上市,这引发了人们对该公司是否仍能在没有苹果继续支持的情况下大规模生产该设备的质疑。

TechInsights将Xtacking 3.0视为2022年最具颠覆性的技术之一。首先,创新架构在新兴的存储器半导体行业中并没有真正竞争者;其次,最近对YMTC实施的限制使这项技术成为地缘政治的焦点。

本周,TechInsights团队收到了TiPlus7100的几个单元,这是第一个应该使用Xtacking 3.0的设备。我们对我们的发现感到惊讶。

01

TechInsights发现了什么?

根据YMTC关于Xtacking 3.0的新闻稿,该技术可以在TiPlus7100高速SSD的每个版本中找到。TechInsights购买了512GB和1TB;2TB还不能购买。

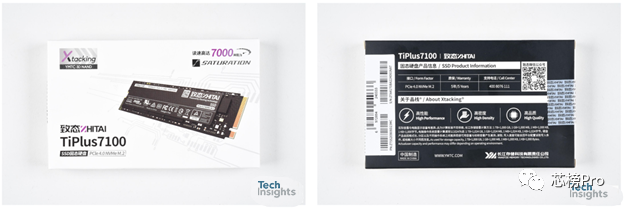

图1:致态TiPlus7100 1 TB SSD

TechInsights尚未在我们拆除的TiPlus7100的任何型号中发现Xtacking 3.0。到目前为止,TechInsights已经评估过:

是128L(图5),而不是232L 包括2x2平面的模具布局(图4),而不是YMTC描述的3x2平面 不包括Xtacking 3.0功能,如背面源极连接(BSSC)或中央X解码器。

TiPlus7100 1 TB SSD中有两个512 GB NAND包(图2)。印刷电路板(PCB)中有两个备用插槽。

图2.PCB图像

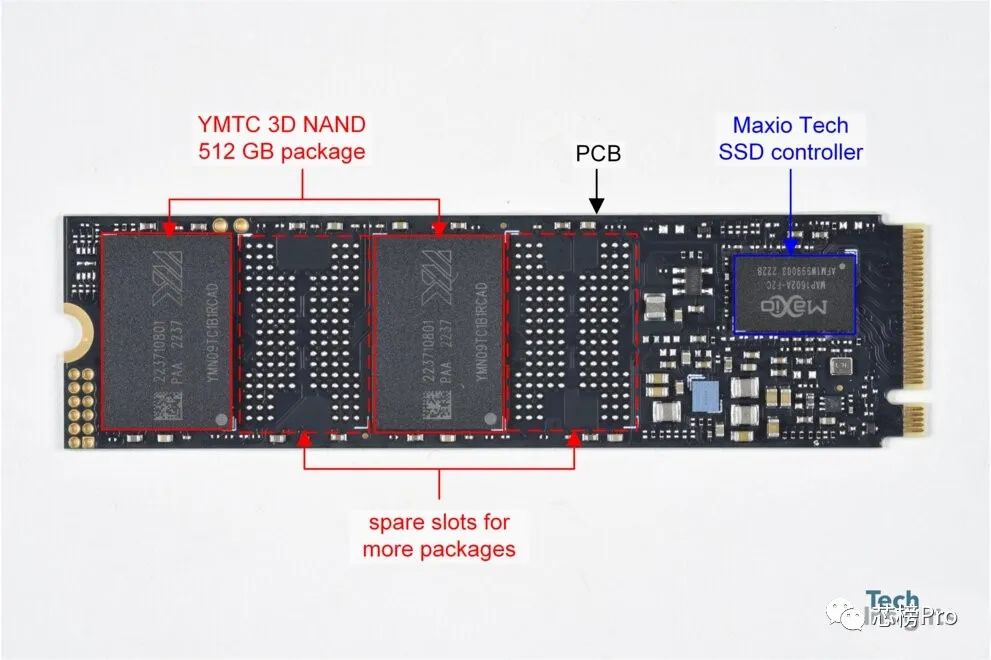

132引脚球栅阵列(BGA)多芯片封装(MCP)的尺寸为18.0 mm×12.0 mm×0.9 mm(图3)。2022年第37周的包装日期代码表明,包装在9月份完成(在2022年闪存峰会上Xtacking 3.0首次亮相后不久)。

图3.YMTC NAND包图像

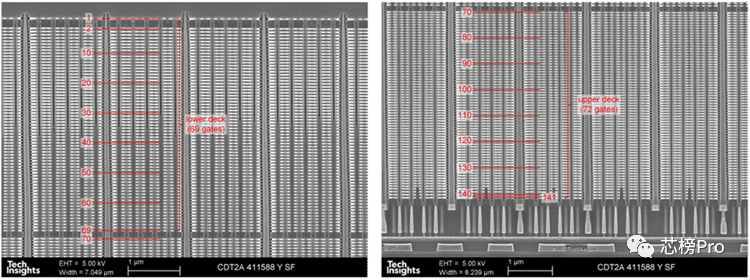

每个NAND封装内有八个NAND管芯(CDT2A的管芯标记)。CDT2A管芯具有2×2平面的布局(图4)。这与具有1x4平面的先前YMTC 128L管芯布局[2]不同。TechInsights的分析显示,新的YMTC CDT2A管芯实际上是YMTC 128层3D NAND,总栅极数为141(图5)。

图4.CDT2A管芯图像

图5.存储器阵列、下部(左)和上部(右)的横截面SEM图像

一些新闻来源猜测,随着苹果的退出,YMTC可能没有资金大量生产Xtacking 3.0。这可能是因为TechInsights在我们的零件搜索中运气不够好,无法确保为数不多的真正的Xtacking 3.0。

TechInsights的分析仍在继续——我们仍在深入研究512GB和1TB。看起来,这些包可能包括Xtacking 2.0和3.0的混合。我们的采购工作仍在继续。如果有Xtacking 3.0,TechInsights会找到它。

02

技术发展路径

Xtacking3.0中有什么?

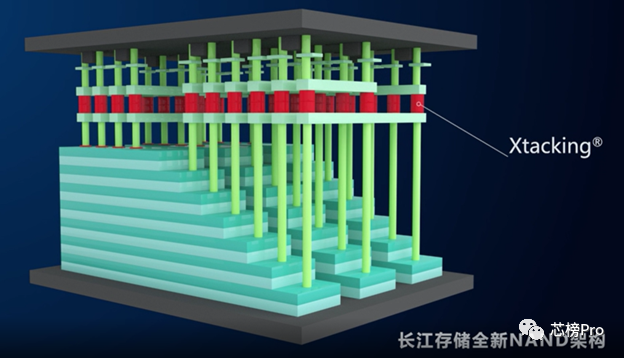

Xtacking是YMTC的注册商标,其创新的3D NAND架构涉及CMOS晶片和存储单元晶片的晶片接合,如图6所示。

图6.来源:YMTC

从Xtacking 1.0到Xtacking3.0中的主要演变点可以总结如下:

Xtacking 1.0使用晶片对晶片结合,以提高电池效率并缩短开发时间。

Xtacking 2.0实现硅化镍(NiSi)而不是硅化钨(WSi),以提高CMOS晶片的器件性能和I/O速度

Xtacking 3.0为存储单元晶片引入了背面源极连接(BSSC),这导致了更简单的工艺和更低的成本

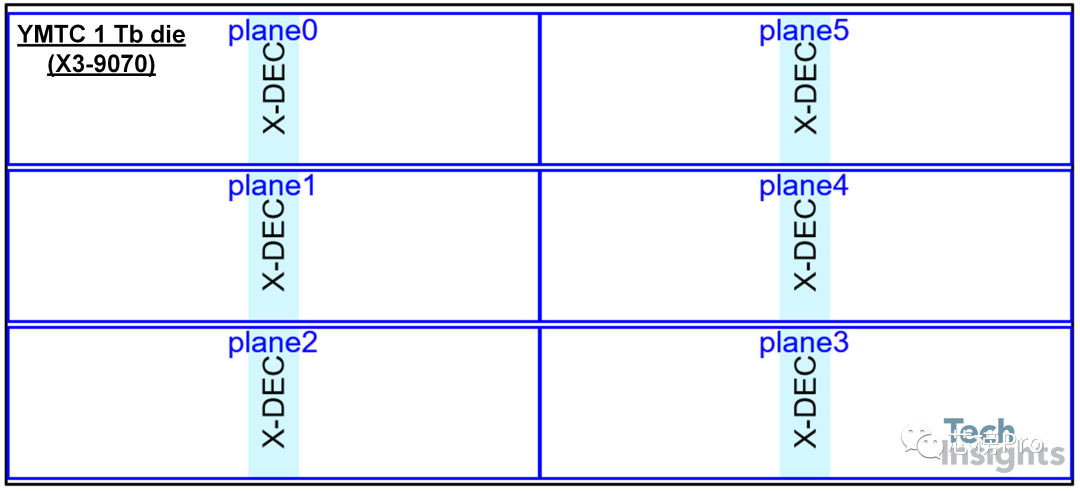

在FMS 2022上,YMTC谈到了1Tb管芯X3-9070(如图7所示),该芯片具有六个平面,每个平面具有异步多平面独立(AMPI)操作,每个平面带有中心X解码器(X-DEC);Xtacking 3.0将允许速度提高50%。

图7.YMTC在FMS 2022上讨论的YMTC 1 Tb 芯片(X3-9070)的表示

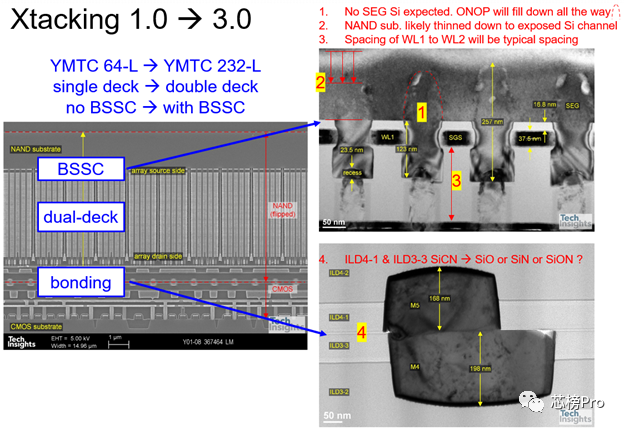

通过BSSC实施,YMTC可能消除了具有挑战性的ONO蚀刻(在Si沟道沉积之前)和昂贵的选择性外延生长(SEG)Si。图8显示了YMTC 64-L(采用Xtacking 1.0)和YMTC 232-L(使用Xtacking3.0)之间的预期变化。随着Adeia(以前的Xperi)将其混合键合技术许可给YMTC,键合界面也可能发生材料变化。

众所周知,Xtacking 3.0将在232L管芯中找到。232L堆叠WL结构的大寄生电容导致性能下降。为了对抗这种退化,与边缘XDEC相比,中心XDEC设计将WL电容减半,并减少RC负载和RC延迟(tRC)。中心XDEC设计可以减少WL稳定时间和对WL充电所需的电流。通过采用中心XDEC,与之前的边缘XDEC相比,性能可以提高15~20%。出于这些原因,TechInsights确信中心XDEC将成为3D NAND管芯设计的主流。

图8.显示Xtacking 1.0(64-L)功能的图像,并附有注释,说明从Xtacking1.0到Xtackng 3.0(232-L)的预期变化

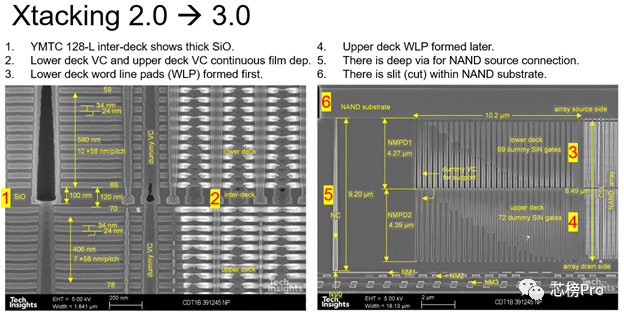

Xtacking 3.0的其他与内存相关的功能/过程预计与YMTC 128-L(Xtacking2.0)中的功能/流程类似,如图9所示。

图9.显示Xtacking 2.0(128-L)功能的图像,并注明了从Xtacking2.0到Xtackding3.0(232-L)不可能发生变化的地方