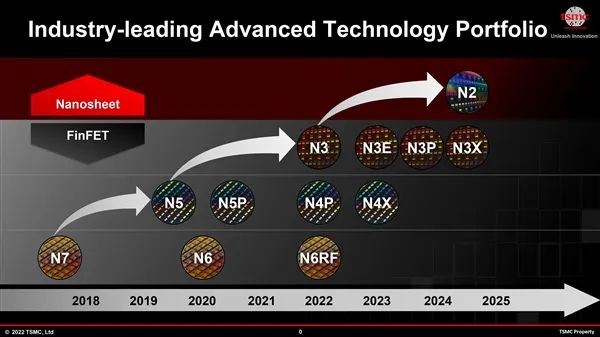

台积电在今日举办的2022技术论坛上,首度推出下一代先进制程N2,也就是2nm。

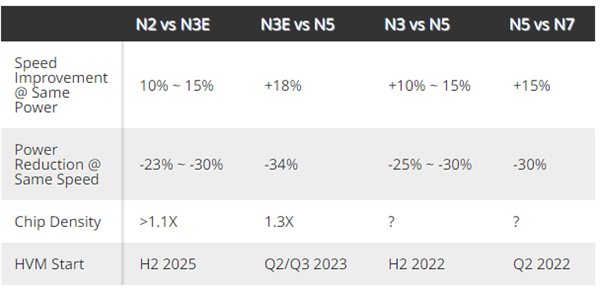

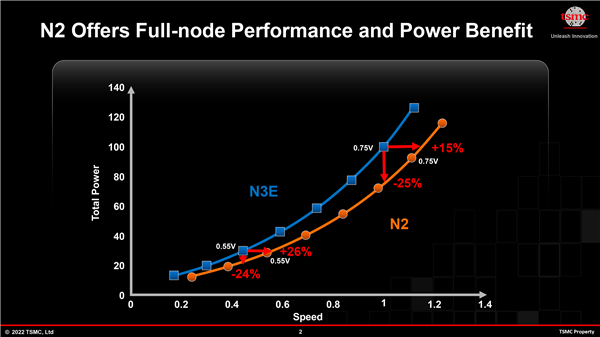

技术指标方面,台积电披露,N2相较于N3,在相同功耗下,速度快10~15%;相同速度下,功耗降低25~30%,开启高效能新纪元。

就纵向对比来看,2nm之于3nm的提升,似乎不如3nm之于5nm,包括但不限于性能、功耗、密度等所有核心参数。

按照摩尔定律来看的话,新一代工艺的密度提升是100%才行,实际中也能达到70-80%以上才能算新一代工艺。

台积电没有解释为何2nm的密度提升如此低,很有可能跟使用的纳米片电晶体管(Nanosheet)技术有关,毕竟这是新一代晶体管结构,考验很多。它取代的是华人教授胡正明发明的FinFET(鳍式场效应晶体管),外界普遍认为,纳米片电晶体就是台积电版的GAAFET(环绕栅极晶体管)。

密度提升只有10%的话,对苹果及、AMD、高通、NVIDIA等客户来说,这是不利于芯片提升的,要么就只能将芯片面积做大,这无疑会增加成本。

台积电还表示,N2不仅有面向移动处理器的标准工艺,还会有针对高性能运算和小芯片(Chiplet)的整合方案。

时间节奏方面,N2将于2025年量产。这意味着芯片出货都要2026年了,4年后才能看到,工艺升级的时间也要比之前的5nm、3nm更长。

有观点认为,台积电在2nm工艺上的挤牙膏,倒是给了Intel一个机会,因为后者预计在2024年就要量产20A工艺及改进版的18A工艺了,同样也是“2nm”级别的。

目前两家的2nm工艺都是PPT上的,但是台积电这次的2nm工艺表现不尽如人意,这让Intel励志重回半导体工艺第一的目标有了可能。

接着看看3nm。

台积电今天不仅公布了Nanosheet碳纳米片技术的开山之作N2 2nm工艺,还展示了FinFET鳍式晶体管的终结之作N3 3nm工艺,发展出了多达五种不同版本,也是历代工艺中最丰富的。

N3

最早也是最标准的3nm,今年下半年投入量产,预计明年初可以看到产品上市。

它面向有超强投资能力、追求新工艺的早期客户,比如苹果、AMD这种,但是应用范围较窄,只适合制造特定的产品。

对比N5,功耗可降低约25-30%,性能可提升10-15%,晶体管密度提升约70%。

Ehanced增强版,近期就会风险性试产,明年年中规模量产,产品上市预计2023年底或2024年初。

它在N3的基础上提升性能、降低功耗、扩大应用范围,对比N5同等性能和密度下功耗降低34%、同等功耗和密度下性能提升18%,或者可以将晶体管密度提升60%——是的,它的密度反而低于N3。

台积电还称,N3E可以达到比N4X更高的频率,后者明年投产。

N3P

Performance性能增强版,细节不详。

N3S

密度增强版,细节不详。

N3X

超高性能版,不在乎功耗和成本,也是N4X的继承者。

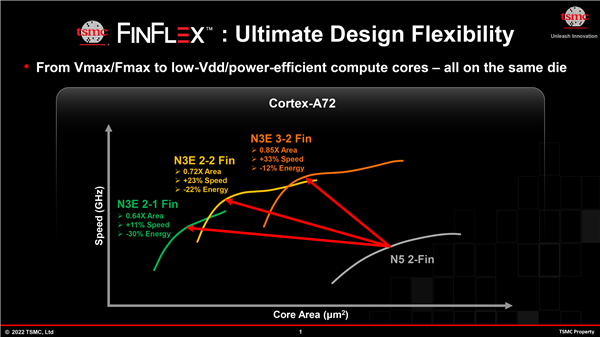

值得一提的是,N3E工艺还可以根据客户需求定制栅极、鳍片数量,性能、功耗、面积指标也不一样,官方称之为“FinFlex”。

比如2个栅极1个鳍片,可以性能提升11%、功耗降低30%、面积缩小36%。

2个栅极2个鳍片,可以性能提升23%、功耗降低22%、面积缩小28%。

3个栅极2个鳍片,可以性能提升33%,功耗降低12%,面积缩小15%。

长按图片,扫码免费领取