随着晶体管先进工艺节点持续推进,国际半导体产业界已明确2 nm以后晶体管技术将转向纳米片晶体管技术,包括多桥通道晶体管(Multi-Bridge Channel FET)和垂直互补晶体管(Complementary FET),来更好地提升静电控制能力。然而基于传统硅锗材料的多桥沟道制造工艺依赖横向选择性刻蚀和重复外延生长,制造工艺日益复杂。此外,体硅材料制作沟道在厚度小于3 nm时,由于界面缺陷的存在迁移率会大幅退化,所以硅基多桥沟道结构也仍然面临漏电流的问题。

所以,半导体业界亟需一种既能原子尺度薄又能保持良好载流子传输能力的新沟道材料,而具有半导体性质的二维原子晶体(二维半导体)的出现提供了解决这些问题的可能选择。因为二维半导体具有天然的原子级厚度的纳米片结构,和碳纳米管、石墨烯一样,具有光滑无悬挂键的表面,可以很好的延续摩尔定律的晶体管微缩趋势;而且二维材料种类丰富、能够任意堆叠的特点,可以用于灵活的器件结构和能带设计。所以,TSMC、Intel、IMEC等领先的半导体公司近年来正在积极引入二维材料,作为未来1 nm以下节点的重要技术储备。

鉴于此,复旦大学微电子学院和北京大学物理学院的课题组紧密合作,基于晶圆级二维半导体薄膜,成功制备了MBC-FET和C-FET原型器件阵列。首先,使用晶圆级的N型MoS2薄膜作为沟道,并通过转移叠层和层间互连工艺实现两层的MBC-FET器件;其次通过在基底上直接生长的P型MoTe2薄膜,通过叠层转移N型MoS2和层间互连,实现垂直C-FET器件。该成果为二维半导体材料在未来MBC-FET和C-FET先进工艺节点中的实际应用提供了规模化制造的验证下结果。夏银、宗凌逸、潘宇为共同第一作者,复旦大学包文中研究员和周鹏教授、北京大学叶堉教授为共同通讯作者。该工作同时还与华东理工大学,深圳六碳科技等单位紧密合作,并得到了科技部重点研发计划纳米科技专项、上海市科委集成电路科技支撑专项等项目的支持。

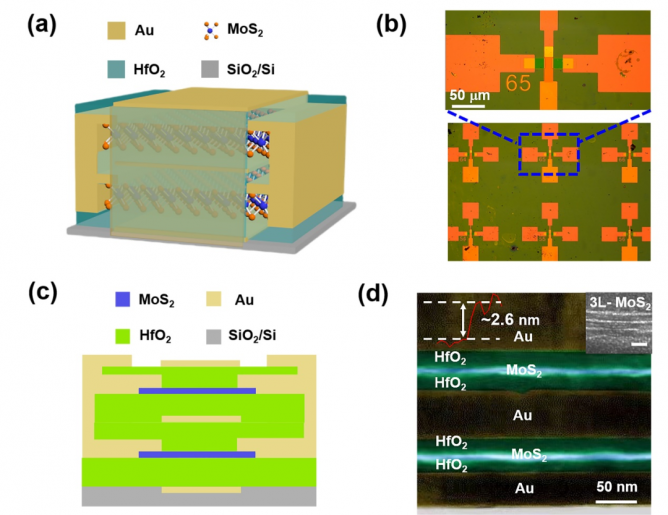

此工作中的MBC-FET是由两层平行的被环形栅电极包裹的MoS2沟道构成,两层MoS2的对应源漏电极通过互联工艺相连。图1所示为MoS2的MBC-FET 立体和横截面结构示意图、阵列图片,以及器件截面的TEM表征。

图1. (a) 基于MoS2的MBC-FET三维结构示意图;(b) MBC-FET器件阵列的光学图;(c) 基于MoS2的MBC-FET的截面示意图;(d)MBC-FET的截面高清TEM表征,左上角的内嵌图是三层MoS2的AFM,右上角的内嵌图是三层MoS2截面的高清TEM表征。

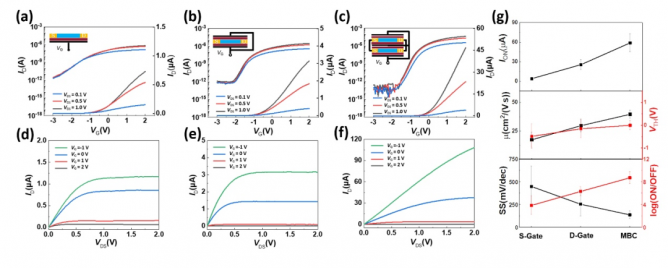

其次,图2 (a)-(c)展示了单栅、双栅以及MBC结构栅控的晶体管的转移特性性能对比。在VDS 为1 V 和 2 V的条件下,同样面积尺寸的单栅和双栅晶体管的驱动电流分别为0.6 μA and 3.2 μA,而MBC-FET的驱动电流增加到了45 μA。并且其关态电流仅为10-13 A。图(g)给出了单栅、双栅以及MBC-FET的电学性能对比,分别各统计了15个器件的电学性能。整体来看,相比于单栅和双栅晶体管的性能,二维半导体作为沟道的MBC-FET的性能得到了极大的提高,具有更大的驱动电流,更高的迁移率以及更小的亚阈值摆幅(SS),并且开关比仍然可以保持。

图2. (a)-(d), (b)-(e), (c)-(f) 单栅FET,双栅FET以及MBC-FET的转移特性和输出特性性能对比;(g) 单栅FET,双栅FET以及MBC-FET的电学性能对比。

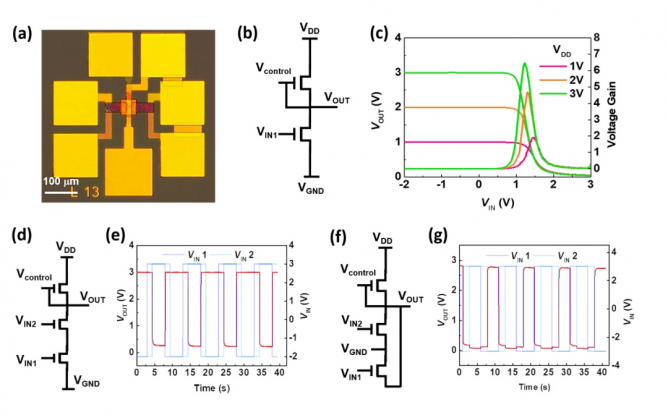

然后,作者们通过对上下两层的MoS2沟道通过不同的层间互连,实现了多种数字逻辑。如图3(a-b) 所示,将上层MoS2 晶体管的栅源电极短接作为负载管,并将上层晶体管的源极与下层晶体管的漏极相连,再将中间的栅电极接地,从而屏蔽了顶部和底部栅极对另一侧沟道的影响。该垂直反相器的测试结果如图3(c)所示,VDD从1V增加到3V,反相器的增益从1.8增加到6.8。基于垂直的两层MoS2沟道,作者同时也制备了NAND和NOR逻辑。该垂直结构相较于传统的平面结构可以省下2/3的电路面积。该结构的NAND和NOR的动态响应,如图(e)和(g)所示。

图3. (a)-(b) 基于n-MoS2 FET的垂直反相器的光学图和电路结构示意图;(c) 垂直反相器的电压转移特性和电压增益曲线;(d)-(f) NAND和NOR的电路结构示意图;(e)-(g) NAND和NOR分别在1Hz的频率下的动态响应。

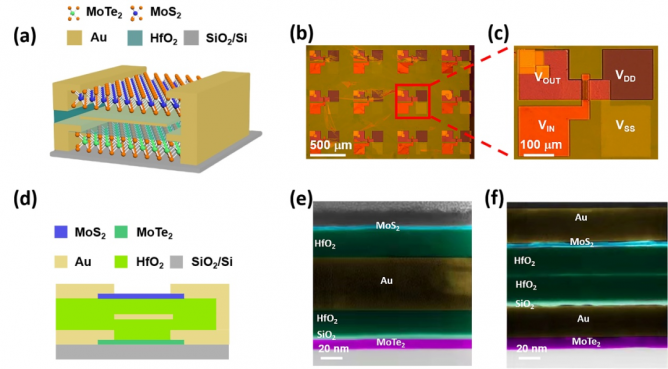

论文的第二部中,作者利用两种二维半导体材料实现了垂直C-FET结构,其三维示意图如图4所示。上层的N型MoS2 晶体管作为反相器的下拉管,下层的P型MoTe2 晶体管作为反相器的上拉管。下拉管的漏极和上拉管的源极通过通孔连接作为VOUT。此时,垂直结构中间的公共栅电极作为VIN,下拉管的源极接地,上拉管的漏极接VDD。此时,MoTe2沟道和MoS2沟道能够同时被中间的公共栅电极调控。

图 4. (a) C-FET的三维结构示意图;(b)-(c) C-FET阵列的光学图;(d) C-FET截面示意图;(e)-(f) 分别是C-FET沟道区域和VDD区域的截面的高清TEM图。

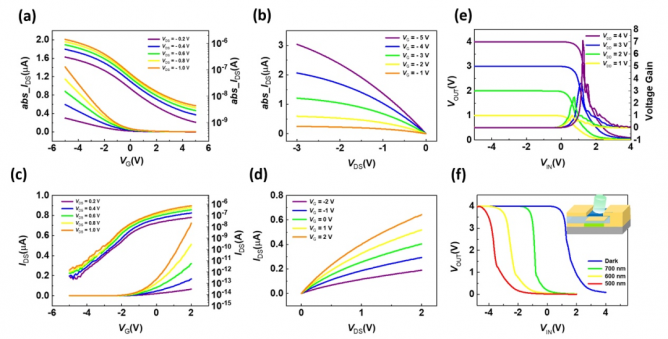

独立测试的MoTe2 晶体管和MoS2 晶体管的电学特性如图(a)-(d)所示,两种晶体管均展现了良好p型特性和n型特性。接下来就是C-FET结构的反相器测试,当给中间的公共栅电极施加负电压的时候,MoS2 沟道被关断,MoTe2沟道被开启,VOUT输出高电平;当公共栅电极施加正电压,MoS2沟道被开启,MoTe2沟道被关断,VOUT输出低电平。图3(e) 展示了在偏压1V到4V下,此C-FET器件的电压转移特性和电压增益。在VDD为4V时,C-FET可以获得7V/V的较好电压增益。最后,作者还证明了C-FET的阈值开关电压可以由不同波长的光信号来调控,这也证明了C-FET结构在传感和光电领域的潜在应用。

图5. (a)-(b) MoTe2 FET的转移特性和输出特性;(c)-(d) MoS2 FET的转移特性和输出特性;(e) 在偏压1V到4V下,C-FET的电压转移特性和电压增益。

总结:

此工作基于晶圆级的二维半导体薄膜,成功制备MBC-FET和C-FET结构的晶体管阵列。而且该工作中提出的二维器件工艺与硅基CMOS工艺更为兼容,有利于未来二维半导体材料的产业化应用。此外,虽然目前阵列器件的最小精度尺寸受限于设备条件,但是结合近期学术界关于二维半导体短沟道原型器件的报道,完全可以验证2 nm节点中引入二维半导体材料可行性,并进一步探究2 nm以下的技术可行性。

论文信息:

Wafer-Scale Demonstration of MBC-FET and C-FET Arrays based on Two-Dimensional Semiconductors

Yin Xia, Lingyi Zong, Yu Pan, Xinyu Chen, Lihui Zhou, Yiwen Song, Ling Tong, Xiaojiao Guo, Jingyi Ma, Saifei Gou, Zihan Xu, Sheng Dai, David Wei Zhang, Peng Zhou*, Yu Ye*, Wenzhong Bao*

Small

DOI: 10.1002/smll.202107650

原文链接:

https://onlinelibrary.wiley.com/doi/10.1002/smll.202107650

原文链接:

https://onlinelibrary.wiley.com/doi/10.1002/smll.202107650