对于当前IC设计领域正崛起的新兴应用以及工程师们所面临的技术挑战,在整个产业链中大概不会有其他人比各家EDA供应商有更敏锐的观察与更深入的了解──而从2019年包括新思科技(Synopsys)、益华计算机(Cadence Design System)与Mentor (现隶属于Siemens)等三大EDA厂商在他们各自的年度使用者大会中讨论的议题就可以得知,人工智能(AI)普及化的时代已经正式来临,而所谓的“异构集成”(Heterogeneous Integration)设计也从概念讨论进入实操阶段。

根据市场研究机构ABI Research发布的最新报告,云端AI应用芯片市场,预期在2024年由2019年的42亿美元增长至100亿美元;至于边缘AI芯片市场,将从目前的19亿美左右规模在2019年至2024年之间以31%的年复合年增长率(CAGR)技术继续扩张。这个潜力巨大的市场吸引的不只是传统半导体公司,还包括众多新创公司,以及系统、服务企业,他们对AI芯片设计的需求为EDA供应商们带来了商机,也成为他们推动设计工具进化的动力。

能实现诸如物体/语音/脸部识别等AI功能的深度学习推动了系统级芯片(SoC)架构的革命,当AI从云端走向终端──也就是所谓的边缘──设备,多样化的应用与感知、连接等功能需求,再加上尺寸与功耗的限制,提升了AI芯片的设计困难度。而为了顺利完成将AI移植到边缘设备的任务,通过2.5D、3D还有“芯粒”(chiplet)等先进封装技术实现之异构集成技术越来越受到关注,这意味着从IC、电路板到整个系统的设计流程出现颠覆性的变化,传统EDA工具已经无法满足工程师们的需求。

随着AI芯片复杂性持续升高,利用工具、服务与专业技术来优化设计案的功耗、性能与成本变得越来越重要。这也就是说,EDA厂商成为AI芯片设计任务中不可或缺的角色。而为了掌握AI商机,EDA供应商们也无不使出浑身解数,包括针对AI芯片设计需求强化旗下IP产品阵容,以及根据AI芯片特性改善自家现有设计流程工具、甚至开发全新设计方法。他们也纷纷将机器学习技术导入设计环境中,以加速AI芯片设计流程与提升验证的准确度。

赋予AI芯片专属DNA

Synopsys产品营销经理Ron Lowman在一篇博客文章中列举了包含深度学习算法的AI SoC设计三大挑战:一是能以更高效率执行矩阵乘法(matrix multiplications)与点积(dot products)等必要性数学运算任务的专门化处理(specialized processing)功能;二是能在处理深度学习所需的权重(weights)、激励(activations)等系数时更快速存取的创新内存架构;三是能实时传递各种数据数据的连接接口。

这意味着传统SoC架构已经无法满足需求,必须从选择IP开始为AI芯片打造专属的“DNA”。为协助客户克服上述AI SoC设计挑战,Synopsys持续扩充其DesignWare IP产品阵容,以新一代的ARC处理器核心与内置CNN引擎的嵌入式图像处理器(EV processor)等,支持机器/深度学习所需的专门化处理,并有涵盖HBM2/HBM2E、CCIX以及PCIe5、MIPI的最新内存与数据传输接口IP选项,满足AI芯片设计中的内存高速存取与连结性需求。此外因个人隐私保护越来越受到重视,Synopsys也能提供在芯片开发初期就确保AI数据安全性的IP选项。

Cadence则是在去年发布了专为AI设计打造的Tensilica DNA 100处理器 IP,并于2019年正式出货。这里的DNA指的是“深度神经网络加速器”(Deep neural-network accelerator)。Cadence指出,神经网络的特征在于权重和激励函数的固有稀疏度,加载与乘以0会造成其他处理器不必要的消耗,DNA 100则以专注硬件运算的引擎解决以上问题,充分利用其稀疏度提高能效并减少运算操作,因此在性能上有4.7倍的提升,功耗也有大幅改善。

除了Tensilica DNA 100,Cadence也可提供一系列内存接口与高速连接IP,以满足AI SoC的设计需求,Cadence资深副总裁兼数字与签核事业群总经理滕晋庆(Chin-Chi Teng)在8月于台湾举行的2019年度CDN Live使用者大会上发表专题演说时指出,该公司正分别从外部与内部将机器学习导入设计工具引擎与流程,以加快复杂SoC设计的速度与质量,催生边缘运算以及其他AI应用,实现“普及智能”(Pervasive Intelligence)的愿景。

(来源:Cadence)

至于Mentor,如同该公司IC EDA部门执行副总裁Joseph Sawicki所言,虽然Mentor并未将IP视为核心业务,一直以来也不是IP市场上积极参与者,但是在AI芯片设计方面,该公司则是专注于与学术界以及业界领先供应商合作,思考如何能在设计环境中让客户妥善集成各种各样的IP以实现设计优化,同时将机器学习导入工具中,提升设计生产力与验证准确度。

为AI芯片量身打造的设计环境

除了提供AI芯片专属的IP产品阵容,为AI芯片量身打造的设计工具平台可说是EDA供应商角逐AI商机的主战场。毕竟如何实现设计仍是决定最后的AI SoC能否充分发挥所集成的IP在理论上的最高性能并取得成功的关键。

在前面提到的博客文章中,Synopsys的Lowman表示,尽管AI SoC开发流程仍在持续变化,在本质上仍包含系统规格与架构设计、逻辑与功能电路设计、实体设计、验证与分析,还有制造、封装与测试、硅后验证等标准阶段,需要相对应的工具来提升设计效率。此外,软硬件协同设计(co-design)的重要性在AI SoC设计中会被放大,而且需要协同设计的不只有软件与硬件,还有内存与处理器,这类因AI衍生的协同设计需求,也需要新一代的工具来应对。

为此Synopsys的策略是为AI芯片打造新一代设计与验证解决方案,包括推出支持SoC设计初期优化的架构探索工具Platform Architect Ultra平台,经AI强化的融合设计平台(Fusion Design Platform)──包含RTL合成、测试、物理验证、验证与签核,以及Verification Continuum验证平台──包括VCS功能验证系统、VC Formal形式化验证(formal verification)、Verdi软硬件除错、ZeBu硬件仿真(emulation)系统、HAPS原型建造系统,以及针对先期软件开发和优化的Virtualizer虚拟原型结构。

Synopsys设计事业群联席总经理Deirdre Hanford在今年5月举行的该公司年度SNUG Taiwan使用者大会上表示,复杂的AI SoC就如同台北101大楼,精密的架构设计是充分展现其功能性与确保安全性的基础,这就是Platform Architect工具所扮演的角色。而集成了Synopsys数字设计工具的Fusion平台,包括最新发布的Fusion Compiler方案,则能让SoC设计流程大幅缩短,并实现芯片功耗、性能与面积(PPA)表现的优化。

滕晋庆表示,Cadence在2019年制定了“智能系统设计”(Intelligent System Design)策略,从三个层面协助工程师应对大数据/AI时代的设计挑战。其一是包含先进IC、封装与PCB设计流程所需EDA工具与关键IP的“设计卓越”(Design Excellence);其次是涵盖实体设计、分析/仿真与嵌入式安全方案的“系统创新”(System Innovation);最后则是将机器学习导入工具,提升设计速度与质量,促成“普及智能”。

Cadence已推出了经过机器学习强化的新版本Allegro、Virtuoso、Innovus、Genus、Quantus、Tempus、Liberate、JasperGold等一系列设计流程工具与验证解决方案,并将持续投资与开发以带来更高自动化、更大生产力与更准确设计结果的技术。此外,Cadence的云端解决方案也是实现其“智能系统设计”策略不可或缺的一环,该公司通过与AWS、微软Azure等伙伴的合作,让客户能为设计尖峰需求以安全、弹性的方法扩充运算资源,提升设计效率。

对于AI的“特定域”(domain specific)架构特性,Mentor的Sawicki则认为高端合成技术(HLS)是优化设计方法;他指出,HLS能支持对AI应用十分关键的架构探索,特别是与内存相关的配置以及功耗分析。Mentor的Catapult HLS平台则能让设计工程师以标准化的ANSI C++与SystemC语言来描述功能意图,以高速度产生高质量的RTL,这将大幅降低AI设计的验证成本。Catapult HLS平台还包括系统集成所需的FPGA演示器、CPU子系统、软硬件接口与HLS加速器模板。Nvidia的Tegra X1芯片就是Catapult HLS平台的成功设计案例之一。

Mentor也持续将机器学习(ML)算法导入工具中,例如新发布的Calibre良率分析平台工具Machine Learning OPC (mlOPC)以及LFD with Machine Learning,都是利用机器学习实现更快速、精确的硅后验证结果;这些新版进一步扩展了Mentor的AI/ML驱动设计解决方案阵容──该公司在2018年收购擅长于将AI/ML概念与EDA结合的开发商Solido,并将其模拟测试工具纳入旗下,包括Solido Variation Designer、Solido ML Characterization工具套件以及Tessent YieldInsight等,为工程师带来更智能化的设计解决方案。

异构集成设计趋势带来的市场竞争变局

AI应用带来的异构集成设计需求,如2.5D、3D与chiplet先进封装,与在汽车、高性能运算、高频通讯等应用领域的设计,都对系统级分析工具有越来越高的需求,如电源完整性与可靠度分析,以及针对电磁、热流体、应力等参数的多物理(multiphysics)模拟解决方案等。EDA厂商为了给客户提供更全面的设计支持而跨界,在工程仿真(CAE)领域推出相关工具,而工程仿真解决方案供应商也将触角从系统延伸到半导体设计了。

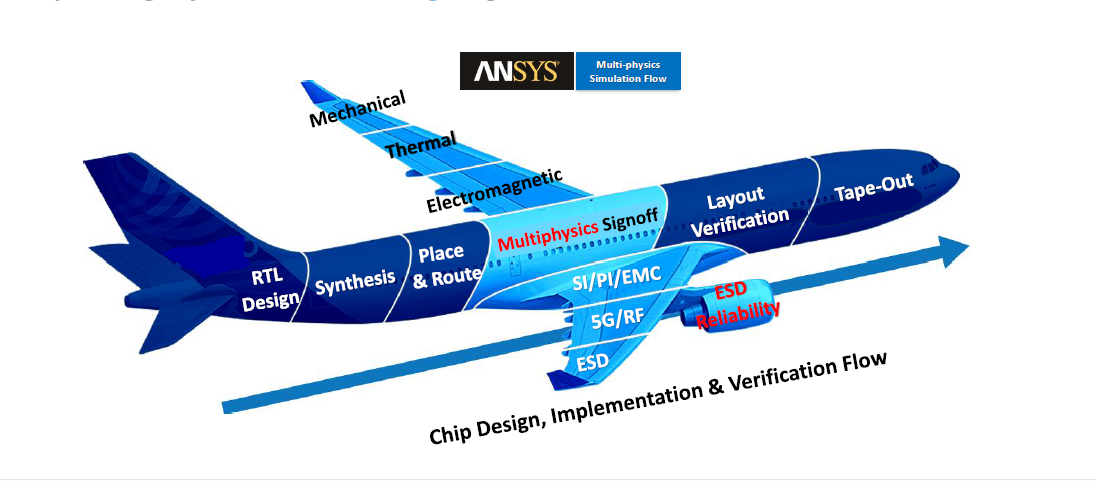

Ansys就是一家在IC领域着墨越来越深的CAE工具供应商,该公司已有超过20年发展历史,其3D电磁模拟工具HFSS (收购自Ansoft)在汽车、航天等机械系统设计领域可说是众所周知。但在Ansys于8月底专为IC设计工程师举办的半导体解决方案研讨会上,该公司技术总监Larry Williams就表示,“有一家IC产业的高层跟我说,在几个月前我们连Ansys这个名字都没听过,”但现在,多物理模拟已经成为复杂度日益升高的3D IC设计不可或缺的工具。

Ansys全球副总裁兼半导体事业部总经理John Lee表示,以堆栈裸片方式实现的系统级IC封装,就会有对电源、热与电磁等物理参数的分析需求,而已经开始蓬勃发展的异构集成3D封装,又加上对应力、机械相关参数,以及未来5nm、3 nm工艺节点带来的技术复杂性,工程师们如果没有仿真软件工具的协助,就很难完成设计任务。

Lee指出,Ansys的多物理分析解决方案,能扮演与其它EDA工具相辅相成的角色,如同一架飞机需要结合可以保持平衡的左右机翼与推进器,才能顺利飞向天空。他强调,Ansys与Cadence、Synopsys等EDA供应商的工具与客户群重叠性很小,他也认为重叠范围将不会扩大,而该公司也将会继续专注于提供电子设计所需的工程仿真软件,与EDA厂商之间密切合作,推动包括AI、5G、自动驾驶车辆/电动车,甚至是未来电动化的飞机等创新电子系统的实现。

实际上,EDA厂商越来越注重能否提供从IC到电路板、系统的全面性设计解决方案,例如Cadence今年首度推出3D系统分析工具Clarity,就是为协助客户有效解决从芯片、封装、电路板到连接器与缆线的复杂3D结构设计所面临的EM问题,而Siemens与Mentor的结合也是为了能在单一平台上,满足电子设计从IC零部件到系统的完整数字仿真需求。AI时代来临引发的电子设计流程变化,CAE与EDA厂商之间未来的竞争与合作关系很值得玩味。