0 引 言

随着集成电路的发展,一个高稳定、高精度的基准电压源变得越来越重要。特别是在D/A,A/D转换以及PLL电路中,温度稳定性和精度之间关系到整个电路的精确度和性能。

当今设计的基准电压源大多数采用BJT带隙基准电压源结构,以及利用MOS晶体管的亚阈特性产生基准电压源;然而,随着深亚微米CMOS工艺的发展,尺寸按比例不断缩小,对芯片面积的挑战越来越严重,双极型晶体管以及高精度电阻所占用的面积则成为一个非常严重的问题。在此,提出一种通过两个工作在饱和区的MOS管的栅源电压差原理,产生一个与绝对温度成正比(PTAT)的电流,利用这个电流与一个工作在饱和区的二极管连接的NMOS晶体管的阈值电压进行补偿,实现了一个低温漂、高精度的基准电压源的设计。

1 NMOS晶体管的构成

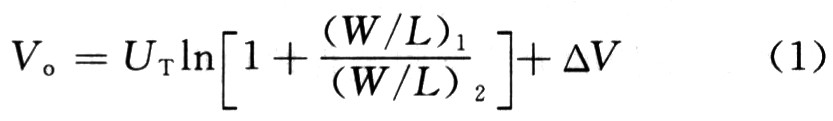

两个工作在弱反型区的NMOS晶体管M1和M2的结构如图1所示。

其输出电压V0可以表示为:

式中:UT=kT/q;k为波尔兹曼常数;△V表示实际中晶体管失配引入的误差,是个常数,这里忽略它的影响。由此得到:

式中:

是由温度决定的倍增因子,后面将对其温度特性进行讨论。

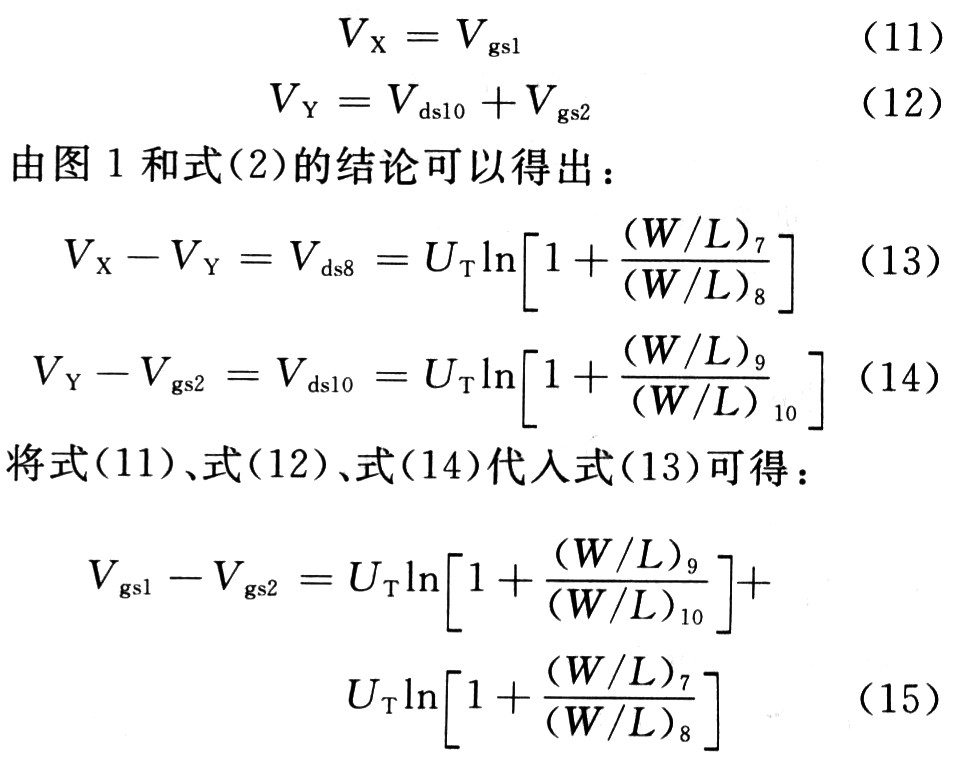

对于NMOS晶体管M1和M2,其栅源电压分别为Vgs1和Vgs2,那么图3中电压为:

![]()

如果利用前面提到的两个工作在弱反型区的MOS管输出电压特性来控制两个工作在饱和区的NMOS的栅极电压Vgs1和Vgs2,使得:

![]()

式中:λ为比例常数。

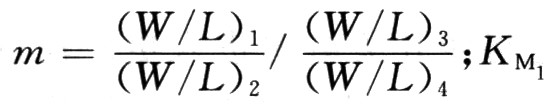

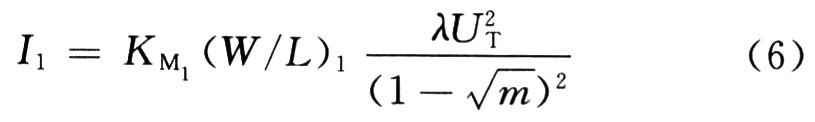

将式(5)代入到式(3)可得:

对于参数KM1,它主要受晶体管迁移率λ的影响,通常被定义为:

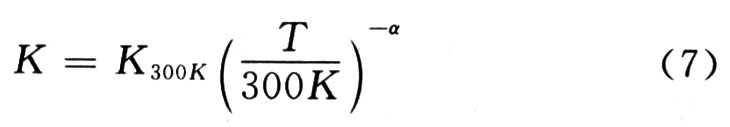

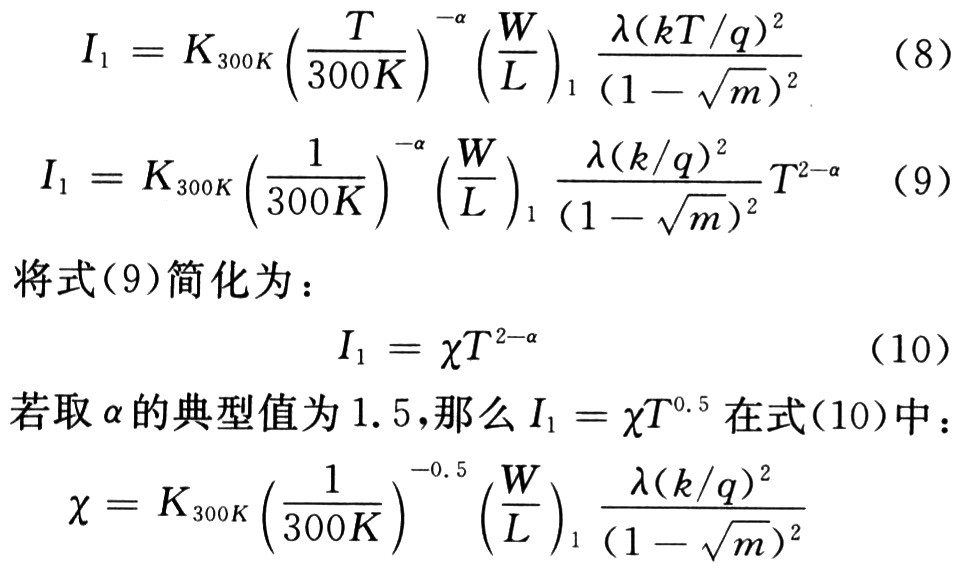

式中:T为绝对温度;α由工艺决定,典型值为1.5.将式(7)代人式(6)可得:

它为一个与温度无关的常数。

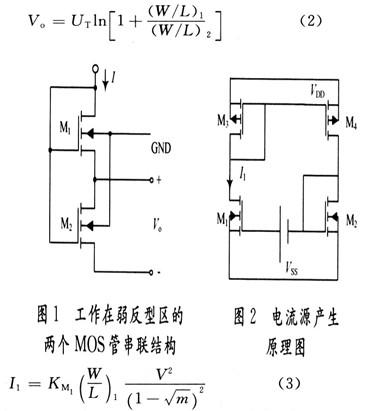

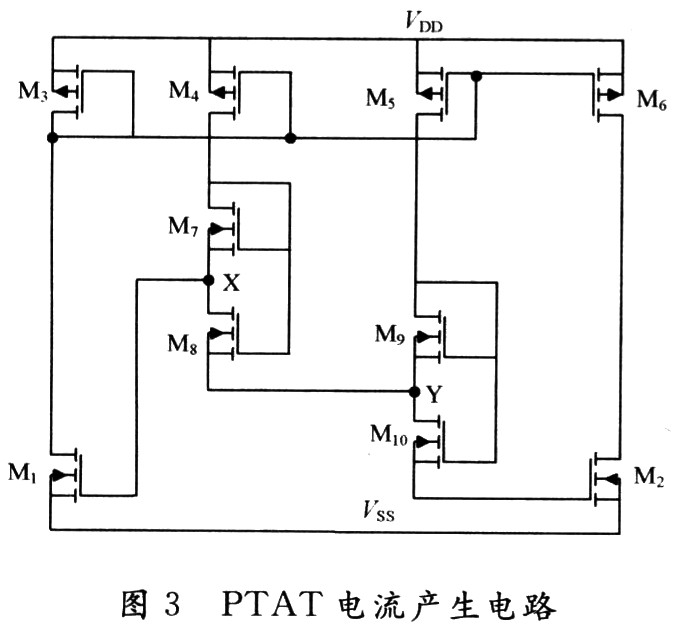

通过上面分析可知,此方法可以得到一个与绝对温度成正比(PTAT)的电流I1.具体实现电路如图3所示。

图3电路中,M3~M6四个PMOS晶体管工作在饱和区,它们的宽长比相同。M1和M2两个NMOS晶体管工作在饱和区,它们的宽长比为(W/L)2/(W/L)1=m.通过调节电路,使得M7~M10四个NMOS晶体管工作在深线性区。现在讨论电路的工作原理。

对于X点和Y点的对地电压,可以分别表示为:

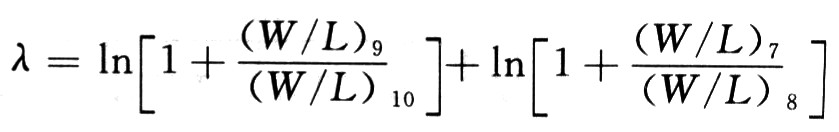

通过式(5)和式(15)可以看出,在这个电路中,式(5)的系数:

它是一个仅与器件尺寸有关,而与温度无关的常数。

通过式(9)和式(10)可知,此电路可以产生一个与绝对温度成正比的电流。[!--empirenews.page--]

2 基准电压的设计

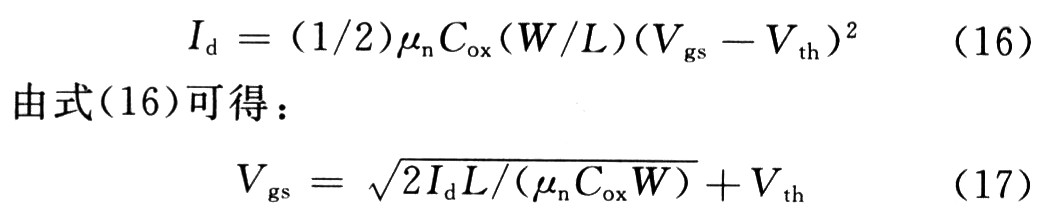

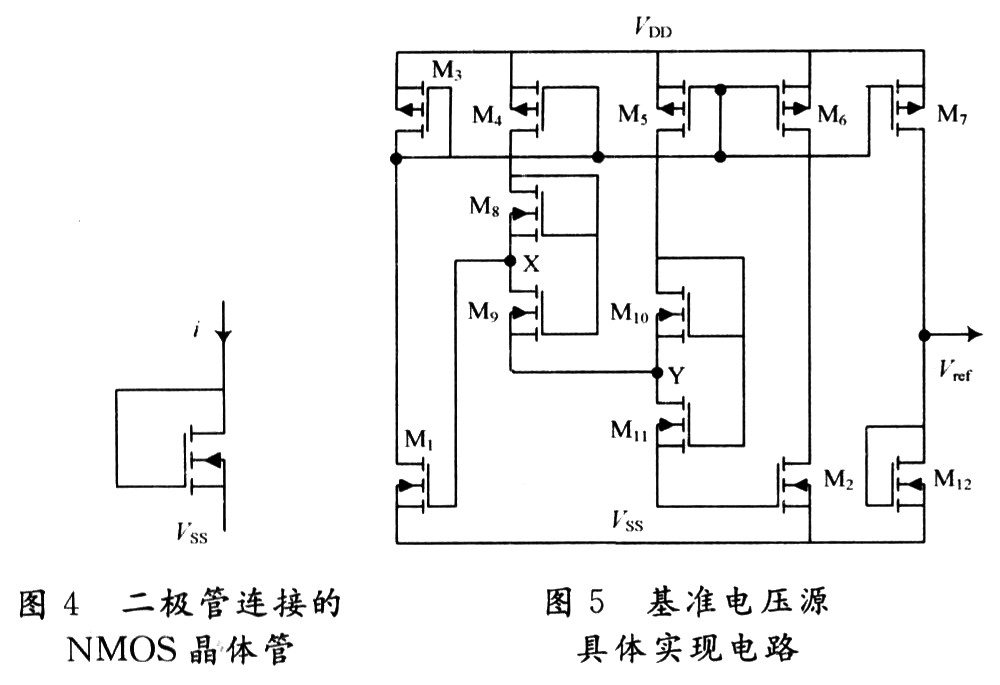

对于一个工作在饱和区的二极管连接NMOS晶体管,如图4所示,它的Vgs=Vds流过它的饱和漏电流为:

对于MOS管的阈值电压Vth,它的一阶近似表达式可以表示为:

![]()

式中:Vth0为MOS管工作在绝对零度时的阈值电压;aVT为一个与温度无关的常数;T-T0为温度变化量。对于一个MOS管的迁移率μn:它的大小可以表示为:

μn=μn0(T/T0)-m (19)

式中:μn0为绝对温度时MOS管的迁移率值;T0为绝对零度;T为温度变化量;m为比例变化因子,它的典型值为1.5.

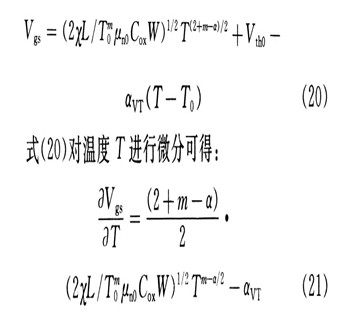

令式(10)中I1为式(17)中的Id,即:I1=Id,将式(10)、式(18)和式(19)代人式(17)整理可得:

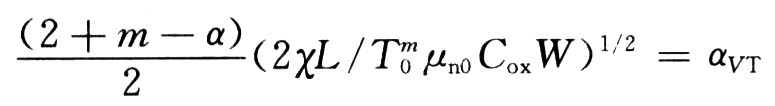

从式(21)可看出,如果适当调节晶体管的宽长比W/L,使得зVgs/зT=0,即:

便可以得到一个高精度、与温度无关的Vgs,即Vref=Vgs=Vds.此思想设计的具体实现电路如图5所示。

对图5进行分析,NMOS晶体管M1和M2通过Vgs1和Vgs2产生漏电流Id1,再通过电流源M3和M7,使得它流入二极管连接的NMOS晶体管 M12,产生一个基准电压源Vref.在图5中,M3~M7五个晶体管尺寸相同,M1和M2晶体管的宽长比比例为1:m.式(21)中的W/L为图5中二极管连接M12管的宽长比。

3 仿真结果与分析

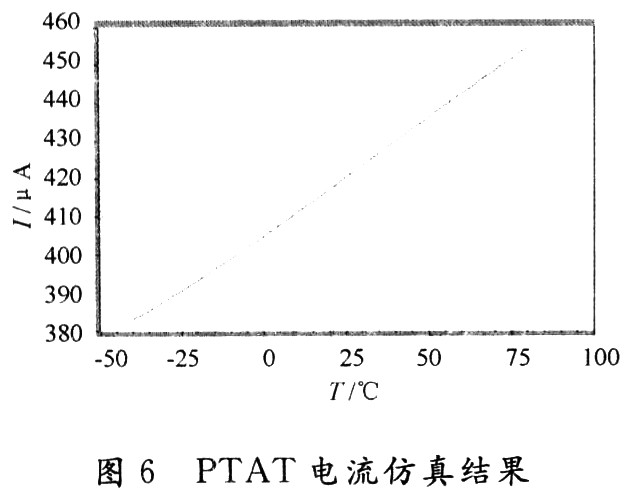

对图3PTAT产生电路进行仿真,可以得到图6仿真结果。

从图6仿真结果可以看出,流过M1管的漏电流与绝对温度成正比,αI/αT△0.6.

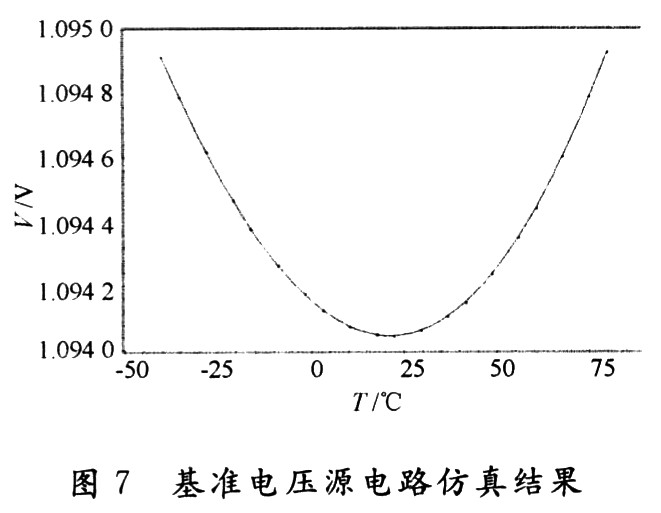

对图5基准电压源电路进行仿真,可得如图7所示结果。通过对图7分析可知,在25℃时,基准电压源的电压约为1.094.04 V,在整个温度范围(-40~80℃)内,其温度漂移系数为6.12 ppm/℃,满足高精度基准电压源的设计要求。

4 结 语

在此,基于SMIC 0.18μm CMOS工艺,采用一阶温度补偿作为基准电压补偿,提出一种新颖的PTAT电流产生电路结构,以对二极管连接的NMOS晶体管的阈值电压进行补偿,得到一个高精度基准电压源。该电路占用芯片面积小,精度高,可移植性强,非常适用于当今高精度的A/D,D/A和高精度运放偏置电路。此电路已成功应用于某款高速DAC芯片中。