作为逻辑工程师,在FPGA和数字IC开发和设计中,一般采用verilog,VHDL或SystemVerilog等作为硬件描述语言进行工程设计,将一张白板描绘出万里江山图景。

工程师在利用硬件描述语言进行数字电路设计时,需要遵守编译器支持的Verilog,VHDL或systemverilog标准规范,并形成良好的RTL设计风格。

本文简要介绍verilog-2005和systemverilog-2017标准,在应用过程中,可根据自己擅长的语言进行设计。

一、verilog-2005标准

Verilog硬件描述语言(HDL)在本标准中定义。Verilog HDL是一种正式的符号,旨在用于电子系统创建的所有阶段。因为它是机器可读和人类可读的,所以它支持硬件设计的开发、验证、综合和测试;硬件设计数据的通信;以及硬件的维护、改装和采购。本标准的主要受众是支持该语言的工具的实现者和该语言的高级用户。

Verilog硬件描述语言(HDL)在1995年作为IEEE标准1364- 1995成为IEEE标准。它被设计成简单、直观和有效的,在多个抽象层次上采用标准文本格式,适用于各种设计工具,包括验证模拟、定时分析、测试分析和综合。正是由于这些丰富的功能,Verilog已被公认为集成电路(IC)设计人员的首选语言。

Verilog包含一组丰富的内置原语,包括逻辑门、用户可定义原语、开关和有线逻辑。它还具有设备引脚到引脚的延迟和定时检查。抽象层次的混合本质上是由两种数据类型的语义提供的:网络和变量。连续赋值提供了基本的结构结构,其中变量和网的表达式可以连续地将值驱动到网上。程序赋值提供了基本的行为结构,其中涉及变量和净值的计算结果可以存储到变量中。设计由一组模块组成,每个模块都有一个输入/输出(I/O)接口,以及对其功能的描述,可以是结构的、行为的,也可以是混合的。这些模块形成一个层次结构,并通过网络相互连接。

随着IEEE Std 1364-2001的完成,在更大的Verilog社区中继续进行工作,以确定该语言的突出问题以及可能增强的想法。当Accellera在2001年开始标准化SystemVerilog时,发现了可能导致Verilog 1364与SystemVerilog不兼容的其他问题。IEEE P1364工作组是作为SystemVerilog P1800工作组的一个小组委员会成立的,以帮助确保这些问题的一致解决。这项合作工作的结果是这个标准,IEEE标准1364-2005。

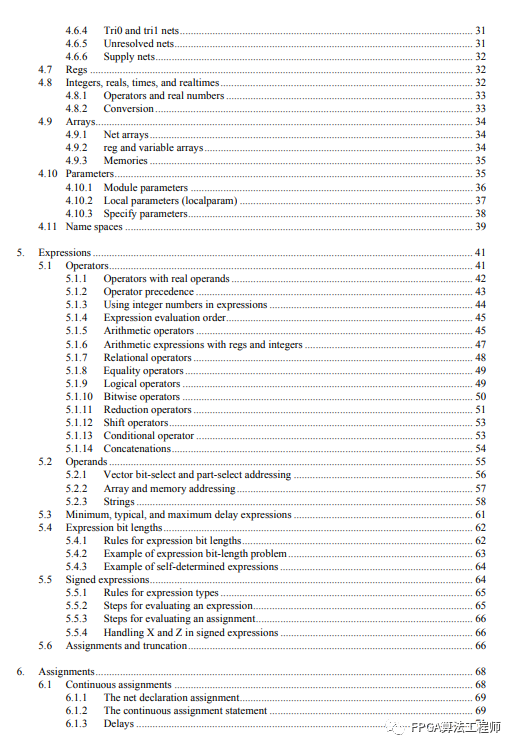

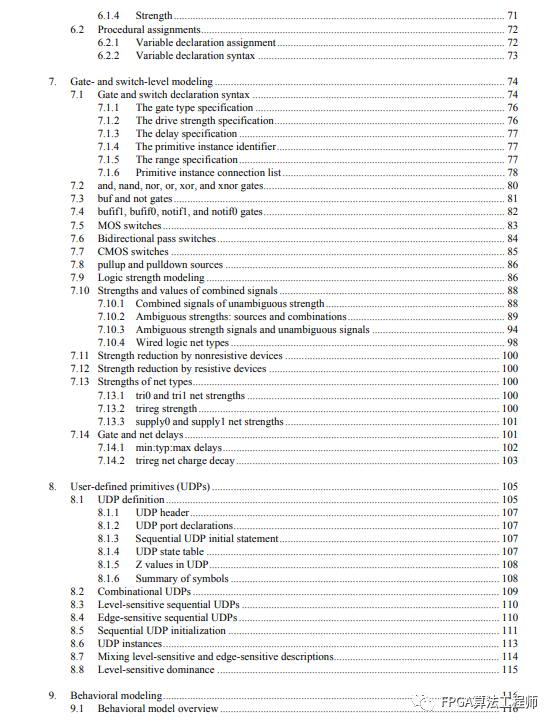

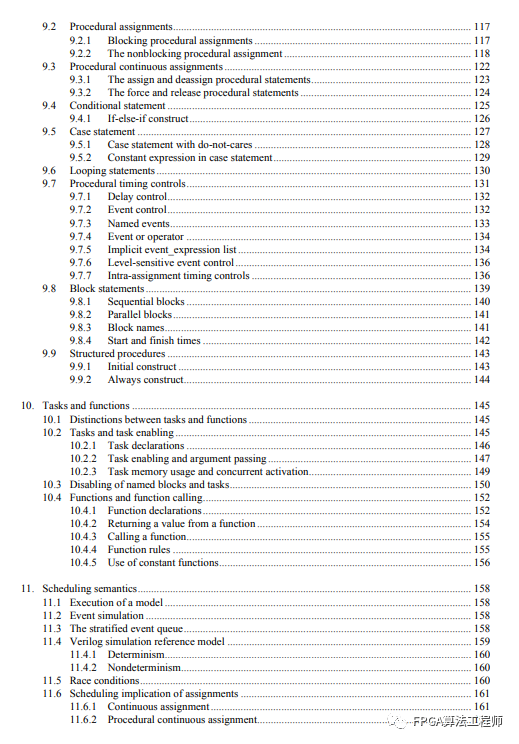

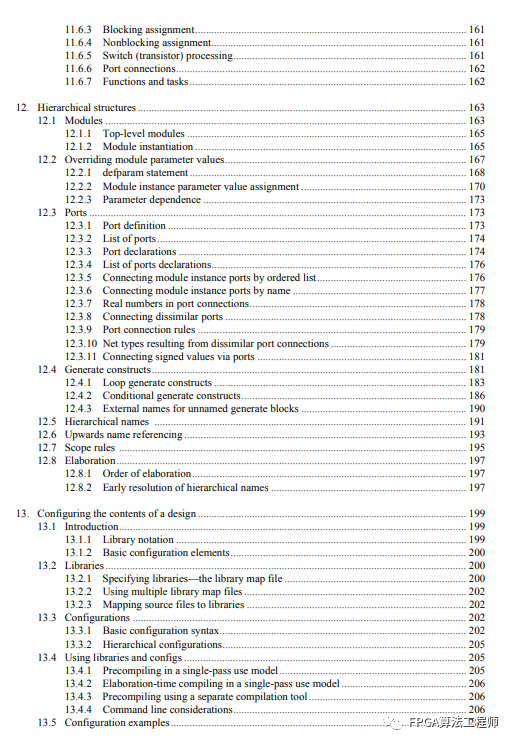

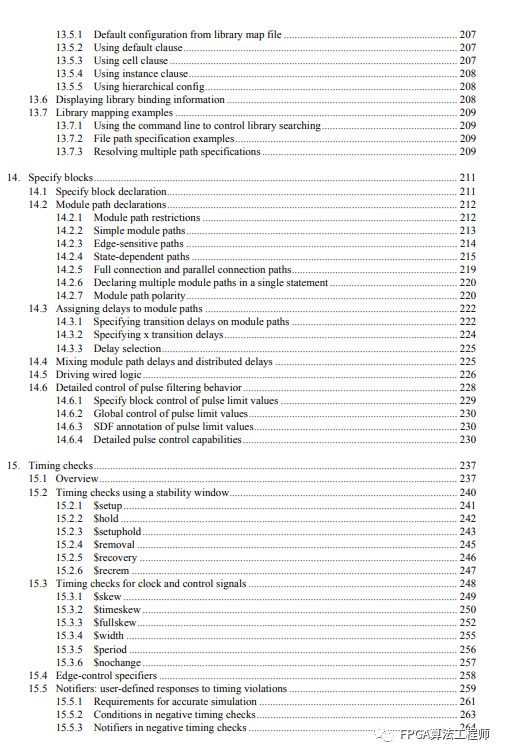

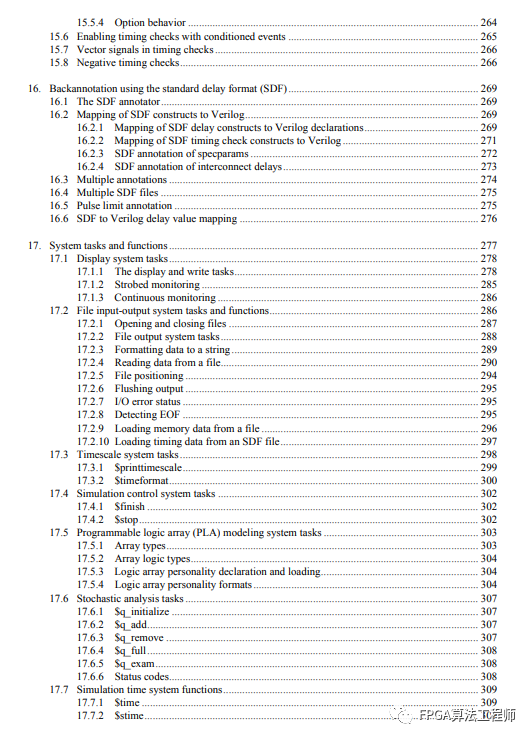

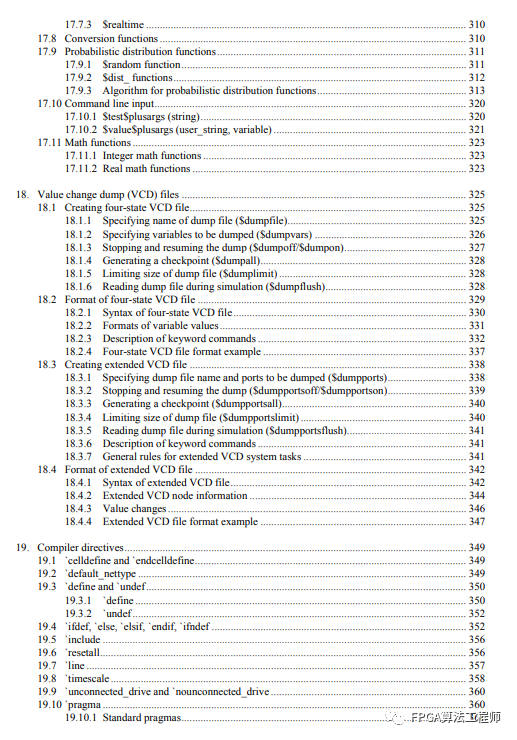

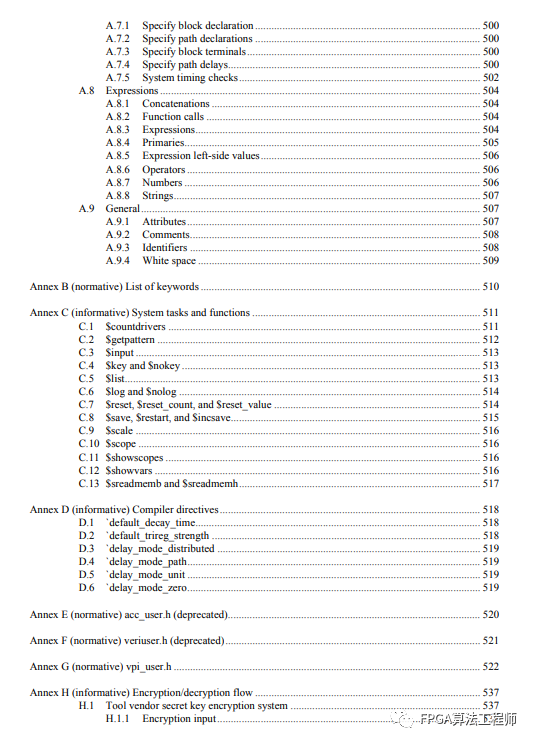

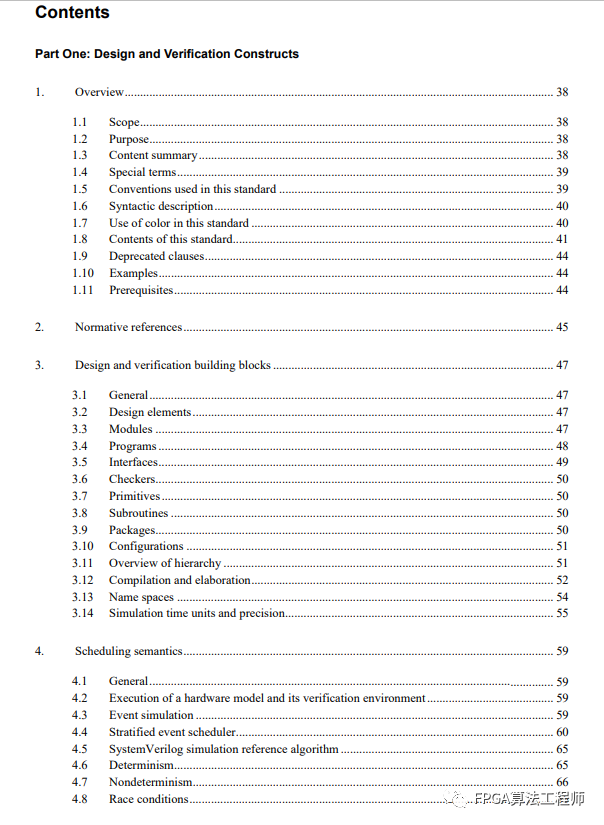

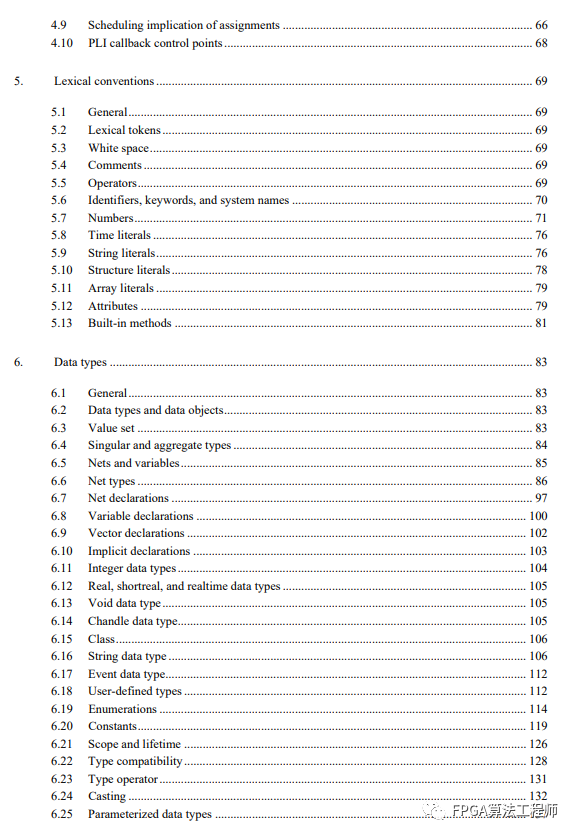

具体来说,IEEE Std Verilog-2005其目录如下:

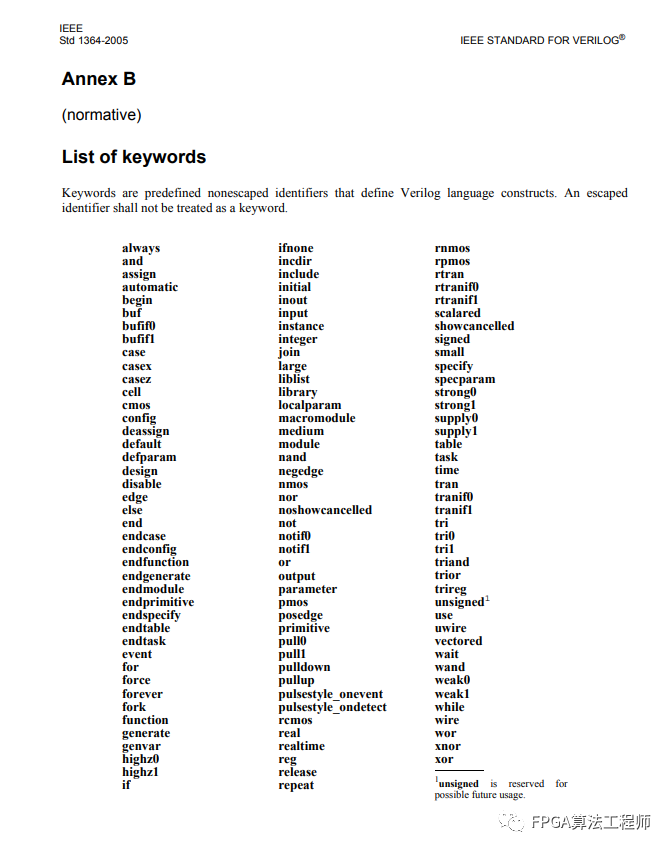

VerilogHDL语言的关键字列表:

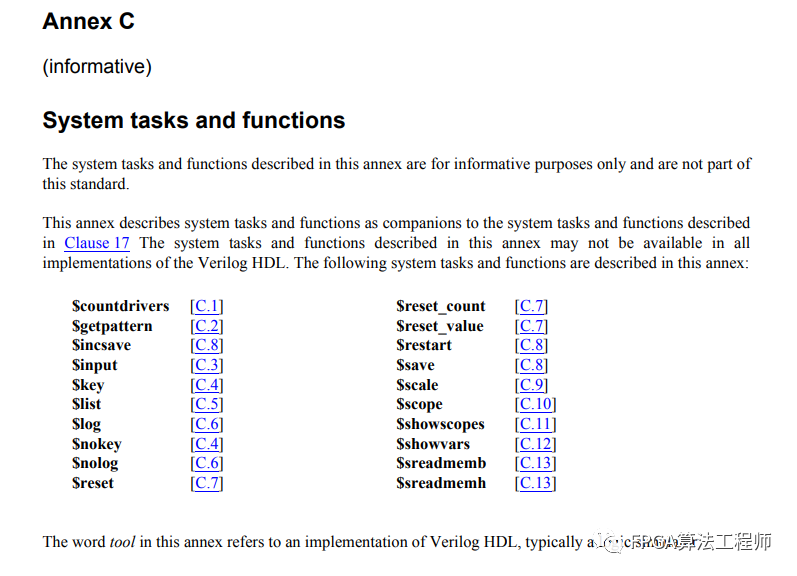

VerilogHDL语言的系统Task和Function列表:

更多详细说明,参阅IEEE Std Verilog HDL。

二、SystemVerilog-2017

本标准为IEEE 1800™SystemVerilog语言提供了语言语法和语义的定义,这是一种统一的硬件设计,规范和验证语言。该标准包括对行为、寄存器传输级(RTL)和门级硬件描述的支持;Testbench、覆盖、断言、面向对象和约束随机结构;并且还为外国编程语言提供应用程序编程接口(API)。

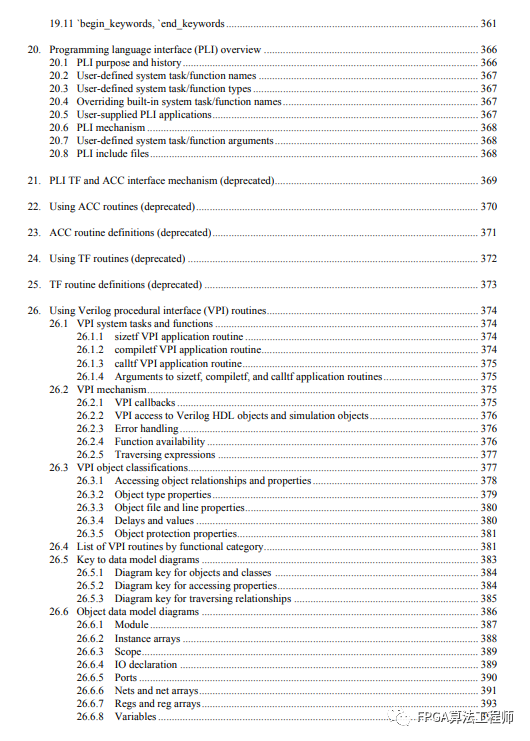

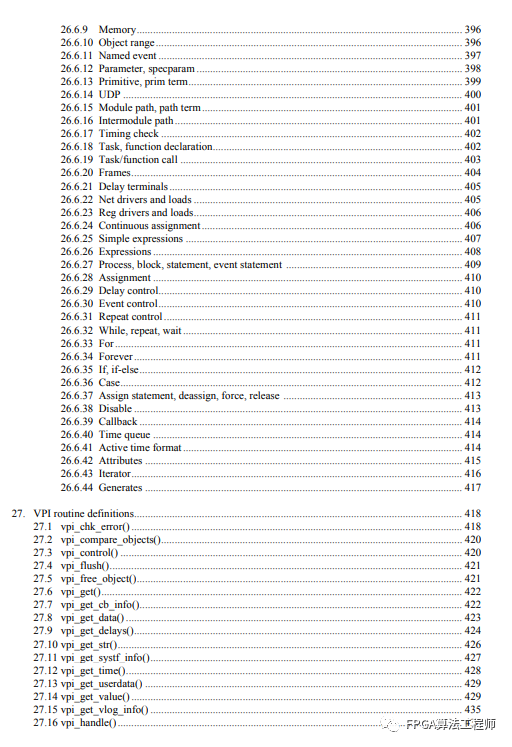

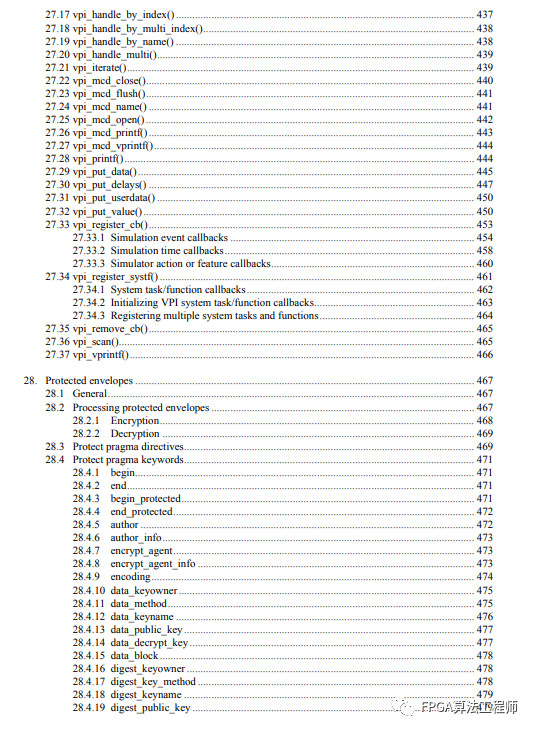

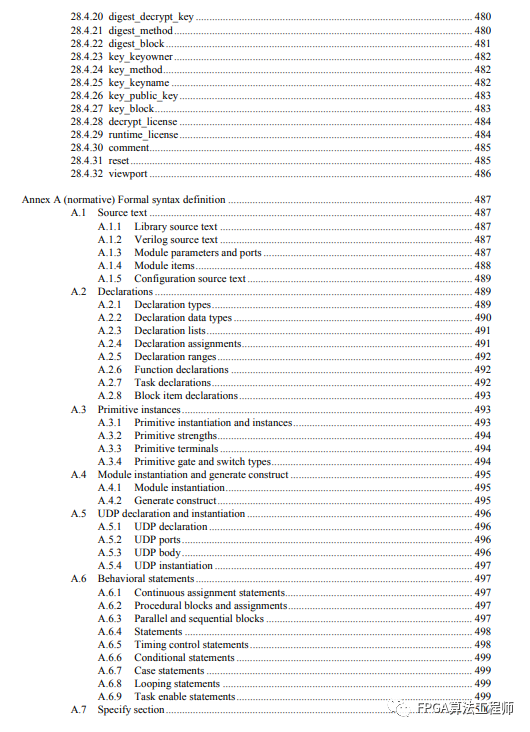

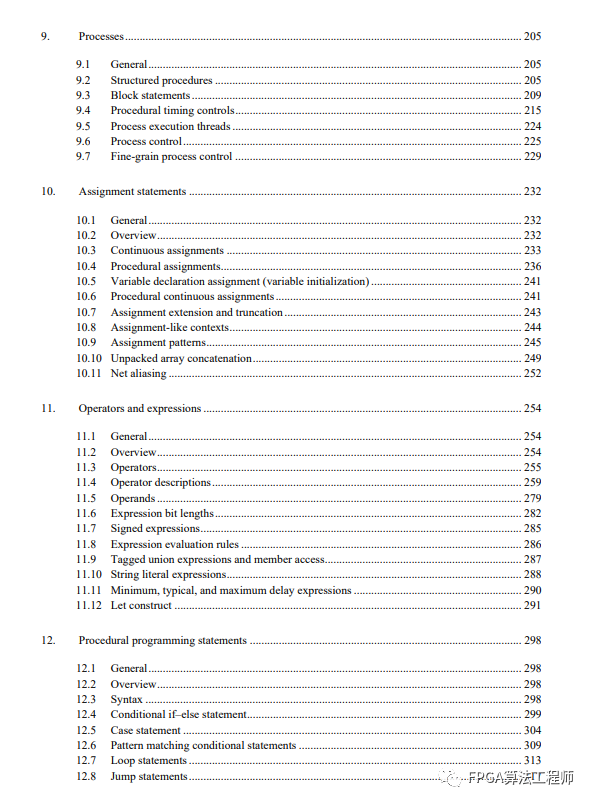

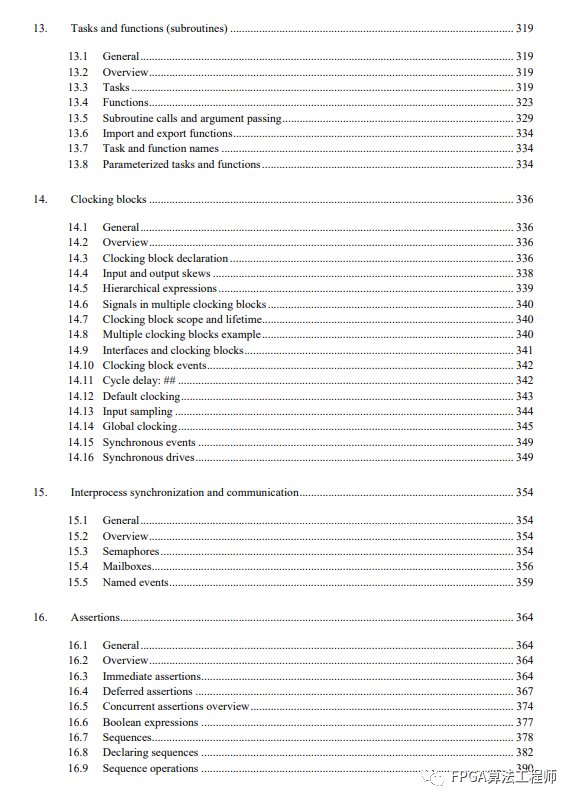

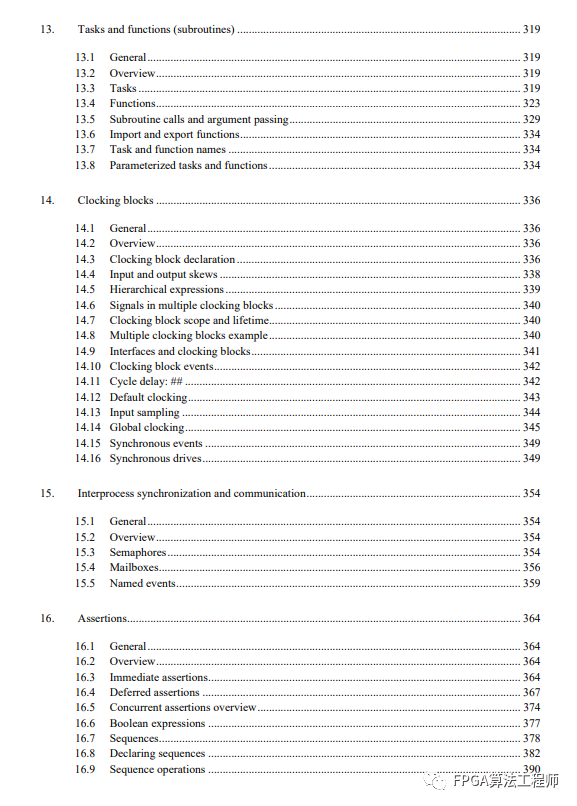

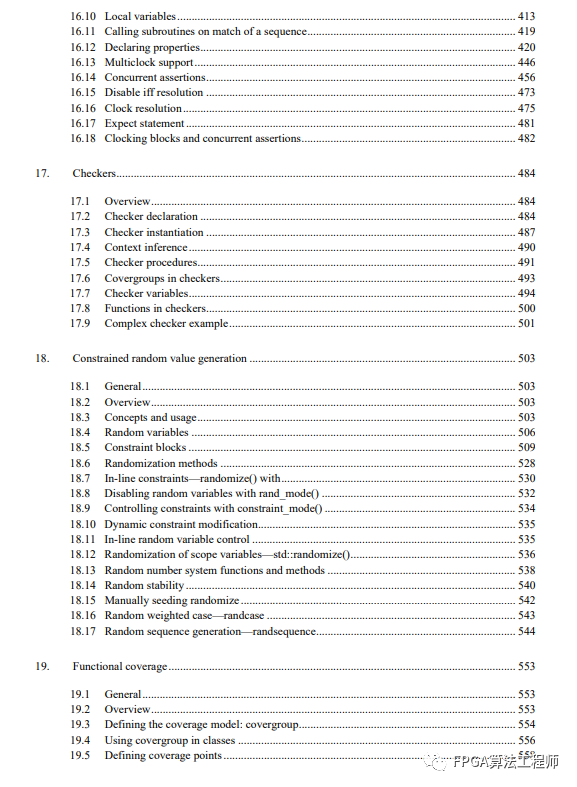

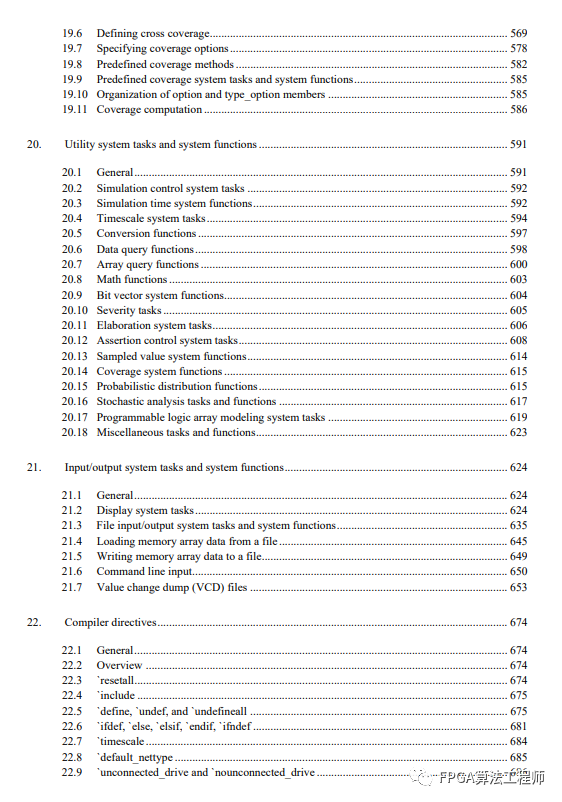

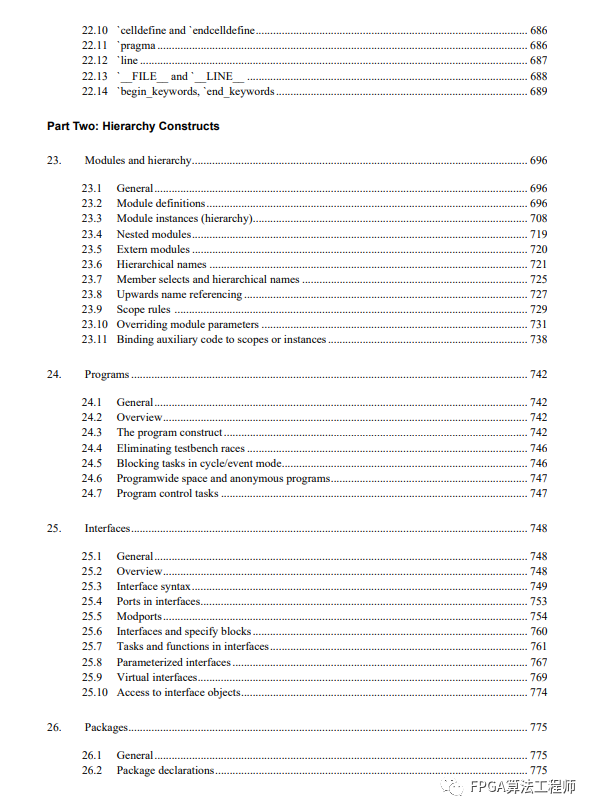

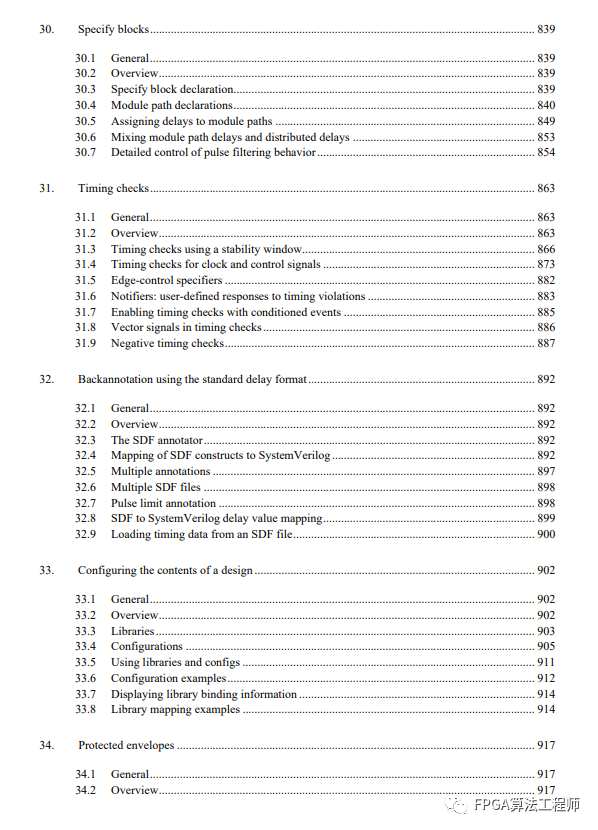

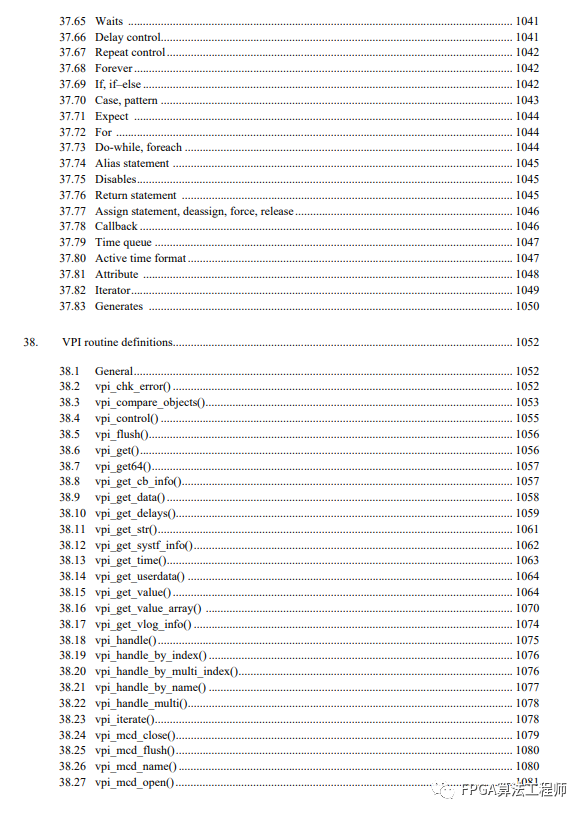

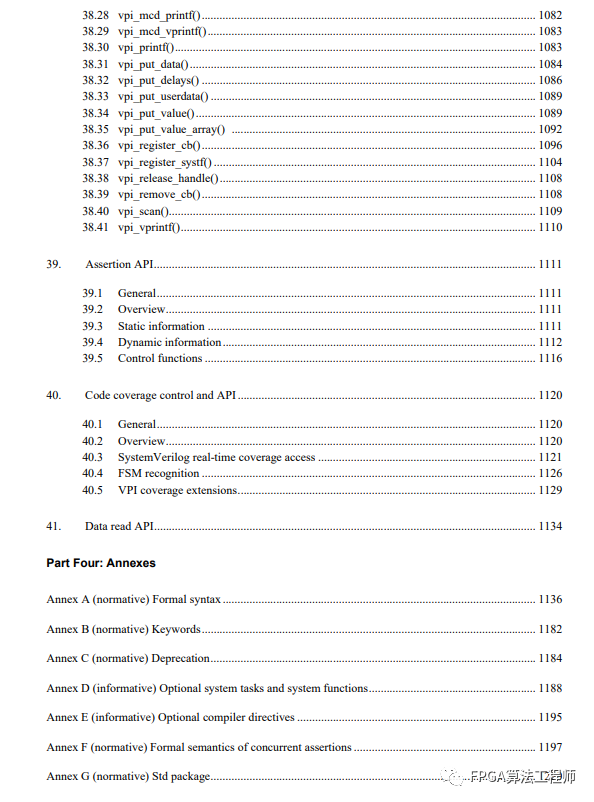

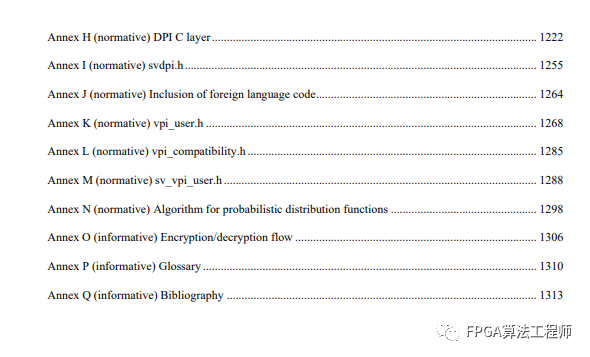

该规范目录如下:

SystemVerilog语言既可以用于设计,也可以用于验证,在FPGA、IC中占有重要地位。相对于VerilogHDL,提供了更丰富的设计和验证规范,SystemVerilog改进了Verilog代码的生产率、可读性以及可重用性。

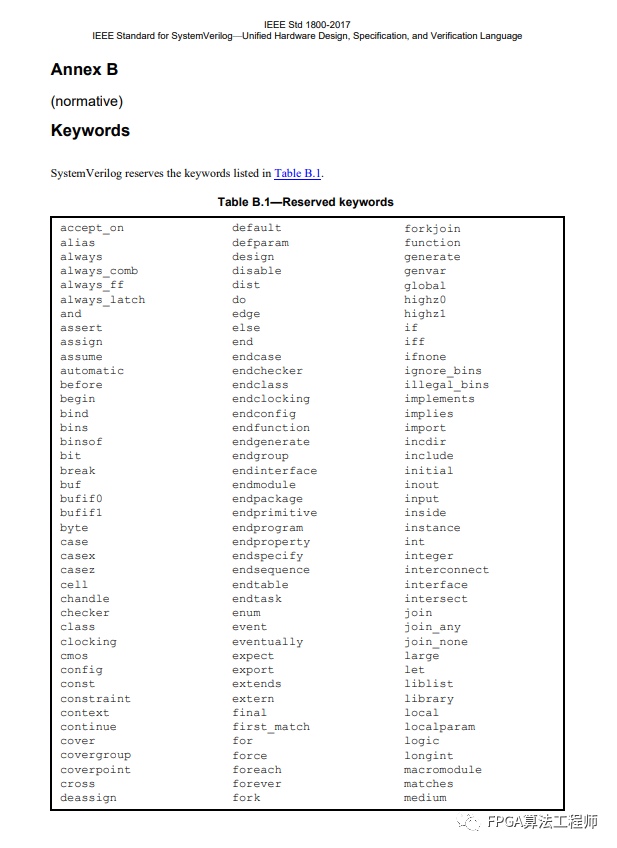

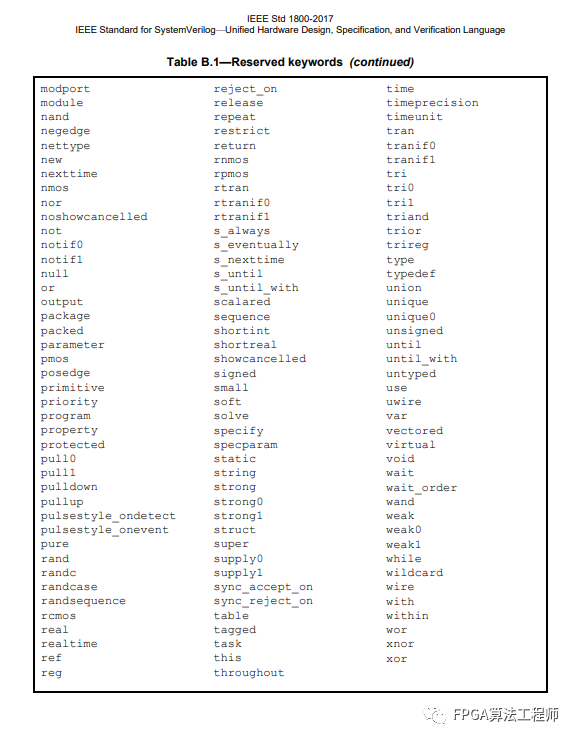

SystemVerilog语言的关键字列表:

更多详细说明,参阅IEEE Std SystemVerilog。

IEEE官网Verilog HDL标准:1364-2005 - IEEE Standard for Verilog Hardware Description Language | IEEE Standard | IEEE Xplore

IEEE官网SystemVerilog标准:1800-2017 - IEEE Standard for SystemVerilog--Unified Hardware Design, Specification, and Verification Language | IEEE Standard | IEEE Xplore

点击左下角”阅读原文“,可前往IEEE官网查看SystemVerilog标准。

更多关于5G、卫星通信、FPGA、数字IC、通信算法等内容,可关注微信公众号【FPGA算法工程师】

技术交流QQ群:860157781

技术合作、产品推广、商业合作、加微信群,请后台发送消息。说明来意,并备注:姓名(昵称)+职业方向+城市。