电子集成技术分为三个层次,芯片上的集成,封装内的集成,PCB板级集成,其代表技术分别为SoC,SiP和PCB(也可以称为SoP或者SoB)

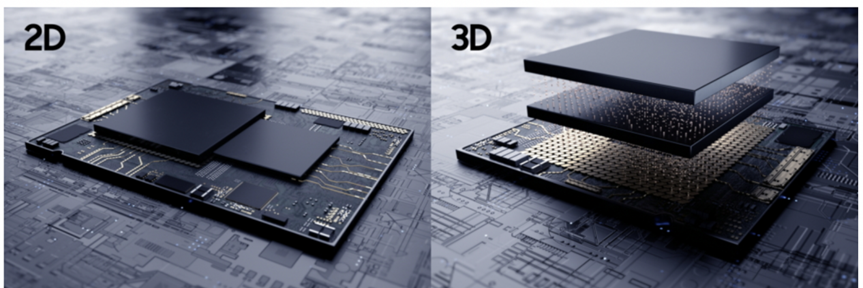

芯片上的集成主要以2D为主,晶体管以平铺的形式集成于晶圆平面;同样,PCB上的集成也是以2D为主,电子元器件平铺安装在PCB表面,因此,二者都属于2D集成。而针对于封装内的集成,情况就要复杂的多。

电子集成技术分类的两个重要判据:1.物理结构,2.电气连接(电气互连)。

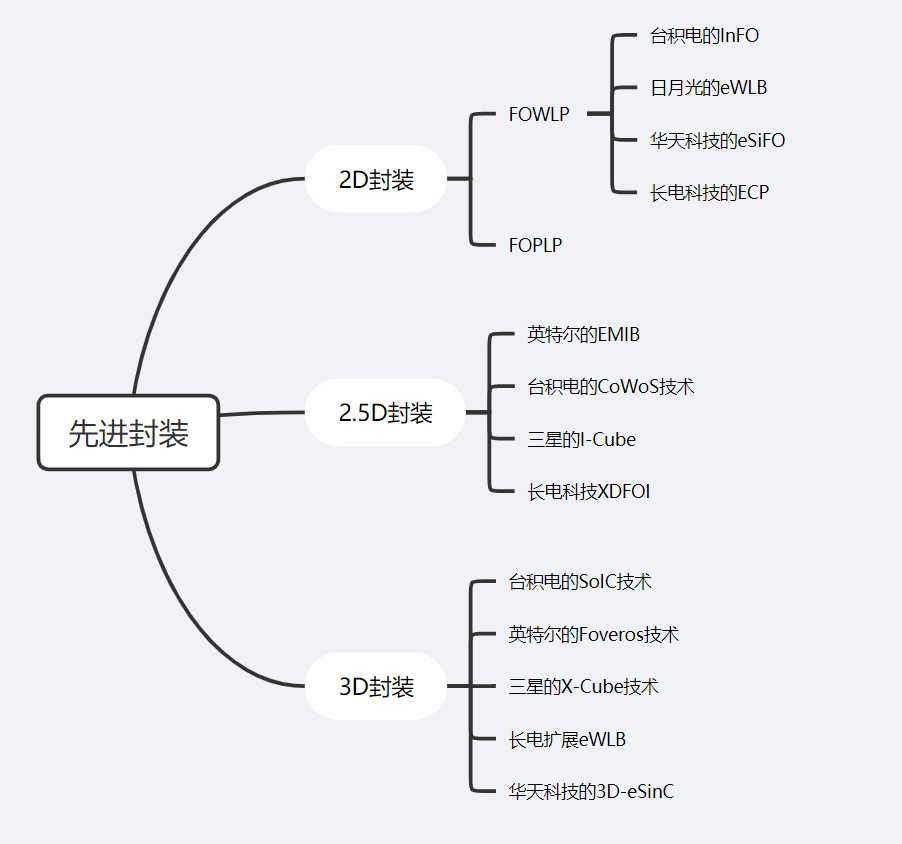

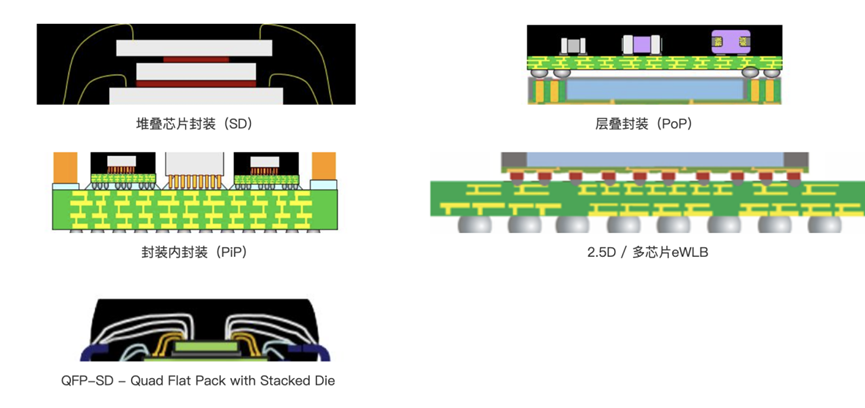

目前先进封装中按照主流可分为2D封装、2.5D封装、3D封装三种类型。

2D封装

2D封装是指在基板的表面水平安装所有芯片和无源器件的集成方式。2D封装上包括FOWLP、FOPLP等技术。

物理结构

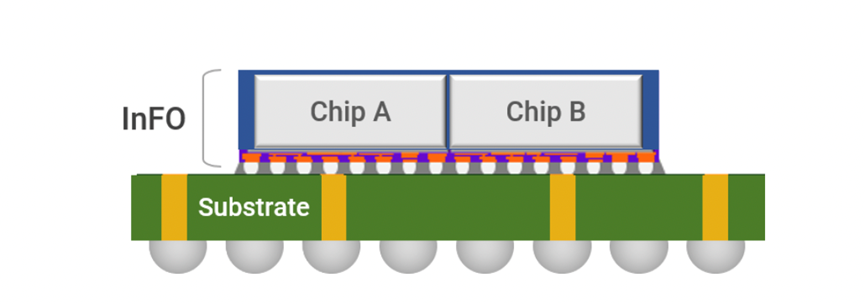

台积电的InFO:

台积电在2017年开发的InFO技术。InFO技术与大多数封装厂的Fan-out类似,可以理解为多个芯片Fan-out工艺的集成,主要区别在于去掉了silicon interposer,使用一些RDL层进行串连(2016年推出的iPhone7中的A10处理器,采用台积电16nm FinFET工艺以及InFO技术)。

日月光的eWLB:与台积的InFO类似,都属于Fan-out技术

另外,还有一种2D+ 集成

2D+集成是指的传统的通过键合线连接的芯片堆叠集成

主要基于以下两点原因

1

2

物理结构

电气连接

2.5D封装

2.5D封装通常是指既有2D的特点,又有部分3D的特点,其中的代表技术包括英特尔的EMIB、台积电的CoWoS、三星的I-Cube。

物理结构

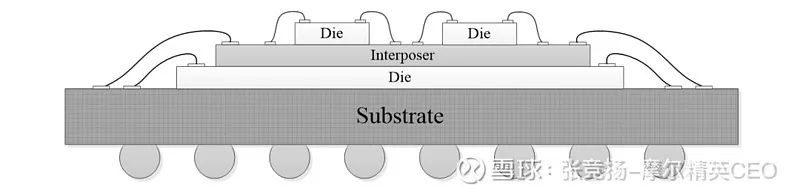

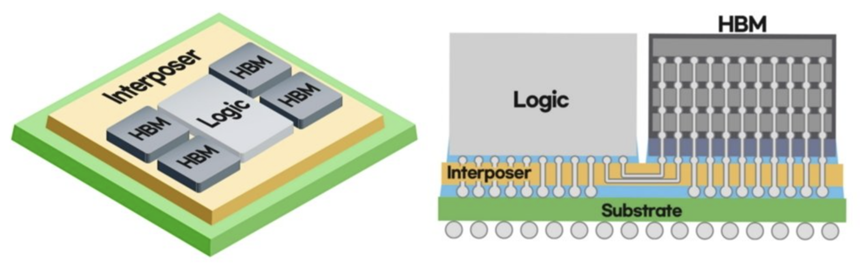

2.5D集成的关键在于中介层Interposer

所谓的TSV 指的是:

硅中介层有TSV的集成是最常见的一种2.5D集成技术,芯片通常通过MicroBump和中介层相连接,作为中介层的硅基板采用Bump和基板相连,硅基板表面通过RDL布线,TSV作为硅基板上下表面电气连接的通道,这种2.5D集成适合芯片规模比较大,引脚密度高的情况,芯片一般以FlipChip形式安装在硅基板上。

有TSV的2.5D集成示意图:

硅中介层无TSV的2.5D集成的结构一般如下图所示

无TSV的2.5D集成示意图:

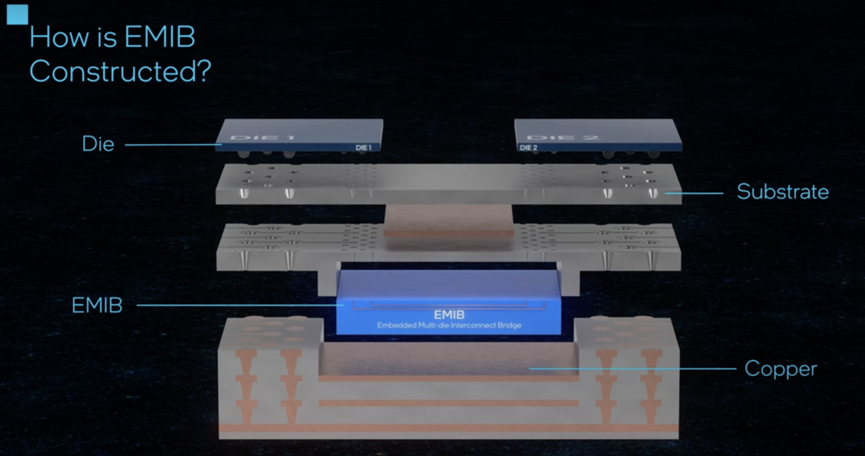

英特尔的EMIB:

概念与2.5D封装类似,但与传统2.5D封装的区别在于没有TSV。也正是这个原因,EMIB技术具有正常的封装良率、无需额外工艺和设计简单等优点。

台积电的CoWoS技术

台积电的CoWoS技术也是一种2.5D封装技术。根据中介层的不同可以分为三类,一种是CoWoS_S使用Si衬底作为中介层,另一种是CoWoS_R使用RDL作为中介层,第三种是CoWoS_L使用小芯片(Chiplet)和RDL作为中介层。

台积电InFO(2D)与CoWoS(2.5D)之间的区别在于,CoWoS针对高端市场,连线数量和封装尺寸都比较大;InFO针对性价比市场,封装尺寸较小,连线数量也比较少。

第一代CoWoS主要用于大型FPGA。CoWoS-1的中介层芯片面积高达约800mm²,非常接近掩模版限制。第二代CoWoS通过掩模拼接显着增加了中介层尺寸。台积电最初符合1200mm²的要求,此后将中介层尺寸增加到1700mm²。这些大型封装称为CoWoS-XL2。

最近,台积电公布的第五代CoWoS-S的晶体管数量将增加20倍,中介层面积也会提升3倍。第五代封装技术还将封装8个128G的HBM2e内存和2颗大型SoC内核。

长电科技XDFOI技术:

相较于2.5D TSV封装技术,具备更高性能、更高可靠性以及更低成本等特性。该解决方案在线宽或线距可达到2um的同时,可实现多层布线层,另外,采用了极窄节距凸块互联技术,封装尺寸大,可集成多颗芯片、高带宽内存和无源器件。

三星的I-Cube

三星的具有的先进封装包括I-Cube、X-Cube、R-Cube和H-Cube四种方案。其中,三星的I-Cube同样也属于2.5D封装。

3D封装

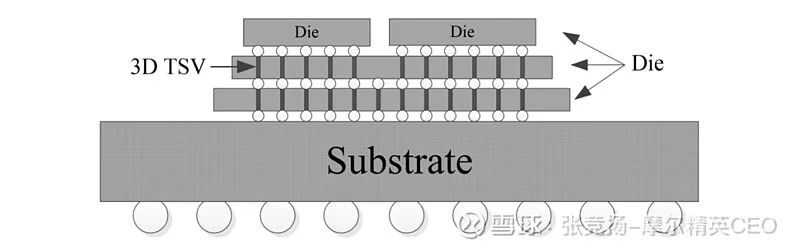

3D封装和2.5D封装的主要区别在于:2.5D封装是在Interposer上进行布线和打孔,而3D封装是直接在芯片上打孔和布线,电气连接上下层芯片。3D集成目前在很大程度上特指通过3D TSV的集成。

3D集成和2.5D集成的主要区别在于

物理结构

电气连接

3D集成大多数应用在同类芯片堆叠中

同类芯片的3D集成示意图:

不同类芯片的3D集成中

台积电的SoIC技术:

台积电SoIC技术属于3D封装,是一种晶圆对晶圆(Wafer-on-wafer)的键合技术。SoIC技术是采用TSV技术,可以达到无凸起的键合结构,把很多不同性质的临近芯片整合在一起,而且当中最关键、最神秘之处,就在于接合的材料,号称是价值高达十亿美元的机密材料。

SoIC技术将同质和异质小芯片集成到单个类似SoC的芯片中,具有更小尺寸和更薄的外形,可以整体集成到先进的WLSI(又名CoWoS和InFO)中。从外观上看,新集成的芯片就像一个通用的SoC芯片,但嵌入了所需的异构集成功能。

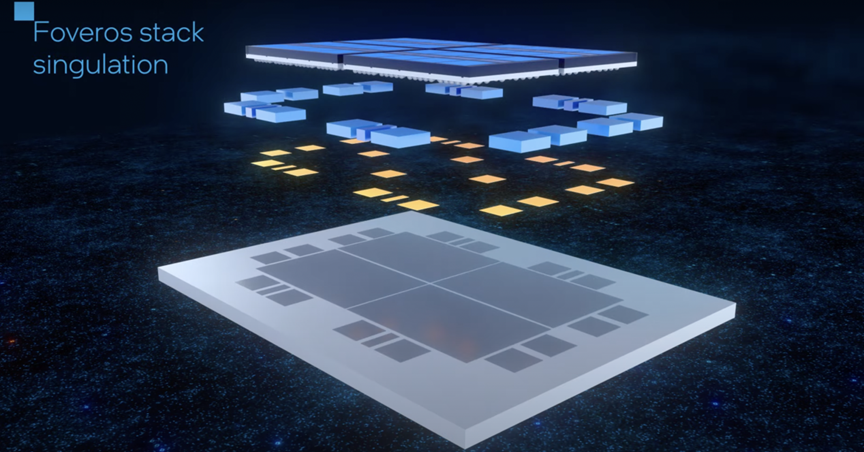

英特尔的Foveros技术:

从3D Foveros的结构上看,最下边是封装基底,之上安放一个底层芯片,起到主动中介层的作用。在中介层里有大量的TSV 3D硅穿孔,负责联通上下的焊料凸起,让上层芯片和模块与系统其他部分通信。

三星的X-Cube 3D封装技术:

使用TSV工艺,目前三星的X-Cube测试芯片已经能够做到将SRAM层堆叠在逻辑层之上,通过TSV进行互联,制程是他们自家的7nm EUV工艺。

长电科技的扩展eWLB:

长电科技基于eWLB的中介层可在成熟的低损耗封装结构中实现高密度互连,提供更高效的散热和更快的处理速度。3D eWLB互连(包括硅分割)是通过独特的面对面键合方式实现,无需成本更高的TSV互连,同时还能实现高带宽的3D集成。

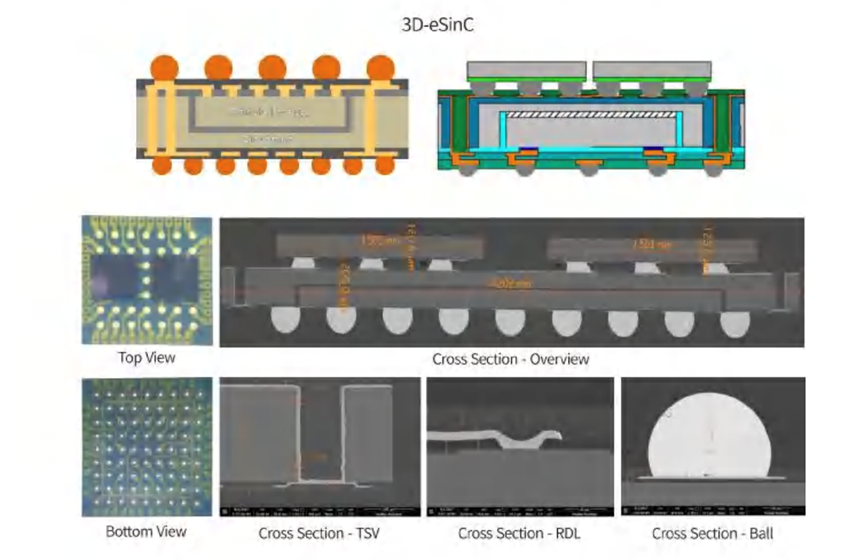

华天科技的3D-eSinC解决方案:

华天科技称,2022年将开展2.5D Interpose FCBGA、FOFCBGA、3D FOSiP等先进封装技术,以及基于TCB工艺的3D Memory封装技术,Double Sidemolding射频封装技术、车载激光雷达及车规级12英寸晶圆级封装等技术和产品的研发。

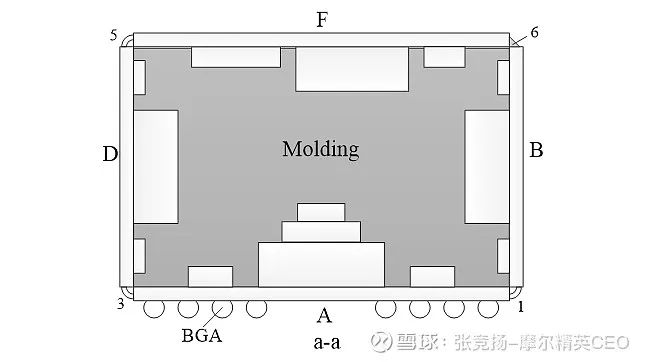

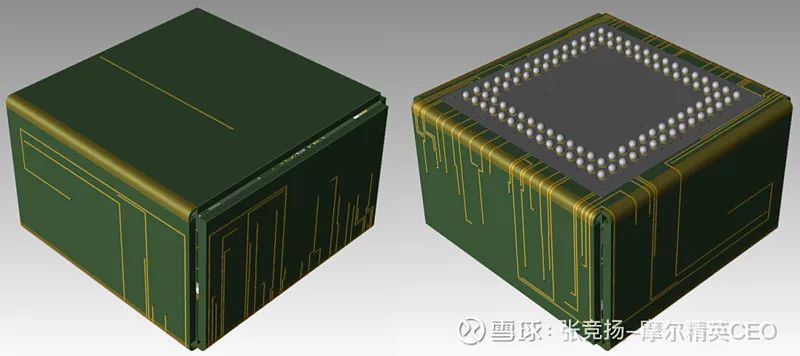

4D集成

物理结构

基于刚柔基板的4D集成示意图:

4D集成定义主要是关于多块基板的方位和相互连接方式

转自:雪球:张竞扬-摩尔精英CEO

© 滤波器 微信公众号