今日光电

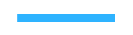

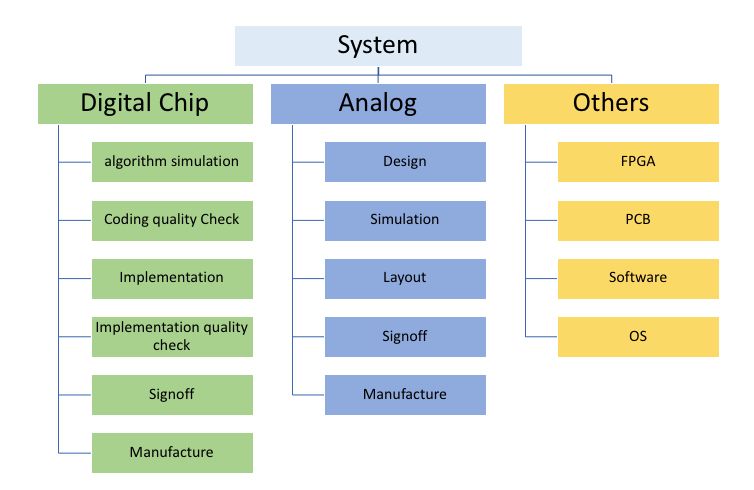

于消费者而言,一个可以使用的系统,有数字集成电路部分、模拟集成电路部分、系统软件及上层应用部分。关于各个部分的功能,借用IC 咖啡胡总的精品图可以一目了然。外部世界是一个模拟世界,故所有需要与外部世界接口的部分都需要模拟集成电路,模拟集成电路将采集到的外部信息转化成0/1 交给数字集成电路运算处理,再将数字集成电路运算处理完的信号转化成模拟信号输出;而这一切的运算过程都是在系统软件的号令跟监控下完成的,故曰:芯片是骨架,系统软件是灵魂。

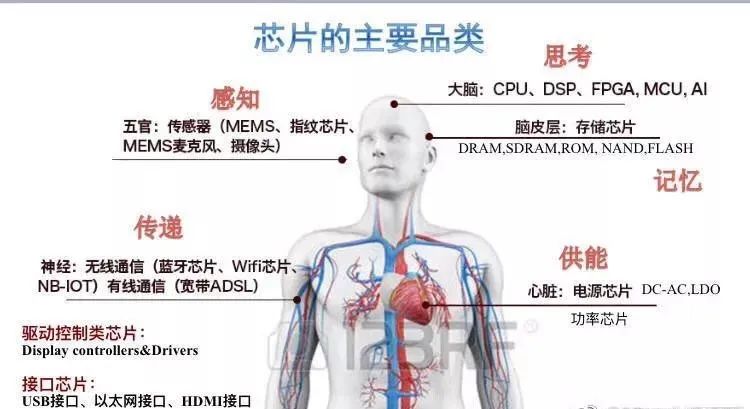

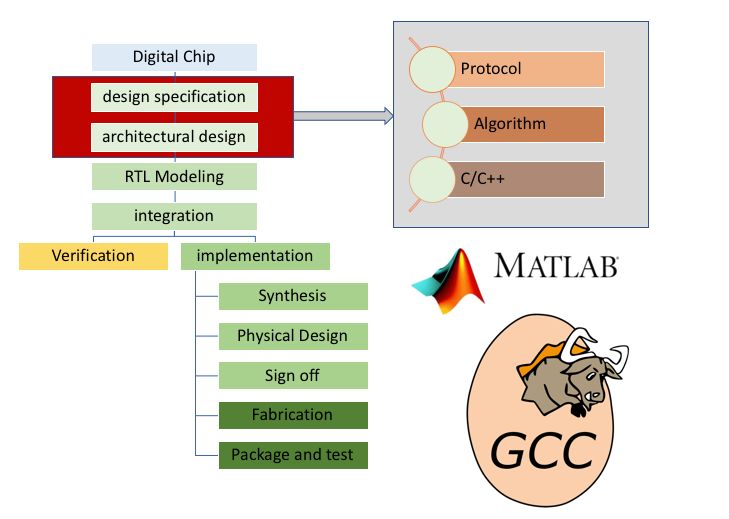

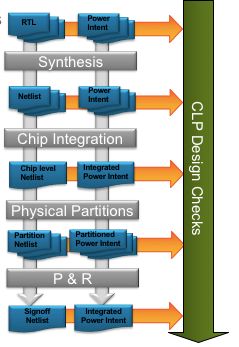

数字集成电路设计实现流程是个相当漫长的过程,拿手机基带芯片为例,对于3G, 4G, 5G, 工程师最初见到的是无数页的协议文档。架构师要根据协议来确定:协议的哪些部分可以用软件实现,哪些部分需要用硬件实现;算法工程师要深入研读协议的每一部分,并选定实现所用算法;芯片设计工程师,需要将算法工程师选定的算法,描述成RTL; 芯片验证工程师,需要根据算法工程师选定的算法设计测试向量,对RTL 做功能、效能验证;数字实现工程师,需要根据算法工程师和设计工程师设定的目标PPA 将RTL 揉搓成GDS; 芯片生产由于太过复杂,完全交由代工厂完成,封装亦是;对于测试,大部分公司都是租借第三方测试基台由自己的测试工程师完成,只有少部分土豪公司才会有自己的测试基台。

一颗芯片,性能的60% 取决于架构师,在国内好的架构师不超过三位数,极好的架构师不超过两位数,架构师是芯片灵魂的缔造者,是食物链的最顶端,是牛逼闪闪的存在,就驴浅显认知,除了office 似乎没有EDA 工具用于架构设计;架构敲定了之后,大量的算法工程师跟上,对于协议规定的每个点,都要选择适当的算法,用C/C++ 做精确模拟仿真,要确保功能、精度、效率、吞吐量等指标,Matlab 跟GCC 应该是他们使用最多的工具。

设计工程师根据算法工程师经过反复模拟仿真选择的算法,将抽象描述或定点C 转换成RTL, 在设计过程中需要反复仿真、综合,以确定设计功能的正确性,跟设计能达到的PPA. 除了RTL, 设计工程师还需要根据设计目标编写SDC 和power intent, 并做对应的质量检查。设计工程师需要使用大量EDA 工具:

编辑器:VIM, emac;

Lint : RTL 质量检查,Spyglass, Jasper;

CDC: SDC 质量检查,Spyglass, Conformal, GCA;

CPF/1801: power intent 质量检查,CLP;

Power: RTL 级功耗分析,Joules, PA;

仿真器:C, S, M 三家都有各自的仿真工具;

综合:Genus, DC;

接着捋,实际项目中验证跟综合从RTL coding 开始就会交叉进行,反复迭代。

语言:各种脚本语言之外,C/C++, SystemVerilog, Verilog;

协议:各种接口协议,各种通信协议,各种总线协议;

工具:动态仿真工具,静态仿真工具,FPGA, Emulator;

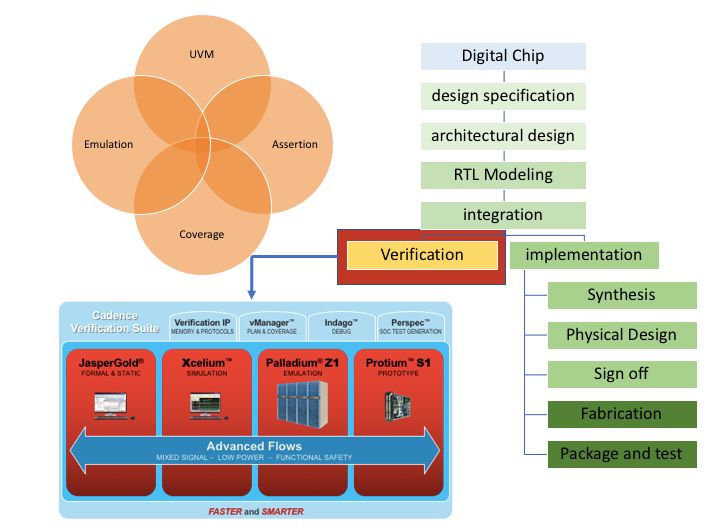

Static Verification: Jasper Gold 是C 家新近推出的静态验证工具,驴所理解的静态验证是基于断言的验证方法学,所谓静态即不需要输入测试激励,验证过程是纯数学行为。

Dynamic Verification: Xcelium 是C 家的动态验证工具,驴所理解的动态验证是基于UVM 的验证方法学,通过输入测试激励,监控仿真结果,分析覆盖率完成功能验证。

Emulator: 硬件仿真加速器,粗暴理解:有debug 功能的集成了丰富接口的巨型可编程阵列;特点:超高速验证、支持系统软件调试。帕拉丁是C 家在验证领域的明星产品,是行业翘楚,据说常有钦差莅临硅厂在帕拉丁前驻足良久,赏其外形之美,赞其功能之强。

Verification IP:验证需要各种验证模型,各种IP, 各种总线,各种高速接口。

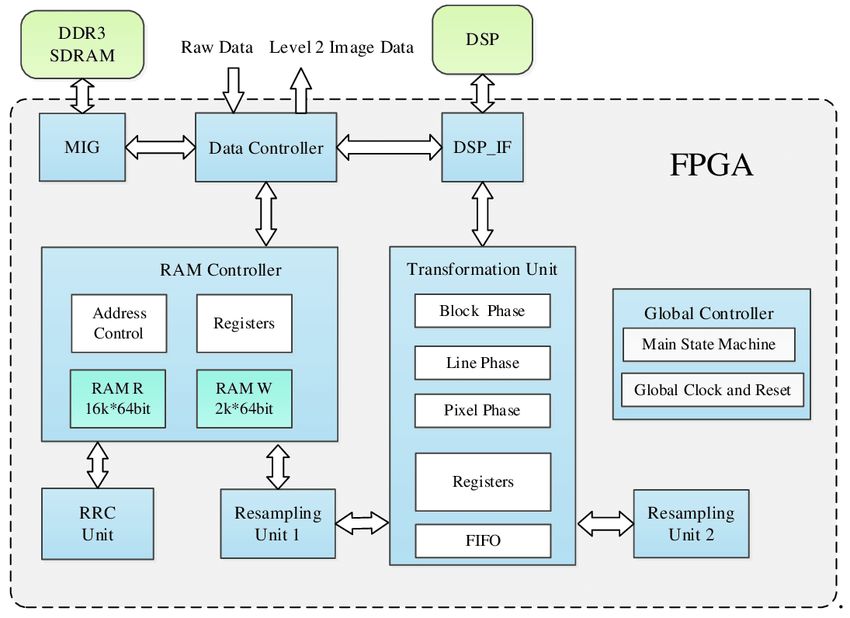

FPGA 的一大应用是验证,故提一嘴。在世上曾经有两家牛逼闪闪的FPGA 公司,一家是Altera 另一家是Xilinx, 后来Altera 像Mentor 一样找了个大爷把自己卖了。FPGA 内除了可编程逻辑之外,通常还会集成各种IP, 如CPU, DSP, DDR controller 等。每家FPGA 都有各种配置,根据集成的IP, 可编程逻辑的规模,可达到的速度,价格相差极大。相对于ASIC, FPGA 也有一套对应的EDA 工具,用于综合、布局布线、烧录、调试。如:Synplify, Quartus。

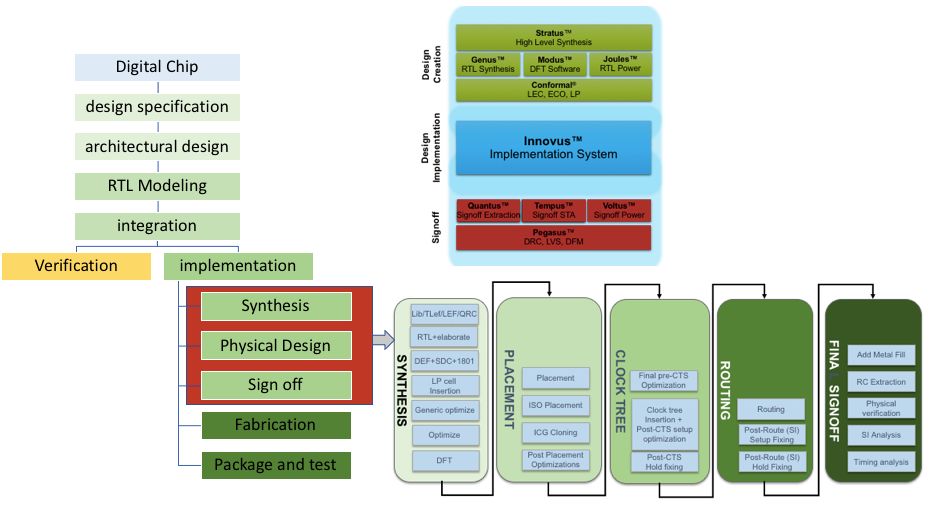

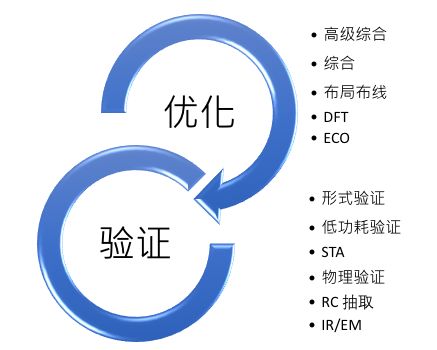

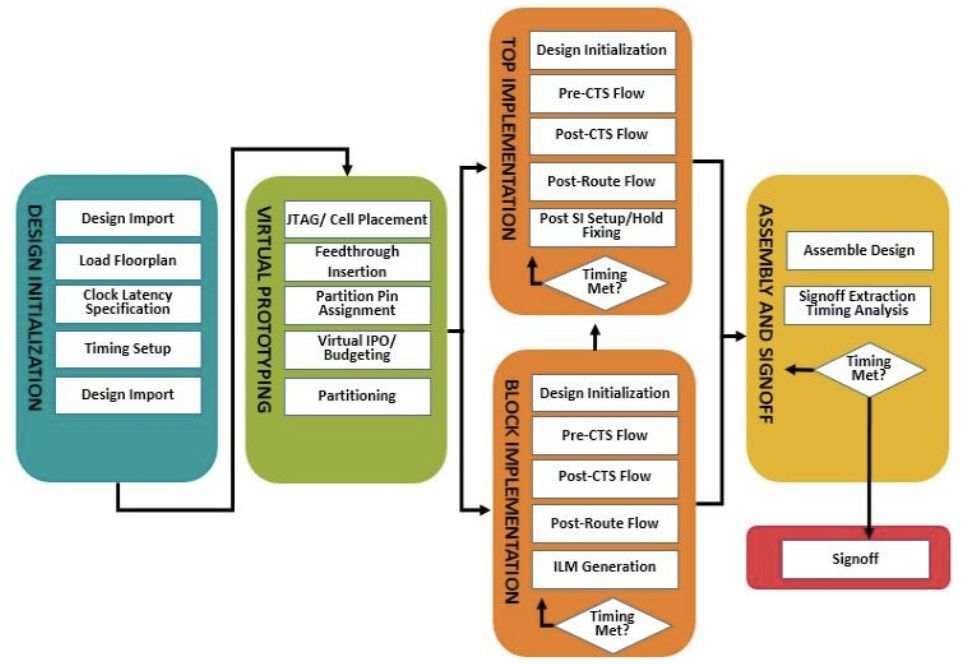

接着上面说的我们继续捋数字芯片设计实现流程,今天进入实现阶段,对于这一段驴只熟悉其中的综合、形式验证、低功耗验证、RTL 功耗分析、STA, 其他部分都是一知半解,故无深究,只捋流程。

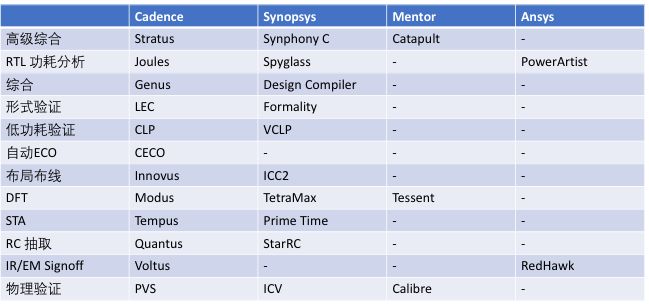

整个实现阶段,可以概括成玩EDA 工具及基于EDA 工具的方法学,EDA 工具无疑是实现阶段的主导,一颗芯片做得好不好,在实现阶段之前基本取决于工程师的能力强不强,而在实现阶段之后基本取决于EDA 工具玩得好不好。整个设计实现流程,涉及到许多工具,此处列出四家主要参与者,空白部分不代表没有,只代表驴不知。

高级综合:所谓的高级综合就是将C/ C++/ System C描述的设计意图,“翻译”成用Verilog/ System Verilog 描述的RTL, 多应用于运算逻辑主导的设计,除了三巨头,市面上有许多小公司在这一个点上也做得不错。

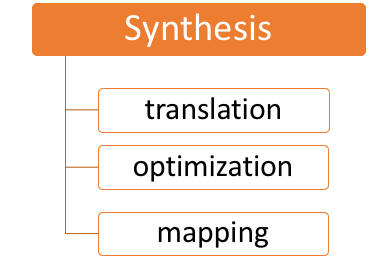

综合:在实现流程中,就背后算法而言,综合一定是最难最复杂的。综合首先将Verilog/ System Verilog/ VHDL 描述的逻辑转化成由Gtech 描述的逻辑,再对Gtech 逻辑做优化,优化后再将Gtech 描述映射到对应工艺库。其中优化过程涉及到多个方面,近年来EDA 工具的发展方向基本可以概括为:容量,速度,相关性。容量:指可处理的设计规模;速度:指EDA 工具的优化速度;相关性:指跟布局布线之间的相关性。主流工具:Genus, Design Compiler. 在这一点上,几乎再难有后起之秀,除非有朝一日,整个数字电路的设计方法学发生颠覆性的革新。

硅农:Innovus 请解析A 文件,按设定目标做个功耗最优的结果;

Innovus: 已读取目标文件,根据设计数据分析,本设计大概需要250G 内存,在5小时内完成,请选择任务完成后是否自动进入后续程序......

申明:感谢原创作者的辛勤付出。本号转载的文章均会在文中注明,若遇到版权问题请联系我们处理。

----与智者为伍为创新赋能----

联系邮箱:uestcwxd@126.com

QQ:493826566