在使用具有超快边缘速率的理想半导体开关时,我们会遇到电压过冲和振铃问题。了解面向 SiC FET 的简单 RC 缓冲电路如何解决这些挑战并进一步提高效率。

这篇博客文章最初由 United Silicon Carbide (UnitedSiC) 发布,该公司于 2021 年 11 月加入 Qorvo 大家庭。UnitedSiC 是一家领先的碳化硅 (SiC) 功率半导体制造商,它的加入促使 Qorvo 将业务扩展到电动汽车 (EV)、工业电源、电路保护、可再生能源和数据中心电源等快速增长的市场。

当您询问电源转换器设计人员有关半导体开关的要求时,他们可能会这样回答:“低导通电阻、高断开电阻以及两种状态之间尽可能快速的过渡。”简单地说,他们想要实现更低的功耗。SiC FET非常接近这种理想状态,其750V 级别的导通电阻不到 6 毫欧,边缘速率在纳秒范围内,而且在多千瓦范围内,转换器和逆变器的效率有望超过 99.5%。

如果稍加思考,设计人员还会 “顺便” 提出其他一些要求,比如:简单的栅极驱动、较高的额定电压、有效的第三象限运行、较高的雪崩能量和短路额定值、较低的热阻、较低的系统成本等。幸运的是,SiC FET 刚好具有这些基本特性,而且其品质因数也十分出色。

但设计人员将 SiC FET 放在电路测试板中以最高边缘速率进行测试时,电路板却冒烟了。“当时的电源电压远低于最大值,且只有轻负载!”但是当时的线路电感和连接电感是多少呢?根据我们熟悉的方程式 V = -L.di/dt,在电感仅为 100nH 的情况下,较高的电流边缘速率 3000A/µs 会产生 300V 的电压尖峰,同时会在 SiC FET 失效前的短时间内,给开关施加应力并触发持续数微秒的高频振铃,从而抑制本地无线电接收。

所以说,除非我们努力实现零连接电感,或疯狂地过度指定额定开关电压,并支持强电磁干扰滤波,否则就得控制边缘速率,并抑制振铃。一直以来,限制电压尖峰的传统方法是增加串联栅极电阻 RG(OFF),但这种方法也并非万全之策。增加栅极电阻会给栅极驱动波形带来延迟,从而限制占空比和高频运行——这便能体现出宽带隙开关的其中一个主要优势。此外,栅极电阻还会显著增加开关损耗,且对振铃也几乎没有什么影响。

更优的解决方案是使用简单的 RC 缓冲电路。您可能会对使用 IGBT 时通常需要大型热电阻-电容网络的想法心存疑虑,但对于 SiC FET 来说,情况就不一样了。那个想法主要是希望减少连接电感与器件电容之间的谐振,而使用 SiC FET 时的谐振非常低。这意味着,通常只需 200pF 左右的电容(2 倍或 3 倍 Coss(er))以及几欧姆的串联电阻即可提供阻尼。缓冲电阻会耗散一些功率,但该网络可减少硬开关和软开关应用中的关断电压和电流的重叠,所以这种转换的损耗实际上比较小。

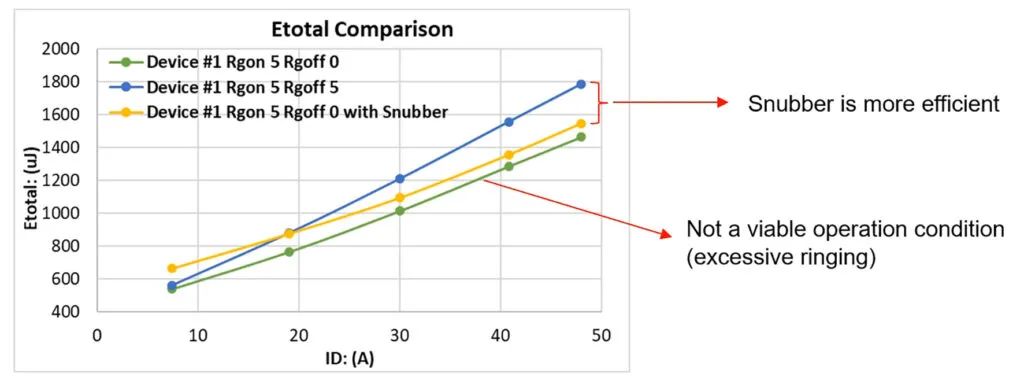

缓冲电路在导通时会耗散一些功率,因此综合考量,应考虑总损耗 E(ON) + E(OFF)。图中显示的是器件电阻为 40 毫欧时的 E(TOTAL)。蓝色线表示未使用缓冲电路,其 RG(ON) 和 RG(OFF) 均为 5 欧姆。黄色线表示采用了 200pF/10 欧姆的缓冲电路,其 RG(ON) 为 5 欧姆,RG(OFF) 为 0 欧姆。在 40kHz 条件下运行时,使用 40 A 缓冲电路的优势非常明显,功耗降低约为 10.9W。在轻负载应用中,情况正好相反,但这些水平的系统功耗较低。

缓冲电路是一个不错的解决方案,但是否不太方便实践呢?如果评估典型应用中缓冲电路电阻所吸收的能量,可能会以为每个周期大约吸收 120µJ,相当于在 40kHz 条件下超过了 5W。然而测试表明,电路导通时,大部分能量耗散在 SiC FET 信道中,因为转换过程发生在其信道的线性区域中,而不是在缓冲电路电阻中。这样一来,在缓冲电路中使用功率为 1W 的电阻通常就足够了,通常表面贴装型缓冲电路便能达到这一功率水平。而且电容器比较小。

如今,设计人员可以在其实现完美开关的愿望清单中愉快地勾选另一选项,即一种易于控制、成本低廉,可在不影响其他优势的情况下减少过冲和振铃的器件。

SiC FET

https://unitedsic.com/group/sic-fets/

750V 级别

https://info.unitedsic.com/gen4