本文来自恩智浦NXP社区。帖链接如下:https://www.nxpic.org.cn/module/forum/thread-622667-1-1.html

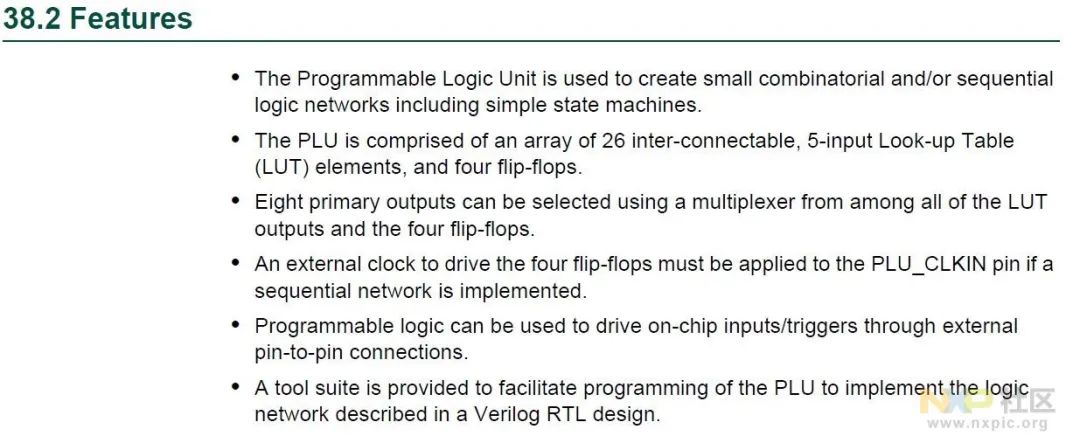

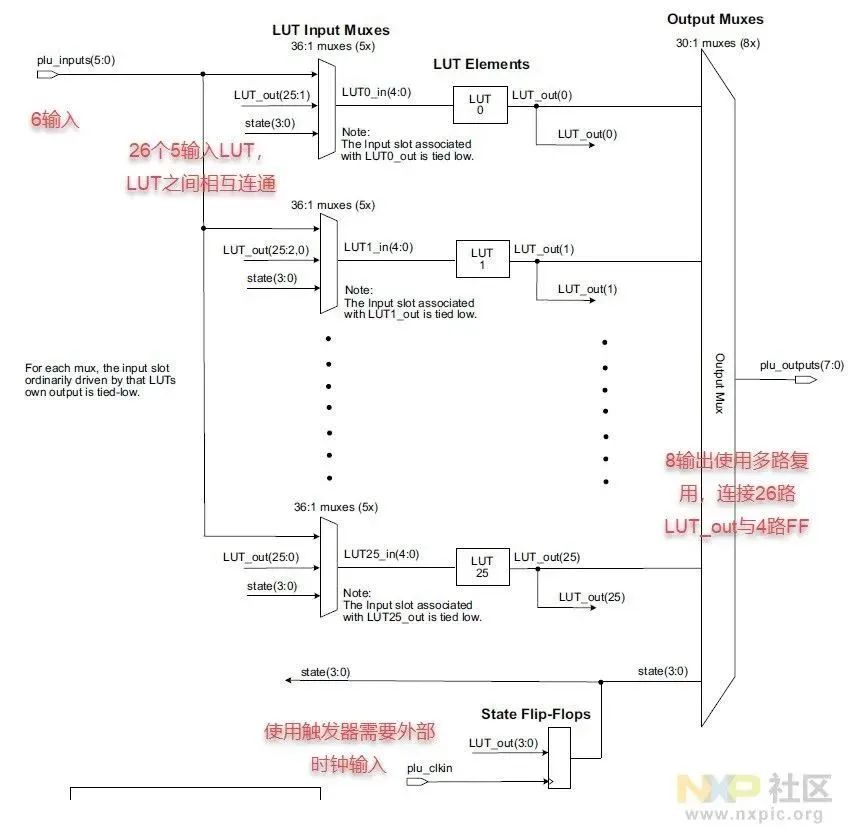

1、PLU简介

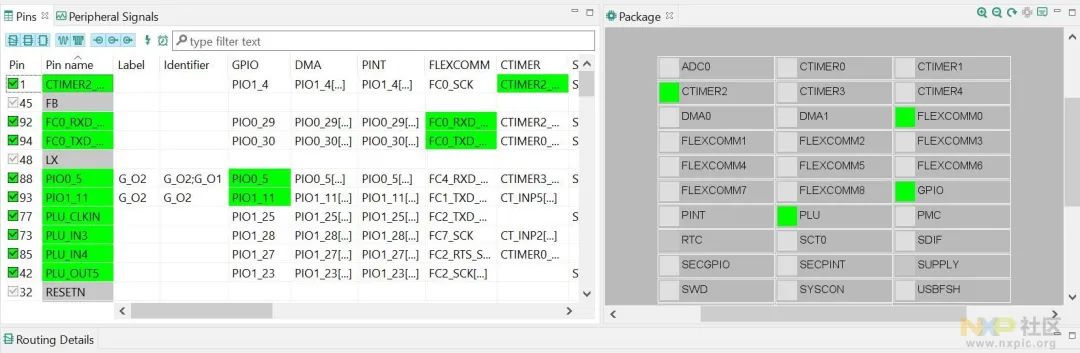

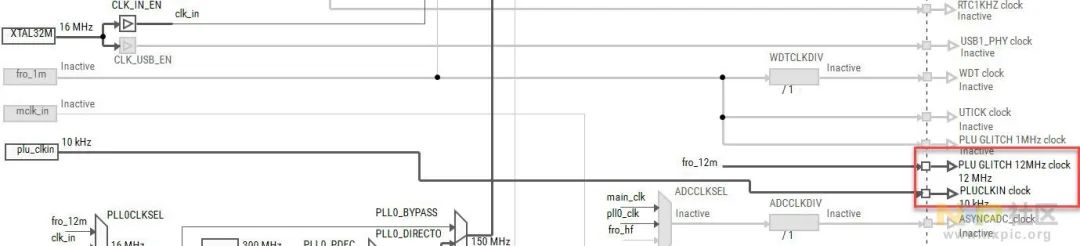

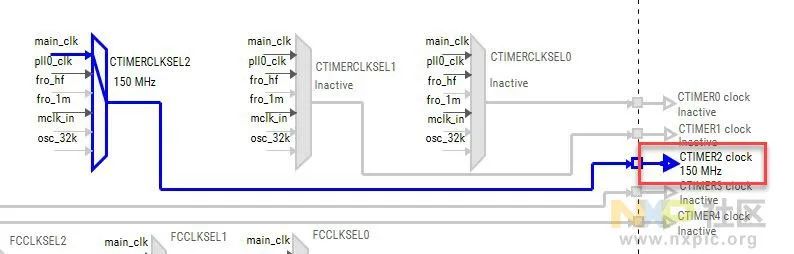

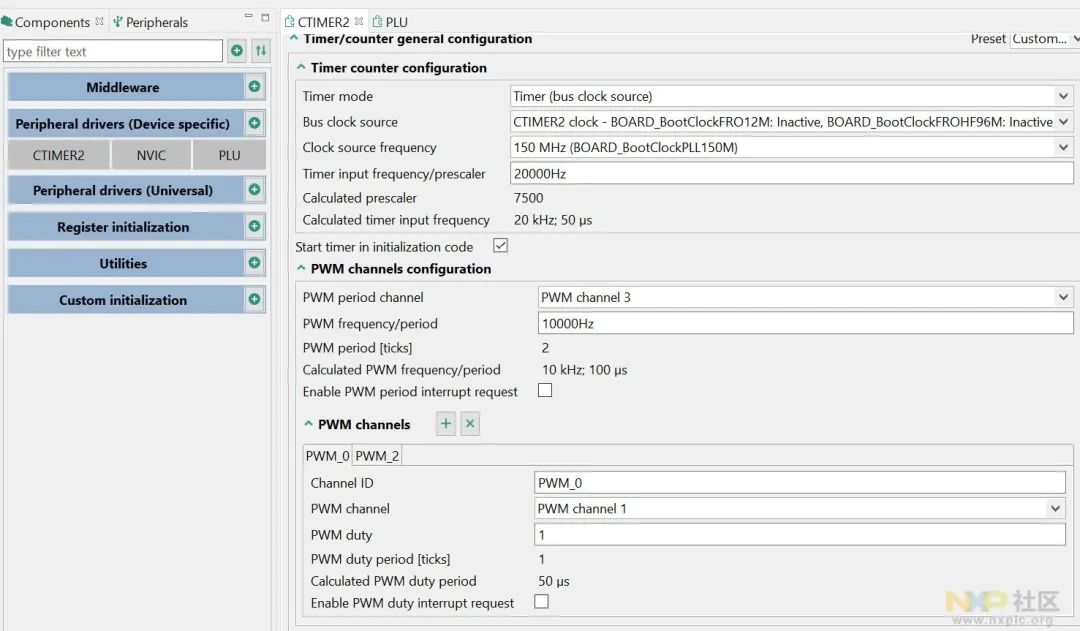

2、PLU配置

3、PLU Configuration tool 配置

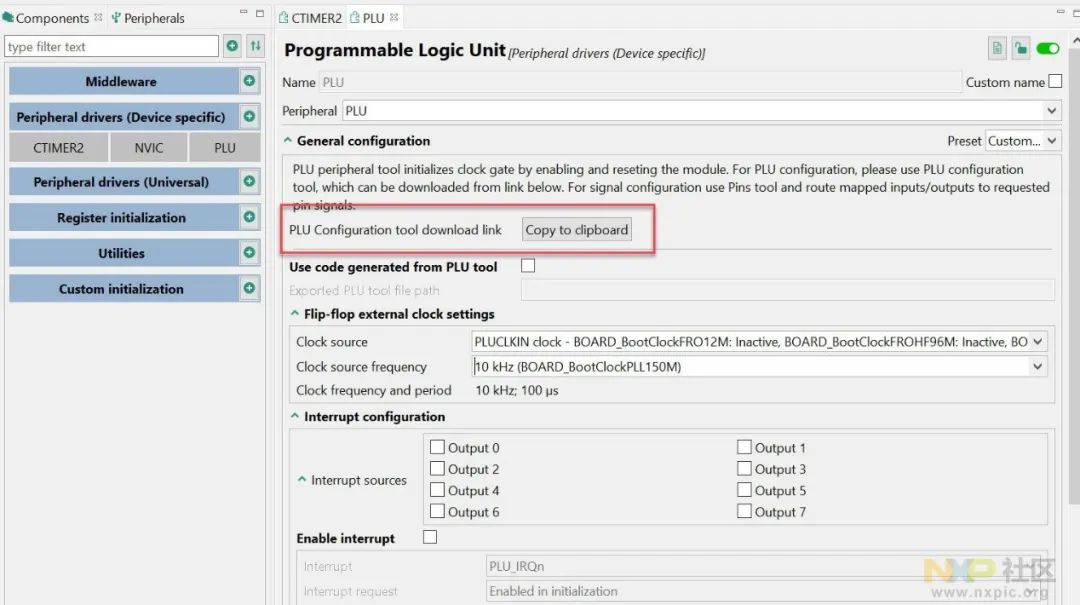

NXP开发了PLU Configuration tool,此工具可以根据数字逻辑电路生成对应代码,去配置PLU及其真值表,下载链接可以在PLU外设配置界面复制,链接如下:

https://www.nxp.com/mcu-plu-config-tool

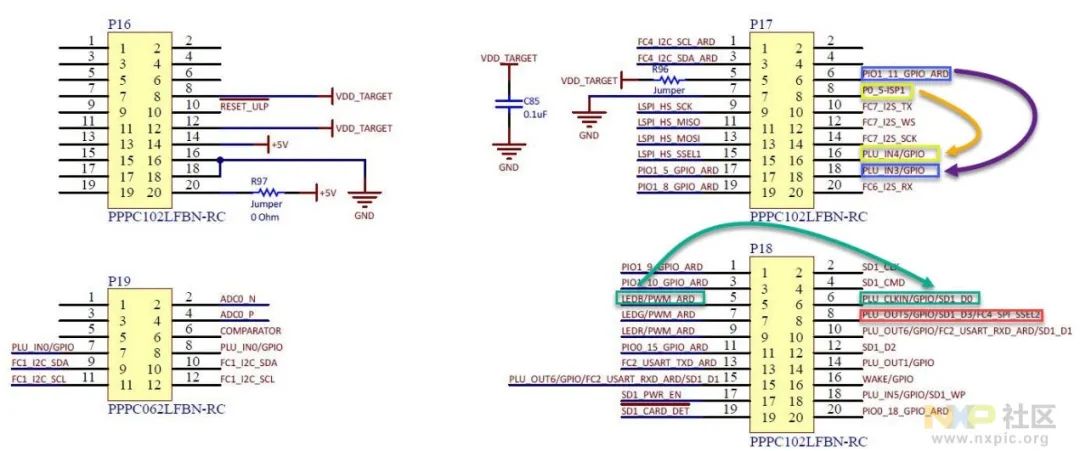

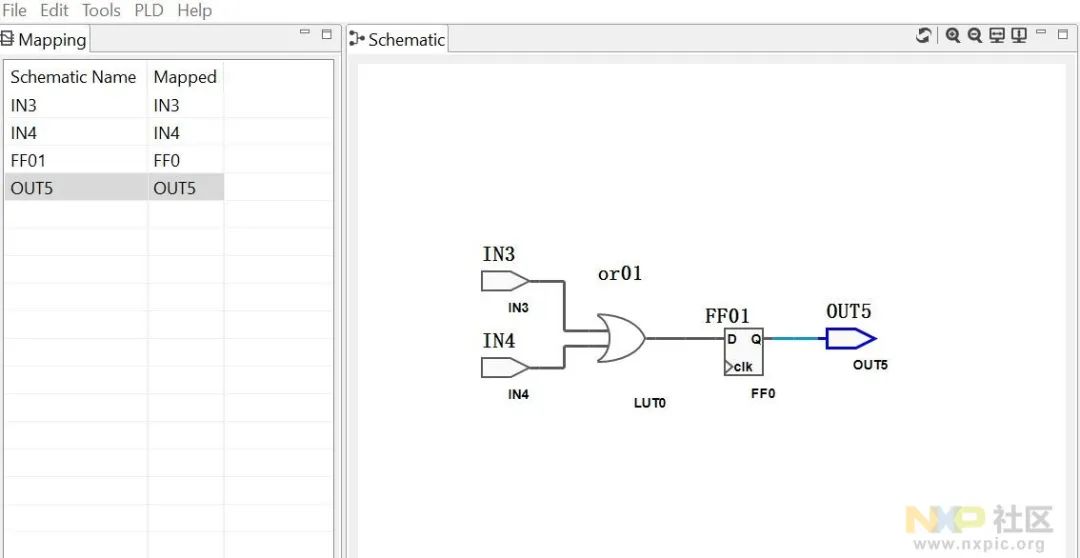

3.1 原理图配置

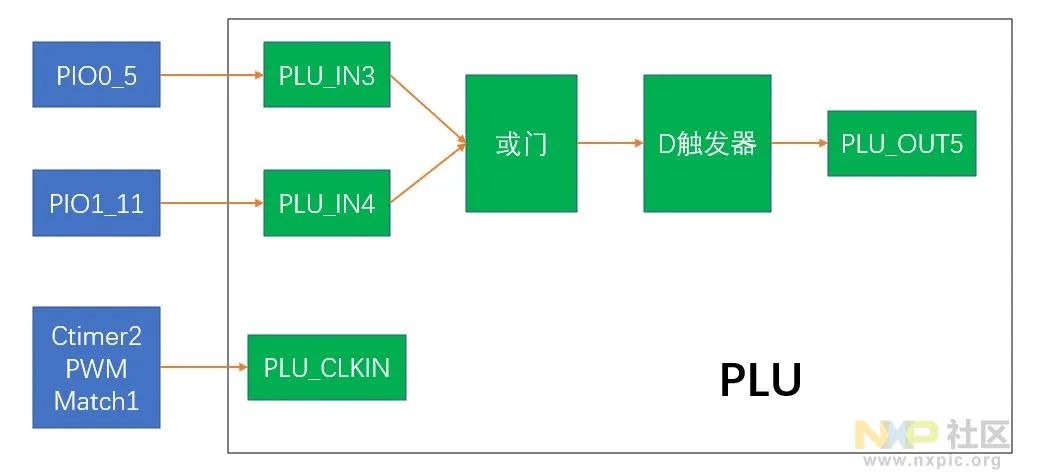

打开PLU配置工具,选择原理图设计,做一个简单的或运算与D触发器实验,如下:

/* LUT0 (or01) */

PLU->LUT[0].INP_MUX[0] = 0x00000003; /* IN3 (IN3) */

PLU->LUT[0].INP_MUX[1] = 0x00000004; /* IN4 (IN4) */

PLU->LUT[0].INP_MUX[2] = 0x0000003F; /* default */

PLU->LUT[0].INP_MUX[3] = 0x0000003F; /* default */

PLU->LUT[0].INP_MUX[4] = 0x0000003F; /* default */

PLU->LUT_TRUTH[0] = 0xeeeeeeee; /* or01 (or01) STD 2 INPUT OR */

PLU->OUTPUT_MUX[5] = 0x0000001a; /* FF0 (FF01) -> OUT5 */

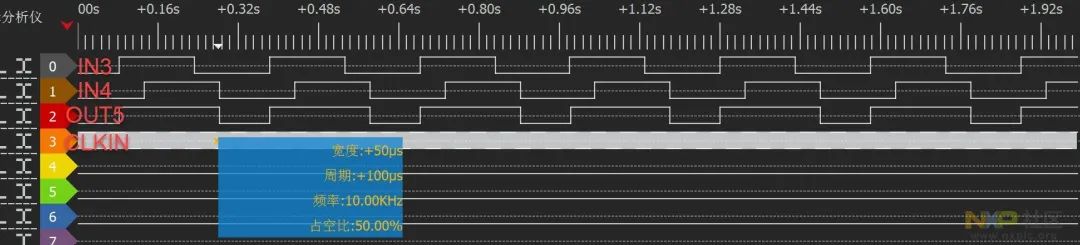

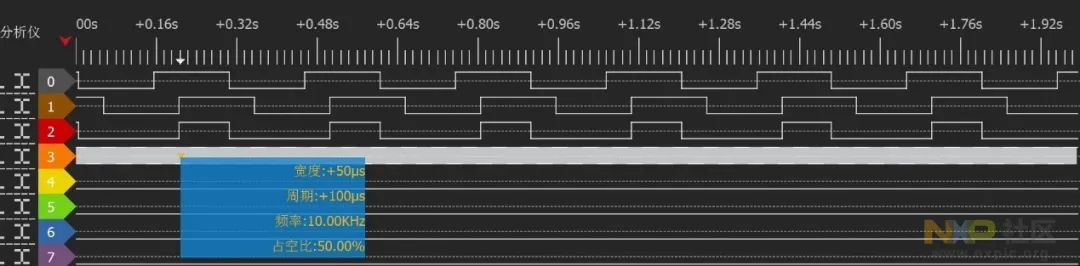

逻辑分析仪检测结果如下:

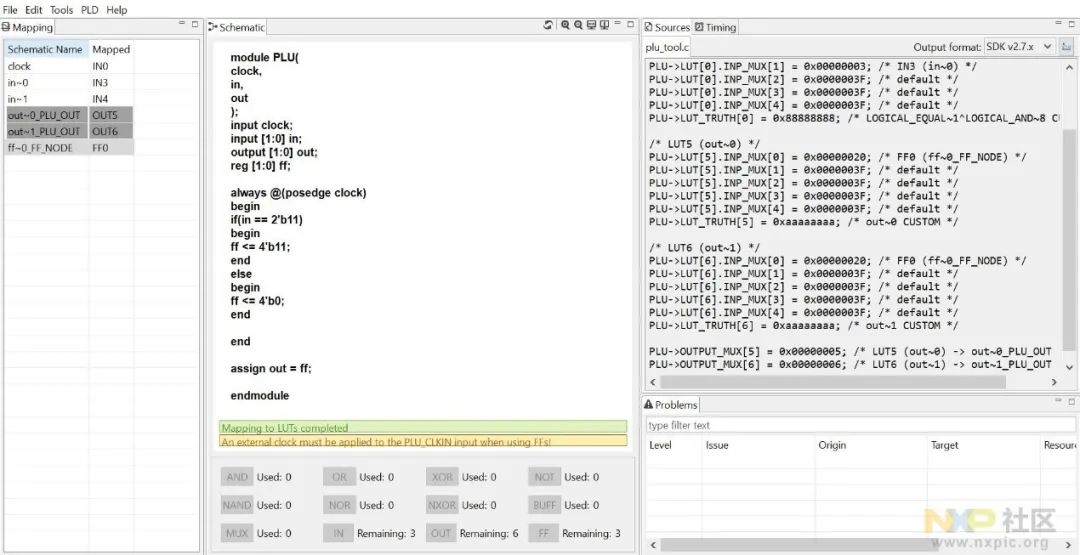

3.2Verilog配置

打开PLU配置工具,选择导入verilog文件,将写好的.v文件导入,做一个简单的与运算实验,如下:

注意只有在verilog文件中声明posedge clock才会使用到触发器,而且不能使用negedge sys_rst_n用来复位。always语句中的posedge clock将由CLKIN引脚的时钟输入代替,所以clock引脚是不起作用的。将生成的代码复制到main函数中,用逻辑分析仪测试的结果如下:

参考官方AN,如下:

https://www.nxp.com.cn/docs/en/application-note/AN13101.pdf

恩智浦MCU加油站

这是由恩智浦官方运营的公众号,着重为您推荐恩智浦MCU的产品信息、开发技巧、教程文档、培训课程等内容。

长按二维码,关注我们

END

更多恩智浦AI-IoT市场和产品信息,邀您同时关注“NXP客栈”微信公众号

NXP客栈

恩智浦致力于打造安全的连接和基础设施解决方案,为智慧生活保驾护航。

长按二维码,关注我们