随着3D-IC的制造工艺的不断发展,3D-IC的堆叠方式愈发灵活, 从需要基板作为两个芯片互联的桥梁,发展到如今可以做到多颗芯片灵活堆叠,芯片设计团队要实现质量最佳、满足工期要求、具有成本效益的设计,面临着如何建立正确的3D-IC 设计实现流程和如何实现设计数据&项目的高效管理的挑战。

解决这个挑战,就要求设计环境可以预先掌握设计意图、支持设计模型简化,进而达成系统的整体规划,获得系统级效应(如热和功耗)所提供的早期反馈,并透过实现和分析的无缝迭代达到同时兼顾芯片和封装效应的最佳系统设计效果。

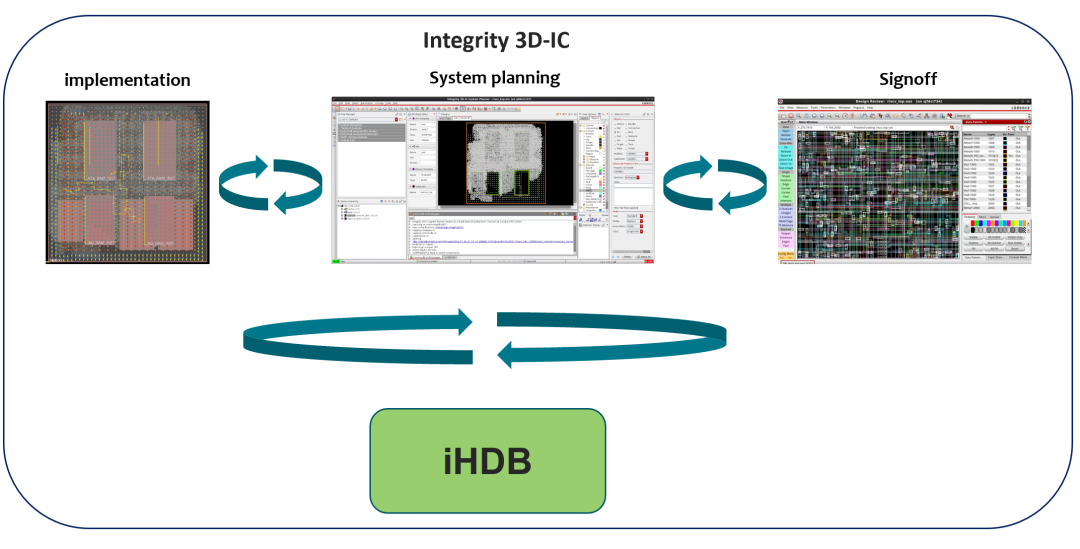

Integrity 3D-IC 平台具有强大的数据管理功能,能够实现跨团队的一键数据同步与更新。同时,Integrity 3D-IC支持灵活的3D-IC实现流程,配合其高效的数据管理机制,可以让用户在流程中的多个关键阶段接入内嵌的分析平台,进而实现整个系统的快速迭代和ECO。

通过系统规划器为 3D 系统提供独特的层次化设计和优化功能

通过与 Innovus™ Implementation System 基于 Tcl 的实时直接集成,提供完整的堆叠管理、芯片到封装的信号映射以及先进的 Bump 和 TSV 规划功能

高效的数据库,可对每一层堆叠结构进行层次化的多级表示

Integrity 3D-IC自底向上的实现流程

-顶层规划

-物理与逻辑连接的设计和优化

-物理实现的自动化流程

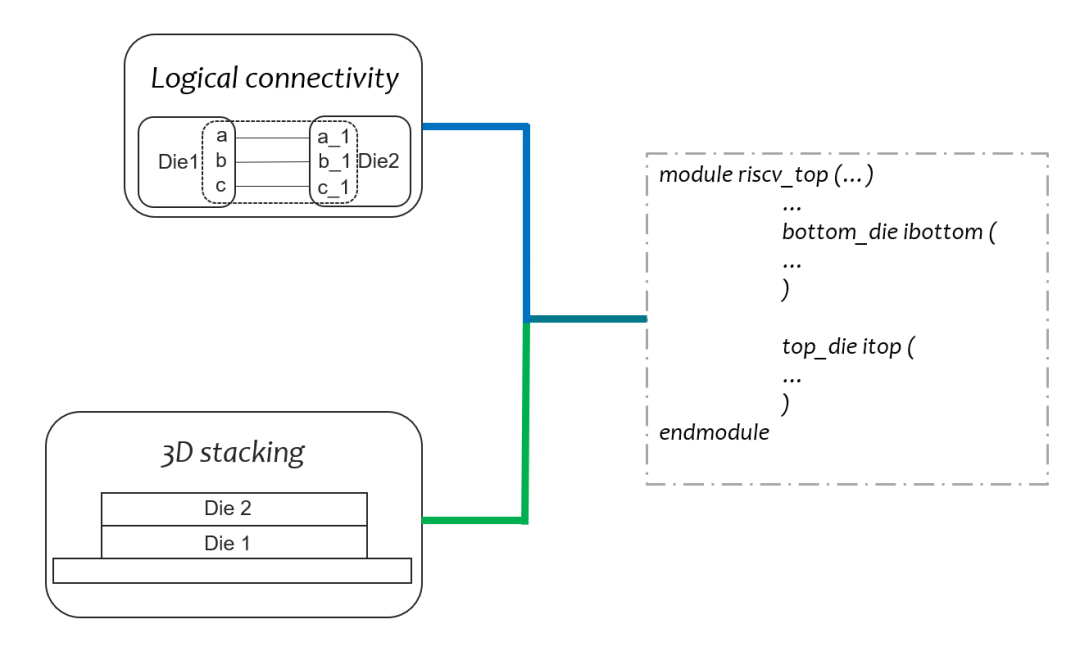

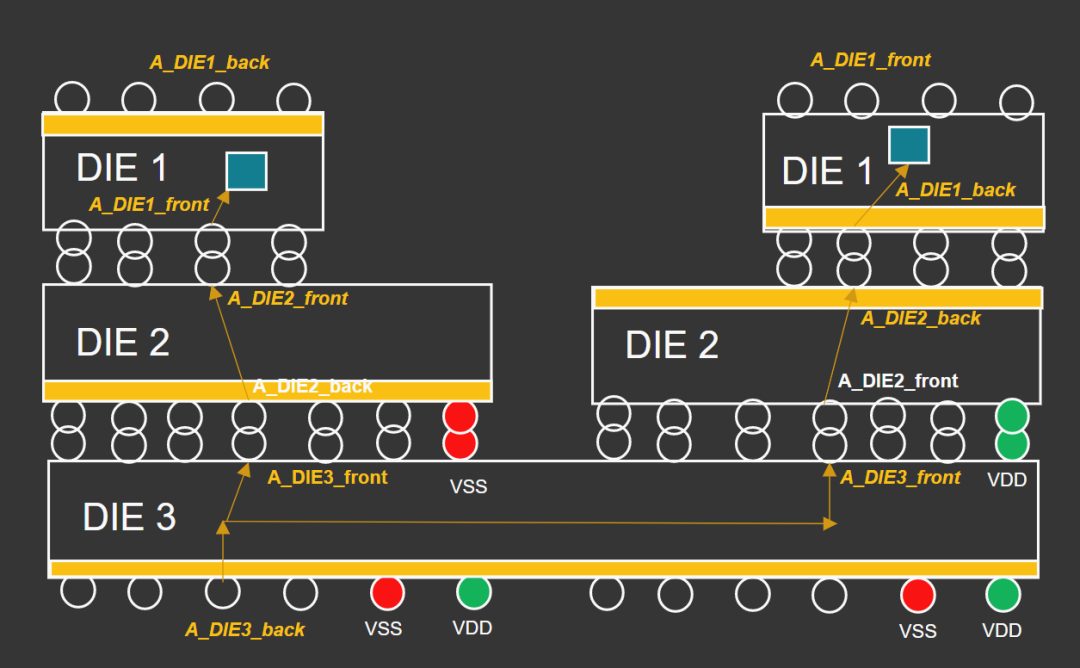

与传统的芯片层次化设计一样,3D-IC 的实现流程也有自底向上与自顶向下之分,但无论哪种方法,其目标都是将设计划分成若干个芯片的数据包分别做物理实现。Integrity 3D-IC 可以轻松将两个芯片的数据包组合,并且在此基础上完成3D系统的布局规划和片间互联优化。与此同时,Integrity 3D-IC 平台拥有多种针对Bump规划以及优化的新特性,帮助用户达成更高性能的设计。

顶层规划

当用户已经有芯片的数据包,无论该数据包处于原型阶段还是已部分物理实现,Integrity 3D-IC 均可以利用其建立3D-IC系统顶层的堆叠与连接。并且Integrity 3D-IC可以支持灵活的顶层逻辑描述格式:用户可以使用常规的verilog 网表或Integrity 3D-IC标准的连接描述文件格式,从而可以帮助用户快速将前端顶层系统设计转化为真实的顶层逻辑连接。

物理与逻辑连接的设计和优化

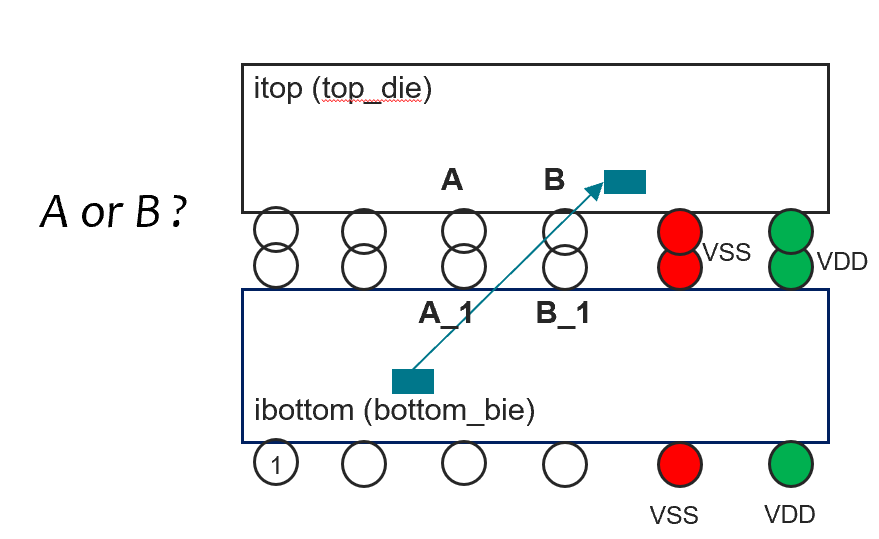

完成顶层设计后,我们需要对片间互联的Bump模式进行设计,并将信号与Bump关联以实现逻辑和物理的数据通路。通常这个过程需要跨团队多次迭代从而实现Bump数量和上下芯片间信号线长的平衡,这个迭代常常为了保留余量而过度设计,导致损失部分系统性能,如下图:

用户需要多次尝试以评估数据从A通道还是B通道传输才能得到最短的线长。当设计中存在数万乃至数十万个Bump的时候,这就变成一个难以完成的任务。

Integrity 3D-IC 可以根据设计的物理信息自动获得最优的信号与Bump关联方案, 帮助用户用最短的时间得到最佳的Bump pattern设计。与此同时,对于一些需要用户定制的数据通路,工具可以根据用户提供的映射关系将所需的信号与Bump准确的关联。这个特性可以让用户如同堆乐高积木一般实现多芯片堆叠和信号通路设计。

物理实现的自动化流程

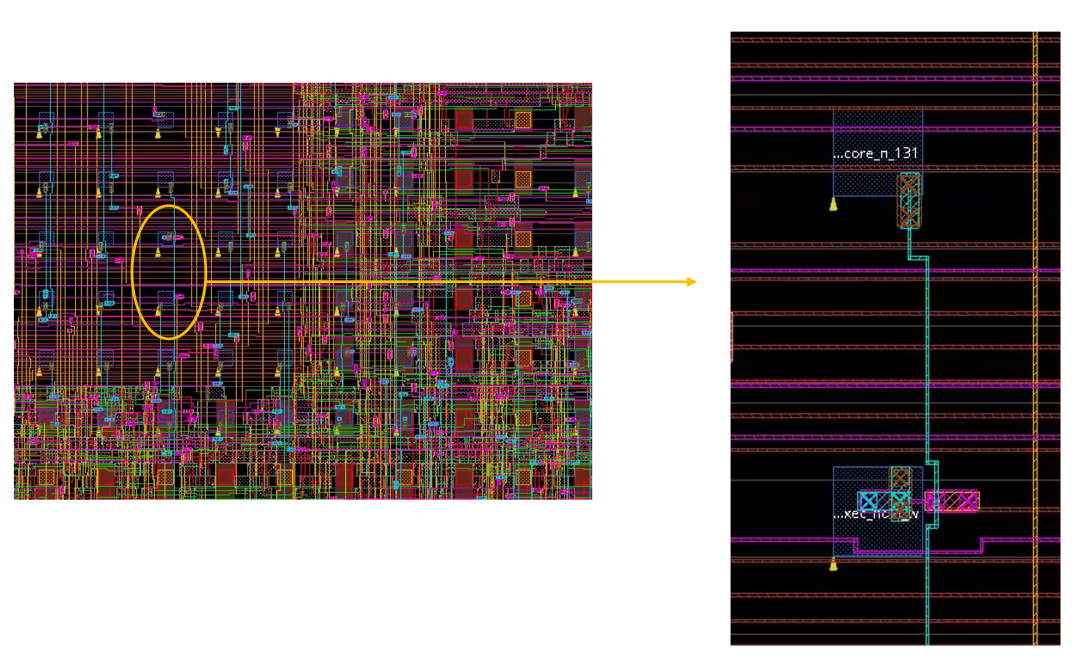

Integrity 3D-IC 支持完整的3D-IC 物理实现流程。工具已经将3DIC设计中所需要的特殊处理整合简化,如下图所示,对于用户而言,只需要在floorplan阶段针对Bump做标准流程处理,即可继续往下进行。而到了绕线的环节,工具的绕线引擎对于Bump的连接已经有着良好的支持,用户可以通过工具轻松的实现Bump 绕线自动化。如图所示,工具可识别出Bump的位置并正确的连线打孔。

Integrity 3D-IC的高效数据管理

-iHDB(Integrity Hierarchical Database)

-数据的同步

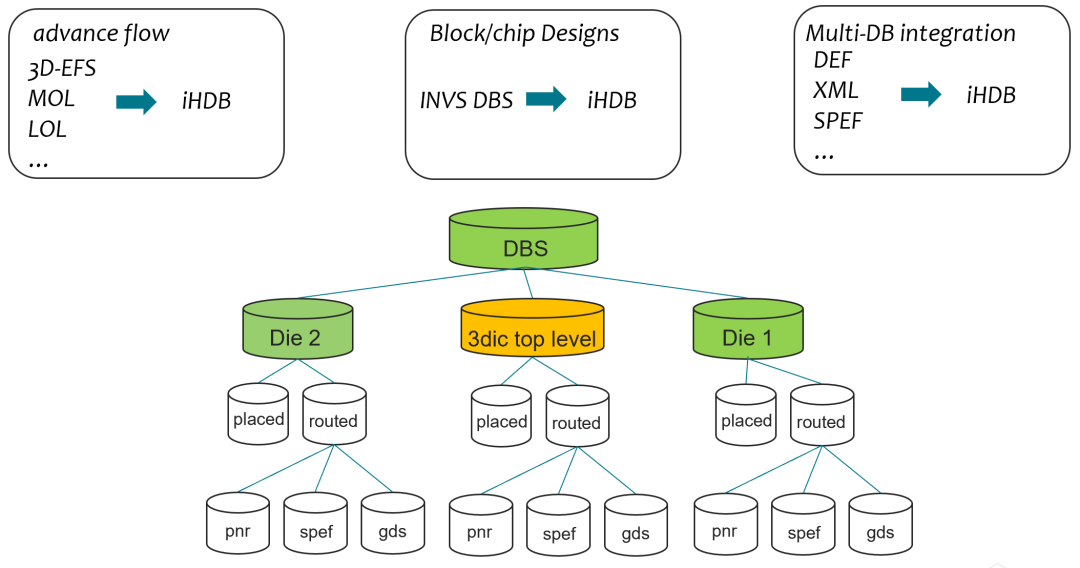

在3D-IC设计中,用户需要管理的不再是一颗芯片的数据, 而是若干个芯片,跨越架构设计,后端实现,封装设计,设计签核的多团队,不同类型的数据管理。在项目进展过程中如果发生ECO,通常需要经过层层沟通,耗时费力易出错。Integrity 3D-IC提供了一套高效的数据管理架构(iHDB),并且可以通过工具将某一个步骤发生的ECO正确的传播到各个团队所需要的数据包中,从而避免了人为沟通检查的时间损耗。

iHDB

(Integrity Hierarchical Database)

iHDB的层次化框架如下图所示,它可以让用户将业界多种形式的标准数据转化成iHDB的层次化结构进行存储。并且其提供Tcl接口让用户可以轻松读写芯片不同阶段不同类型的数据。用户可以通过这个框架管理不同项目节点的存档,确保不同设计者之间交付的数据版本一致性,并可以实现快速的交叉检查。

数据的同步

在3D-IC设计过程中,用户可能在任意阶段做ECO或分析,Integrity 3D-IC提供极为强大的数据同步功能,用户只需要用一条命令就可以完成数据的更新和同步,并可以直接在Integrity 3D-IC 中启用分析签核工具读取更新过后的数据做分析。这可以大大提高不同团队之间互相交付输入件的效率,进而加快项目收敛。

凭借cadence在模拟和数字IC设计,封装设计以及PCB设计领域提供的全方面EDA工具产品的集成,Cadence Integrity 3D-IC 通过统一的层次化数据库结构,利用cadence业界领先的数字/模拟/封装以及签核技术,实现了让用户可以在系统规划和实现流程的早期就进行系统分析和设计迭代,达到系统PPA驱动的高性能3DIC设计效果,同时可以避免高昂的过度设计成本。

如您需了解这部分的更多内容, 请点击“阅读原文” 注册申请我们的Integrity 3D-IC资料包。

注册成功且通过Cadence审核的用户可获得完整版PPT资料。审核通过后Cadence会将PPT发送至您的邮箱,提供您的公司邮箱地址通过审核的几率更大哦!

Integrity 3D-IC资料包

Cadence Integrity 3D-IC 平台提供了一个高效的解决方案,用于部署 3D 设计和分析流程,以实现强大的硅堆叠设计。该平台是 Cadence 数字和签核产品组合的一部分,支持 Cadence 公司的智能系统设计战略(Intelligent System Design™) ,旨在实现系统驱动的卓越 SoC 芯片设计。