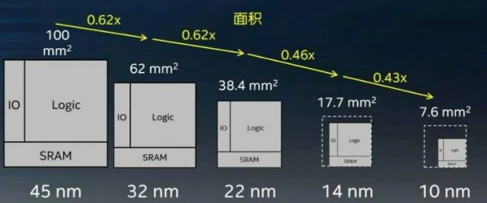

近来芯片行业都在不停的提速,大到IDM巨头,小到一个初创芯片设计公司,无一不在以比以往更加快速的抢占新制程的高地。几乎每家都在不断努力降低设计和生产成本,积极响应不断变化的客户需求,在日渐充满挑战的商业环境中,芯片的复杂性是一个关键点,无论是原型设计还是芯片layout,对于技术节点缩小,设计规模扩大和芯片系统扩大----这一“缩放”过程,都表示难度呈几何级上升。

DFT越来越重要

DFT----可测试性设计,在IC测试和监控时的作用日益重要已经是无可争议的事实,过去IC设计、制程良率把控、再到测试和整个生命周期内监控已经捉襟见肘。举例来说,汽车电子的蓬勃发展让越来越多的安全型器件走向大众视野,这些元件需要非常高的测试质量和测试项目,在设计初期就必须考虑元件级和系统级的DFT。

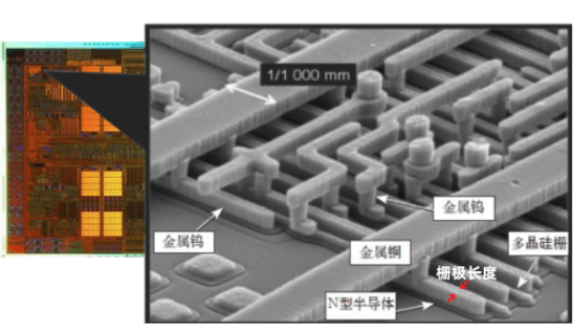

曾经有一位质量管理的老员工和笔者聊起DFT的核心是什么,其实就是在硅片内部的“警察”,用来捕获片内所有的缺陷,每一道或者几道工序后,都有着不同的测试检测方法,就这样不停地筛选修正才能确保最终器件之余系统内会按照初期设计安全运行。而且对于先进的工艺节点,很多缺陷都是发生在各个逻辑单元内部,互联部分少了很多,当然制程越小的节点内部一个微小缺陷就可能影响整个单元。

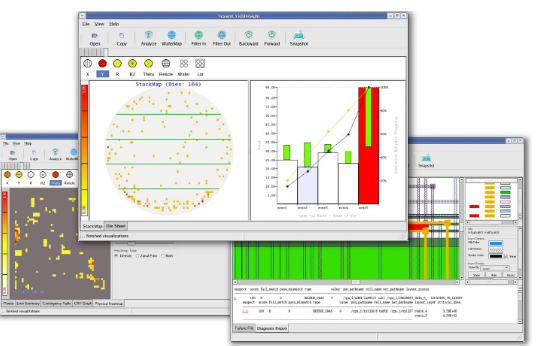

随着节点微缩,芯片的良率将直接影响到新技术在商业上的迈进,而缺陷检测是整个环节最重要的一环,因为我们在提高工艺解决失效时首先要做的就是确认缺陷所在位置,因此大规模高效的批量测试将是未来芯片公司大力发展的重中之重。随着SoC变得越来越庞大和复杂,大多数制造商还是采用手动扁平测试或者分区测试的方法,对于大量集成核心多核心设计来说,扁平化的DFT根本行不通,不仅仅是设计规模和核心数的限制,过去的BIST、扫描测试和其他晶圆中测都依赖于仪器设备,往往是测试时间长、测试的成本高但是效果却越来越不理想,企业抢占市场先机拔得头筹便变得越来越拖延。

系统规模管理和良率提升极其重要

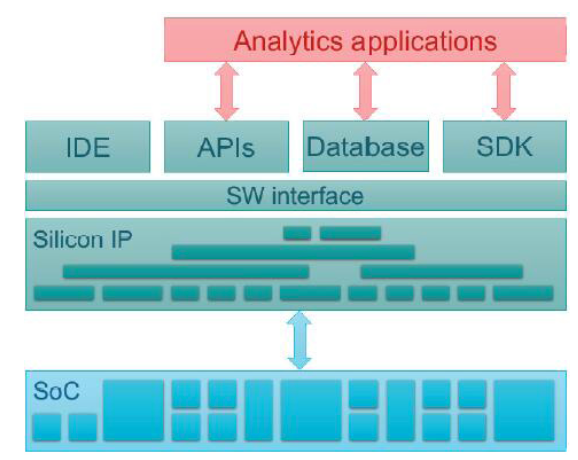

在市场不断变化的今天,一个产品的上市时间和应用现场性能均会受到系统复杂性的影响,要想一鸣惊人就意味着要在第一次流片时把芯片做对,并且配套的生态和工具让芯片在全生命周期内保持最佳状态。这就需要从仿真到模拟、原型设计、流片再到封装和系统验证,所有的工程师都要了解软件和硬件的各种情况,以及在和电路系统交互时的状态。所以系统规模日益提升的同时,所有环节涉及到的人员也成倍增多,现场分析、监控、性能功耗、可靠性、功能安全和网络安全等等,所以系统规模扩展俨然成为了一项新的挑战。

随着无晶圆厂公司的可选代工厂数量的减少和芯片应用场景数量的增加,满足市场对芯片产量的需求已经成为一项艰巨的挑战,晶圆代工厂和设计厂之间的合作关系变得日趋紧密。与此同时,故障分析成本随着寻找根本原因的时间增加而上升,所以解决良率几乎就可以解决一切,已经在先进工艺节点界成了不争的事实,越早利用DFT解决在节点微缩和规模扩大时所遇到的良率问题,就能达到公司量产的产能提升和盈利要求。

所以在半导体设计和制造领域,先进工艺节点需要更加精进的DFT设计和全局把控来提升良率,SoC的功能日益繁杂也需要更多的人力(工程师)和物力(测试软件等)来支持。半导体已经不是之前“半年出师,三年大牛”的单功能IC的时代,未来的IC必将更加复杂。

责编:我的果果超可爱

参考自:

应对缩放挑战以实现硅片成功------Siemens

DFT设计的难点----网络

半导体产业迈入“复杂化时代”, 降本增效成测试行业新趋势----EE Times