近日,由兰州大学信息科学与工程学院副教授何安平团队领衔的异步电路与系统团队设计的首颗极大规模全异步电路(Asynchronous Circuit)芯片成功流片。

全异步电路芯片(图自:兰州大学)

该芯片为120颗名为LZU_GERM的芯片,上图中每一个小方块就是一个独立芯片。它是兰州大学异步电路与系统团队设计的全异步众核芯片,采用40纳米工艺,在96平方毫米的面积里集成了1512个计算单元和3.5亿个晶体管,且每颗芯片的功耗仅有98毫瓦。这些芯片在2021年4月底完成设计,于2022年5月成功回片。

同步电路和异步电路的区别

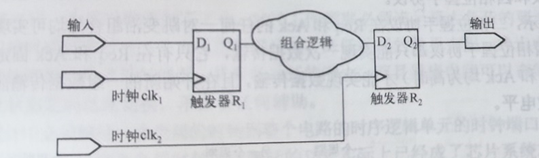

目前数字芯片的主流设计都是同步电路(Synchronous),它的基本结构如下图所示。电路中所有受时钟控制的单元,如触发器(Flip Flop)或寄存器(Register),全部由一个统一的全局时钟控制。如图所示,触发器R1和R2都由一个统一的时钟clk来控制时序,在R1和R2之间有一堆组合逻辑,这就是一个最简单的同步电路。

可以说,这种以时钟信号驱动的流水线结构是现代数字电路的基础。在同步设计中,EDA工具可以保证电路系统的时序收敛,有效避免了电路设计中竞争冒险现象;由于触发器只有在时钟边缘才改变取值,很大限度减少了整个电路受毛刺和噪声的影响的可能。

但是随着设计和测试的复杂度的不断提高,加之低功耗设计(比如clock gating)的需求,在一个实际设计中会出现时钟偏斜(Clock Skew)、时钟抖动(Clock Jitter)及功耗等问题。

异步电路有时也称为无时钟(clockless)或者自定时(self-timed)电路,其基本思想是取消传统的集中式时钟控制机制,采用分布式控制方式管理和协调各功能模块。具体来说,就是通过前后级直接发送握手信号(Request和Acknowledge)来保证数据传输的正确性。Bundled-data是这种机制的一个标准术语,其含义是数据和控制信号捆绑在一起,而其中控制信号则起到了在同步电路中时钟信号所起的作用。

与同步时钟电路相比,异步电路的系统优势体现在:面积小、功耗低、防电磁辐射等等;在异步电路设计时,其优势在于模块化强,电路中的数据传输可以在任何时候发生以及不会出现时钟电路设计时的时钟分布、时钟歪斜等等问题。而难点在于没有时钟电路作为芯片的全局驱动电路,并且主流的商用EDA软件均是针对同步电路设计的软件。国内优秀的同步电路设计团队很多,但是异步电路设计团队却寥寥无几,有能力生产芯片的团队就更是少之又少。

如上图所示,触发器R1由时钟clk1控制,触发器R2由时钟clk2控制,R1的输出端Q1通过组合逻辑连接到R2的输入端D2。D2的输入端的数据值的跳变并不在clk2的控制之下,它可能在时钟clk2的任意时间点发生跳变。在全异步设计中,原来同步设计中可避免竞争冒险现象、减少噪声影响的优点全没有了。

异步电路研究,中国起步较晚

国外从很早就注意到了异步电路的优势并开始了研究,但是对中国却有严格的技术封锁。Intel、IBM等公司已经用Loihi、TrueNorth等芯片证明了用异步电路做类脑计算,无论在功耗还是在性能上均比同时期的同步电路优越。

兰州大学这支研发团队成立于2013年,当时国内异步芯片研发还处于起步阶段,针对异步电路的系统性研发不足。何安平带领团队历经9年时间,从异步电路设计方法学开始,一直探索到芯片设计。早在2018年,何安平团队就在兰州大学发表了名为《异步人工神经网络芯片设计方法与实现》的学术报告。

何安平团队在主流商用EDA软件的基础上,逐渐突破了异步驱动逻辑设计、异步时序约束、大规模异步电路设计和设计稳定性验证等一系列芯片设计问题。团队采用国际上最先进的异步电路设计方法,在这一枚枚小小的芯片上,每一个异步的CPU核都将由异步的mesh网络连接,数据在CPU中运算后会被mesh网络广播到各个路由节点,并被目标路由节点抓取。这样的工作机制非常适合用于如今人们熟知的类脑计算和其他高并发计算领域。

同时,何安平团队基于异步电路设计的EDA软件“拼图”3.0版历经两次迭代,日臻成熟,成为中国自主研发的第一个异步电路EDA软件,并在OpenI网站开源。

附:何安平简历

何安平,兰州大学与美国波特兰州立大学联合培养博士,硕士生导师。

2009年至2011年在美国波特兰州立大学ARC团队的Ivan Sutherland(美国双院院士、1988年图灵奖和2012年京都奖得主)和Marly Roncken(Intel资深工程师)教授指导下,从事异步系统形式化分析与验证研究,2014年开始独立进行异步系统设计与分析验证研究。目前已成功开发全异步RSA芯片、全异步SNN芯片和CNN芯片demo,发表SCI检索论文6篇,翻译国外原著3篇(2篇已成稿待出版,1篇已购版权在译中),参与英文著作1章,EI和其他索引论文30余篇,其中异步系统顶级会议Demo论文1篇,fresh idea论文1篇,CCF B类会议1篇,C类会议1篇,图灵奖得主署名论文3篇,申报专利和软件著作权16项(获批6项),获得省级科技进步二等奖1项,国家自然科学基金青年基金1项(已结题),参与制定Verilog硬件描述语言国家标准1项目,指导研究生获得教育部和电子学会举办的竞赛三等奖2项,作为主要研发人员参与国家自然科学基金、科工局和其他省部级项目7项。

本文内容参考兰州大学电子与信息工程学院、兰州新闻网、央广网、视听甘肃、科学网报道

参考资料:

“传说中”的异步电路能否在AI芯片界异军突起?——知乎@ 唐杉

同步电路、异步电路设计——博客园@ Real马锥

上传视频可以获得5-100元不等的现金奖励,优质视频创作者还可以获得精美礼品一份。

视频要求:

1、原创视频;

2、电子行业内容;(无论是电子技术知识讲解、技术应用、设计实例、市场分析...等)

3、发布视频时,标题中请添加#芯视频#,即视为参加本次活动;

扫码直达芯视频