这篇文章作为《展望来年3nm之争》系列文章的最后一篇可能有点牵强(前两篇的链接:上篇 | 中篇),因为本文展望的恐怕是3nm之后的技术与竞争——基于现在的信息,Intel不大可能在3nm工艺竞争中取得优势。不过Intel作为尖端工艺制造的其中一股力量,探讨其技术竞争的未来也是相当有必要的。

上个月,我们写过一篇题为《2025年,Intel真的有机会重回王座吗》的文章,主要是阐述Intel在投资者会议上更新的计划表。好像相关Intel“重回王座”的话题,电子工程专辑已经探讨过好几次了,虽然角度不一样。“重回王座”的一个前置条件是:Intel曾经是王座之上的人,以及我们这里所说的王座,具体是指半导体尖端制造工艺。

130nm工艺时期(2001年)甚至更早,稳步的两年迭代节奏是Intel得以确坐稳“王座”的基础。90nm时代Intel是行业内首个针对应力增强引入eSiGe(嵌入硅锗)的企业;2005年Intel首度采用HKMG(high-k metal gate,高介电常数金属栅),比别家提前了5年以上;2011年Intel 22nm工艺首次引入FinFET结构晶体管......

所以我们说当年的Intel是以比别家fab和foundry厂领先几年的技术水平存在的。只是眼见14nm技术以后,Intel开始遇上瓶颈;10nm迟迟不见成熟,7nm变得遥遥无期。Intel的初代14nm处理器是2014年出货的。14nm一用就是6、7年。2021年11代酷睿桌面版CPU都还在用14nm工艺。2019年才算正式问世的10nm工艺,事实上历经3次迭代才全面走向成熟——这一点我们在过去的文章里也多有总结。

从名义上来看,三星14nm和台积电16nm工艺是在2013年首次流片的。不过基于这两家foundry厂热衷于工艺数字的虚标,2014年的Intel 14nm在行业里仍然是领先的。只是在随后漫长的迭代周期里,台积电和三星对Intel实现了制造工艺上的全面赶超,尤其是台积电。

Intel作为半导体制造厂的技术水平被赶超的拐点,出现在2018年台积电N7(7nm)工艺问世之际。按照Intel早期的路线图,Intel 10nm理应于2016年问世——普遍认知中,Intel 10nm ≈ TSMC 7nm。但很快由于技术问题,10nm大规模量产被推迟到2017年,后被推迟到2018年,再是被推迟到2019年。2019年9月,10代酷睿笔记本CPU才正式以10nm量产的姿态大规模上市。

2019年的10nm仍然算不上成熟,且遭遇了产量和良率问题。同期AMD Zen 2架构CPU开始采用台积电7nm工艺,在最终出售的CPU产品上,首次实现对Intel处理器的部分超越。至此,在2019年这个时间点上,Intel正式无缘“王座”;保持了多年的技术领先地位不再。

现在和Intel 10nm(包括Intel 7)同场竞争的乃是台积电5nm。Intel 10nm的逻辑电路晶体管密度大约为100 MTr/mm²(百万晶体管/平方毫米),而台积电N5工艺的该值为173 MTr/mm²(这个值后续似乎已调整为185 MTr/mm²)。另外从SRAM单元大小、CPP、MMP间距等各个维度来看,台积电N5都有着全方位的优势。

有关4年更新5代工艺

本文不再细数Intel到2025年打算重回王座的技术路线图,可参见前文给出的部分超链接。抛开IDM 2.0计划,以及新任CEO对Intel文化、人才等布局方面的革新不谈,总的来说为了重现昔日荣光,在尖端制造工艺方面,Intel的计划是4年要推进5个主要工艺节点。

包括已经量产的Intel 7;将于今年下半年量产(或做好量产准备)的Intel 4;明年下半年量产(或做好量产准备)Intel 3;2024年上半年量产(或做好量产准备)的Intel 20A;以及2024年下半年量产(或做好量产准备)的Intel 18A。

前不久的Intel投资者会议上,Intel还将18A工艺的量产时间进行了提前,最终造就这张4年迭代5个工艺节点的紧凑时间表,得以于2025年再度回到半导体尖端制造工艺的王座之上。

这张表看起来是有些夸张的。不过也算是Intel吸取此前教训的一个重要缩影。早年Intel每2年才进行一次工艺迭代,这种迭代主要基于相对严格甚至过度地遵守“摩尔定律”,毕竟摩尔定律就是Intel的Gordan Moore提出的。在此期间,Intel是相当执着于(甚至迷信)晶体管密度这个值的。

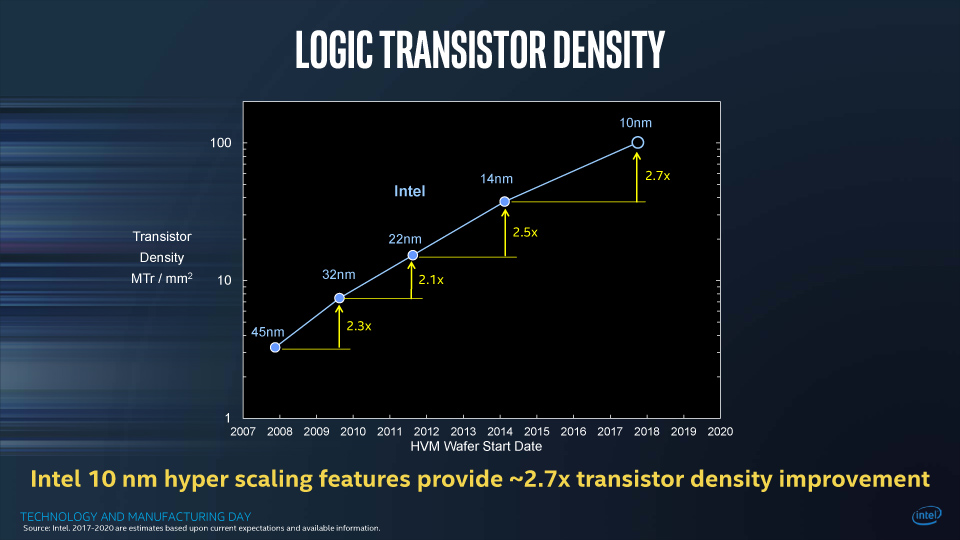

从2017年Intel公布的这张逻辑晶体管密度进化方向来看,22nm→14nm,Intel达成了2.5倍晶体管密度提升;而14nm→10nm,Intel的目标是2.7倍的晶体管密度提升。Intel当年称其为Hyper Scaling超级缩放。这些值放到今天来看还是比较惊悚的。我们说台积电N7→N5 1.9x密度提升,N5→N3 1.6x密度提升已经算比较大的迈进幅度了。

很多分析师认为,Intel 10nm、7nm工艺难产的关键,就在Intel对于晶体管密度的偏执上;也是这些工艺节点无法按照计划中的时间点完成的真正原因,毕竟它们造就了更大的技术障碍。

三星和台积电的工艺节点推进就完全没有这方面的包袱——他们每代工艺以更小的晶体管密度进行迭代,中间还辅以过渡节点(如N7+、N6、N4等),过渡节点间有时也有晶体管密度的小幅提升(如N4相比N5可实现6%的die面积缩减)。

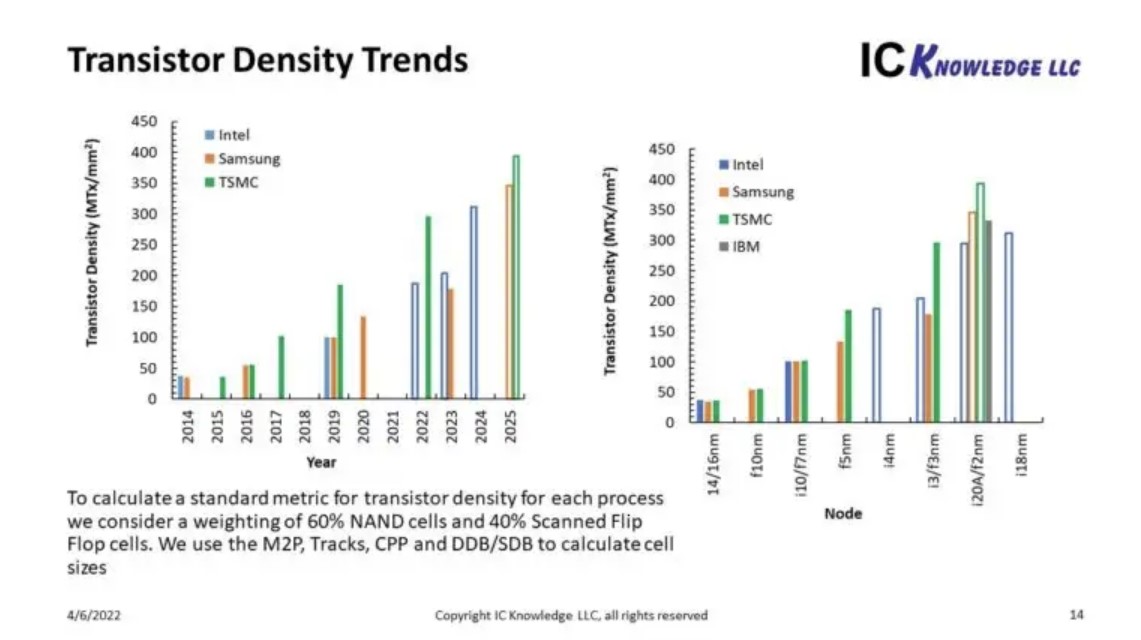

Intel去年的工艺节点改名操作,以及4年更新5代节点,实则都是对过去动辄2.x倍晶体管密度提升这一传统和偏执的抛弃。比如原本Intel 4(原7nm)计划中要实现2.3x密度提升。从最新消息来看,这一激进操作似乎也将不复存在。IC Knowledge对于Intel新工艺的预期为,Intel 4相比Intel 7晶体管密度提升1.8倍,Intel 20A会有1.6倍密度提升。(虽然我们认为这组数据可靠性很值得怀疑)

IC Knowledge预期中,2014-2025年三家尖端工艺晶圆厂的逻辑电路晶体管密度变化(通常特指高密度或超高密度单元库,计算方法见上图小字);不过我们认为这张图的参考价值可能并不大

而且这5个节点中,Intel 3、18A理论上都类似于半代工艺节点(被Intel称为TOCK节点),是对Intel 4、Intel 20A这种完整迭代(TICK节点)的工艺优化和更新。这回的半代工艺节点应当也会有晶体管密度提升(这和此前14+/++时代就大不一样了),比如IC Knowledge预计Intel 3工艺将有1.09倍密度提升,Intel 18A则会有1.06倍密度提升。

从技术难度、更新节奏等问题来看,加上此前我们文章里探讨的“模块化方案”之类的操作方式,要在2025年以前达成Intel 18A量产的目标应当还是有较大操作空间的。

尖端制造工艺的“没准”

一般这种“谁赶超谁”的操作,一方面是后来者要勇于做技术创新和突破,另一方面也可以寄希望于先行者跛脚和失误。虽然这想法略微卑鄙,不过当下我们就已经看到了三星与台积电3nm工艺的集体延后,而且一延后就是至少6个月。苹果的iPhone芯片用台积电5nm工艺家族(包括N4工艺)都已经3年了。况且台积电当年对Intel的赶超,不就是基于Intel的大失误吗?

实际上参与尖端工艺制造的foundry和fab厂普遍有发布会放卫星的传统,IBM、三星、Intel、台积电都堪称个中翘楚。Intel 10nm最早要在2016年上市一说,一延后就是3年;三星早在2019年就放出3GAE工艺的PDK 0.1了,并提到过2020年风险生产、2021年规模量产的,但其实去年6月才有了3nm测试芯片首次流片的消息;台积电过往更是放卫星不断,还有20nm工艺全面翻车这样的黑历史。

既然大家都有“拖延症”,且一般难以按期完成工作,那么这种常态就令人无法轻易取信官方发布的信息。

而且不光是时间上的不靠谱。台积电最早说自家3nm工艺能实现逻辑电路晶体管密度1.8倍的提升,后来变成1.7倍,去年又改成1.6倍;公布的性能与功耗表现提升数据也是反复修改,似无定数。2019年三星最初提到3nm的时候说3GAE工艺相比7nm至多实现45%芯片面积缩减、50%功耗降低和35%性能提升;去年这三个数字又改做25%、20%、10%;最新的数字似乎是25-30%功耗降低、10-15%性能提升。

所以没准和变数,乃是尖端制造工艺发展的特点。谁又会知道2nm时代要出多少幺蛾子。尤其转向GAAFET晶体管以后,其中变数可能会更大。Intel当前面临的问题是,首次在新工艺上准备应用EUV极紫外光光刻,以及后续也要引入GAAFET晶体管,还有PowerVia等具备相当技术挑战的预期,则其发布会提到的每瓦性能提升可能也会有变数。

在变数交织的大前提下,大概没人能搞清楚,3年以后尖端工艺制造谁领先,谁又将崛起。分析师们也不过基于厂商的预期和宣传做出推测罢了,Wikichip和IC Knowledge这类机构,每隔一阵就会对预期和过往数据做调整,即是这些变数的体现。

市场的更多变数

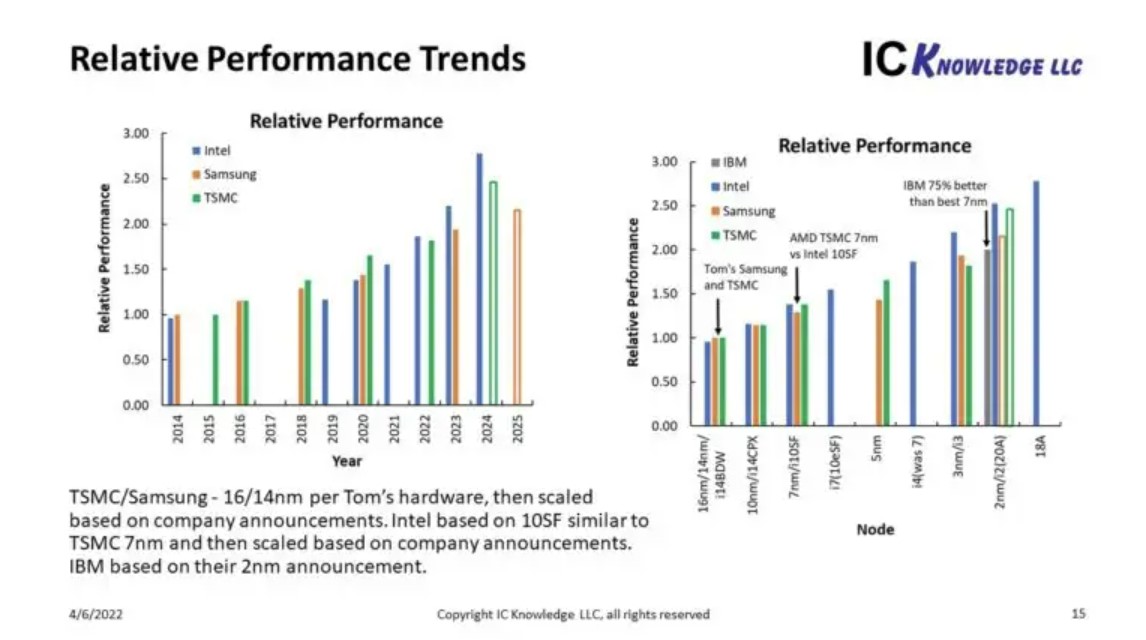

最近Scotten Jones(IC Knowledge)写了篇有关Intel能否在2025年追上台积电的分析文章。前文中给出10年来,尖端制造工艺的晶体管密度提升柱状图即出自于此。这则分析最重要的一则结论是对不同工艺节点的相对性能趋势做了分析,结果如下图:

来源:IC Knowledge

这张图,是以三星14nm、台积电16nm达成相似性能为单位1的。后面的性能评估则基于主要foundry厂后续宣布的性能提升数字,以及IC Knowledge的预估。中间参考值也包括了台积电7nm与Intel 10nm达成相似性能水平等。

基于我们前文提到foundry与fab厂对自家工艺提升表现数字的反复修改,以及如果各位读者有兴趣也可以去看一看工艺迭代的性能提升数字究竟基于什么(比如台积电宣称3nm性能提升10-15%,说的是当大家都基于Cortex A78这个IP做设计时,N3高性能单元库预期可提升的性能),这其中的变数和对比方式之多变,也让这张表呈现的数字仅可作为大略值参考。

最终结论是,预计到2025年台积电仍可在晶体管密度方面保持领先,而Intel将在性能方面取得领先,毕竟Intel发布的节点迈进数据都很大程度基于“每瓦性能”提升。这似乎也符合Intel当前固有市场的特点,即PC、数据中心以及更多HPC类应用。

不过最后值得一提的是,毕竟是多年计划,4年更新5个节点更多是在提振市场信心。就像前文谈到的,尖端制造工艺变数甚多,连厂商自己都没个准,更不必谈未来分析。且此间变数不仅在foundry厂自助机。只说现在面临的行业大问题:缺芯潮将持续数年,就不单是COVID-19有所缓和的问题。

一个颇为关键的变数是,接下来恐怕很快就要面临EUV光刻机短缺的问题了。Intel目前有3个开发工厂可适配EUV光刻,1家生产工厂可应用EUV光刻,且Intel还在造更多需要EUV光刻参与的fab。其他目前下单或需求下单EUV光刻机的企业还包括美光、SK海力士、三星、台积电。

台积电、三星和Intel都将是EUV光刻设备需求大户。台积电目前拥有最多的EUV系统,而Intel将是最为受限的,毕竟其入局EUV光刻技术的时间最晚。IC Knowledge预计,2022-2024年EUV光刻工具需求还将逐年提升,按照ASML的产能来看,今年会有大约18台光刻设备短缺,2024年会有20台光刻设备短缺。Intel 4的产能如果要达到140k片晶圆/月(基于此前14nm与10nm工艺数字),则Intel需要大约45台EUV光刻设备。此前Intel还宣布了需求更多EUV光刻设备的扩展计划。那么这么多光刻机,要从哪里买得到?类似这样的现实问题,都是等着Intel在重返“王座”过程里需要着手解决的。