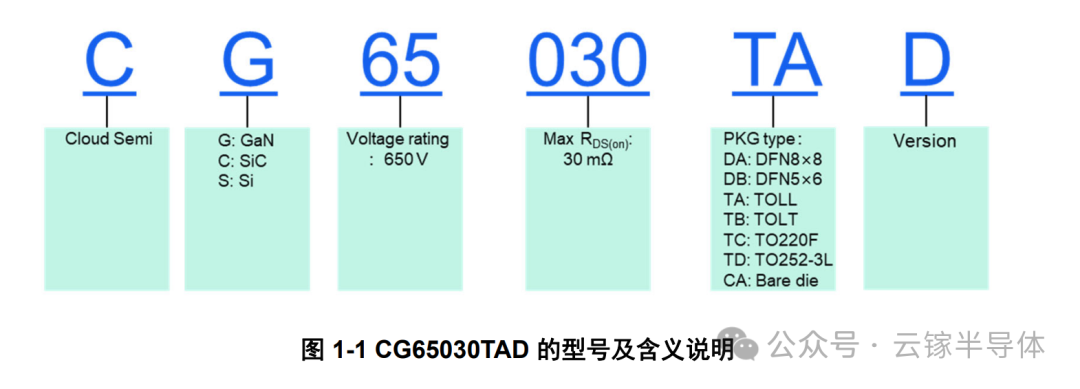

1. 命名规则

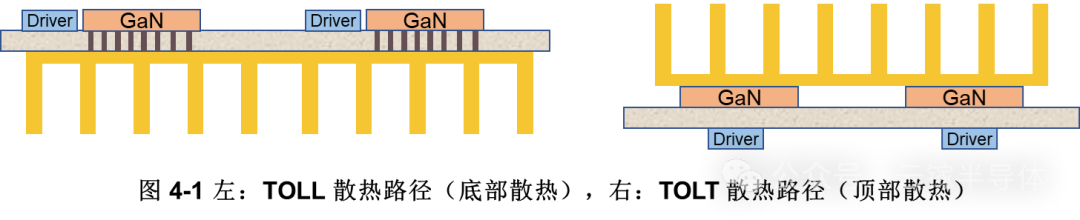

以CG65030TAD产品为例,"C" 为公司名CloudSemi, "G" 代表GaN产品,"65" 代表产品建议的最大耐压为650V,"030"代表器件的最大导通电阻为30mΩ,"TA"代表使用 TOLL 封装,除此以外云镓还有 DFN、TOLT、TO220F 和 TO252 等多种封装类型,最后一位 "D" 为版本号。

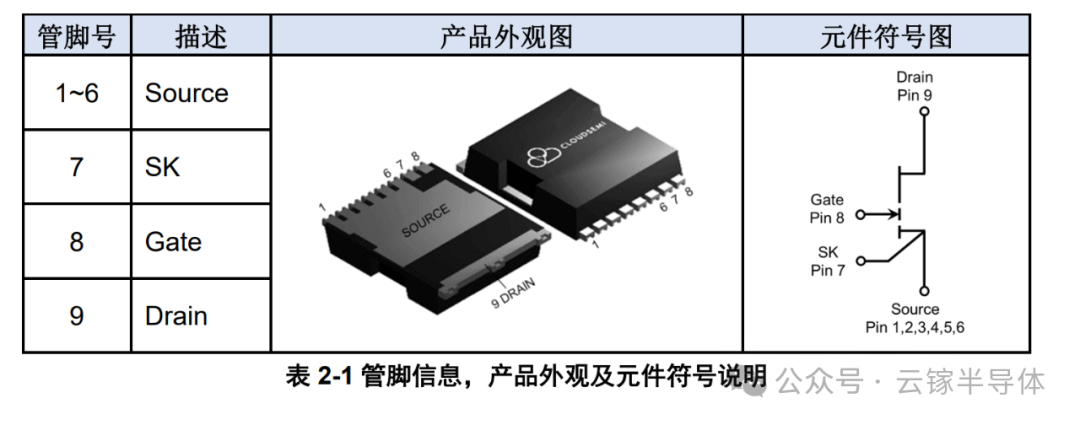

2. 元件符号

CG65030TAD采用TOLL封装,相较于传统Si MOS 的 TOLL 封装,云镓的 GaN TOLL 封装在常规的Gate, Source, Drain 之外,还提供了SK (KelvinSource) 管脚,在使用的时候,SK端口接入驱动回路,不参与功率回路的工作。在开关过程中,源极上的寄生电感在大的di/dt场合下容易导致栅极波形振荡。引入SK端口后,功率回路和驱动回路实现了分立,功率回路电流转换在寄生电感上引起的振荡不会对驱动回路造成影响,SK端口可以有效降低器件源极寄生电感对驱动信号的干扰。从元件符号图上还能看出,为了确保器件的漏极能够承受650V及以上的电压,HV GaN FET在栅漏间设计了更大的漂移区,为非对称的功率器件。

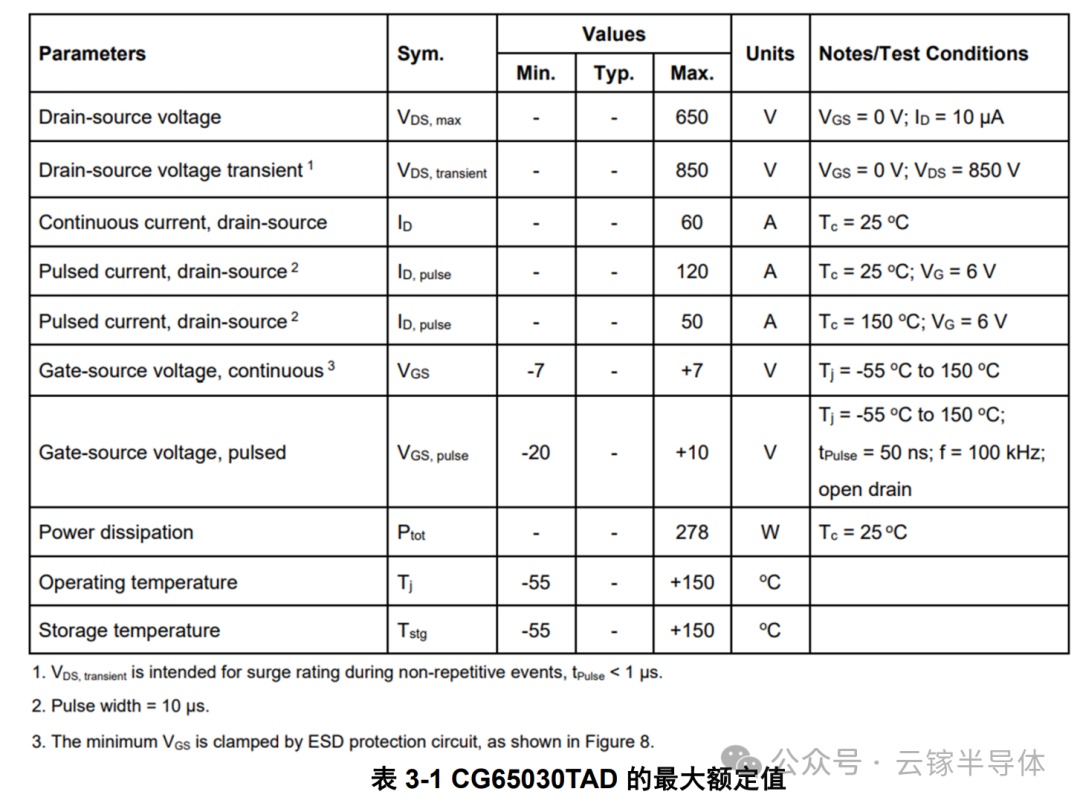

3. 最大额定值

最大额定值规定了此款 GaN 场效应管允许的工作范围,当器件工作在额定范围外时,可能会降低预期寿命。下面以 CG65030TAD 的最大额定值表格为例说明。

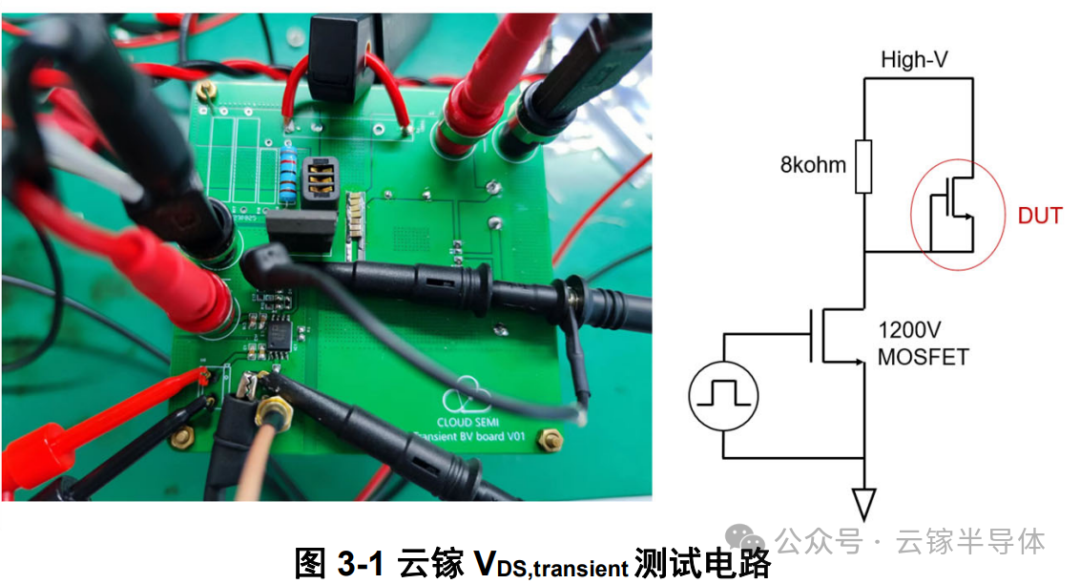

3.1 瞬时耐压VDS,transient

当出现雷击、设备启停或故障等情况时,GaN 器件的源漏之间会有概率地引入瞬时大电压,其持续时间很短,往往在 ns 到μs量级,但对器件的冲击很大,这种现象被称之为浪涌。因此,为了确保器件能在浪涌等极端工况下安全工作,需要在最大额定电压之上,再留出一定的裕量,对应的最大电压值被称为 VDS,transient。

JEP186 中规定了该参数的两类说明规范:1.非重复脉冲情况下的最大电压值,需说明脉宽;2.重复脉冲情况下的最大电压值,需说明脉冲数量及脉宽,或者经历的总脉冲时间。云镓当前基于第一类规范,规定了 GaN 器件在 <1μs 的非重复事件期间的浪涌额定值。测试电路请参考下图。

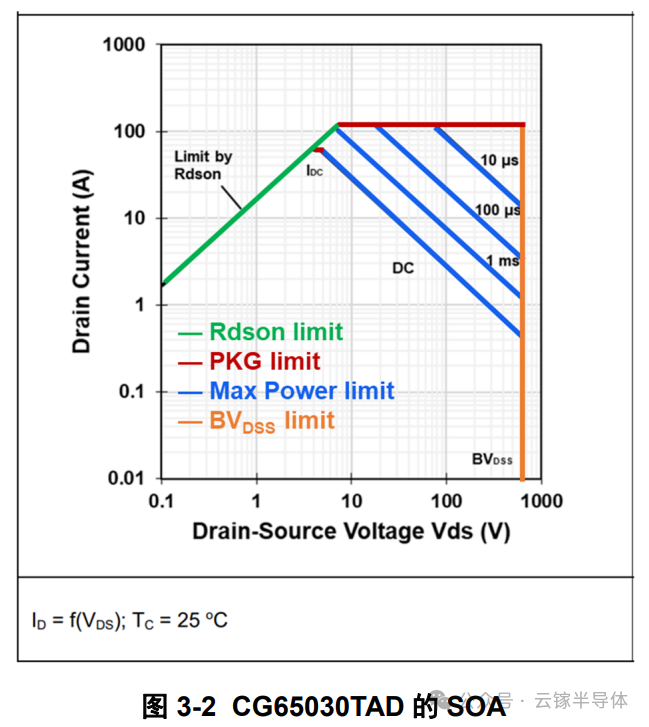

3.2 安全工作区SOA与ID, ID,pulse

对于功率器件而言,安全工作区 SOA (Safe Operating Area) 是个非常重要的概念,若使功率器件安全工作,就要确保其工作条件(电压、电流、结温等)处于安全工作区内。SOA 的横坐标是电压 VDS,纵坐标是电流 IDS,其边界由 RDS(on)、ID、ID,pulse、击穿电压等条件共同限制。

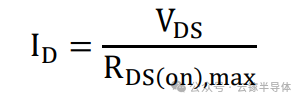

限制1:RDS(on)限制:

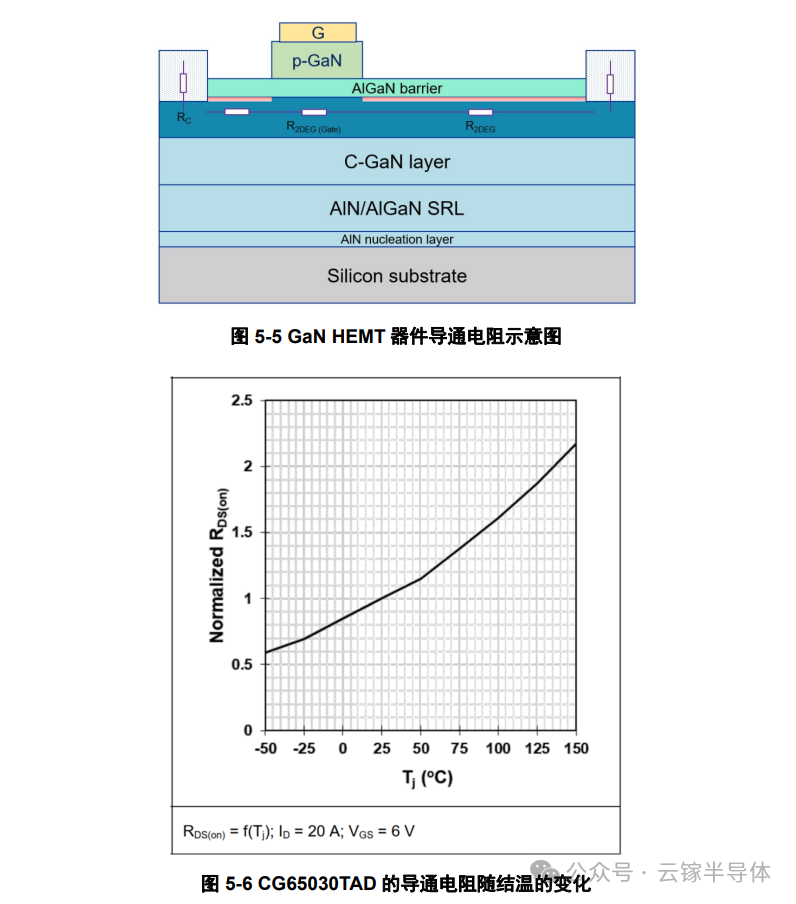

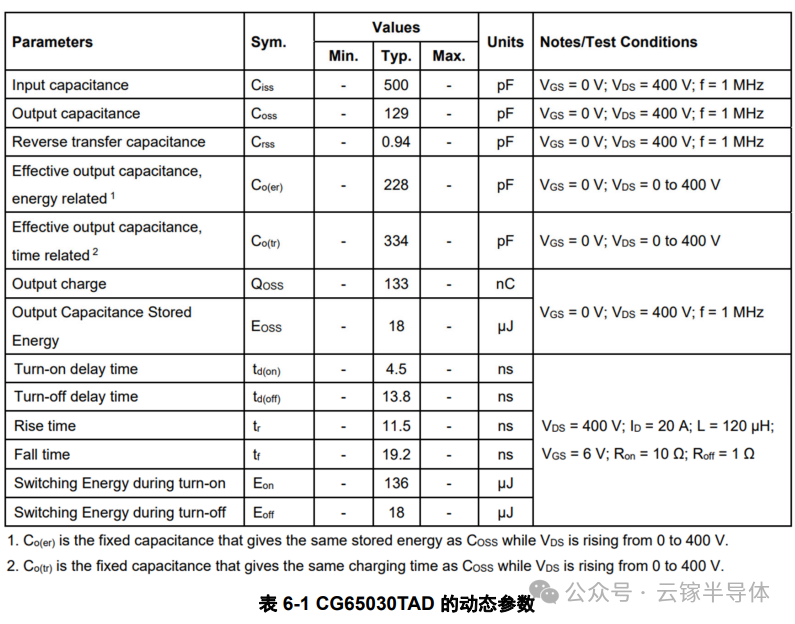

要理解 RDS(on)限制,就需要了解 RDS(on)与结温的关系。GaN 场效应管的结温额定值 Tj,max=150oC,而 GaN 的导通电阻是正温度系数的,当器件结温随功率增加而上升,导通电阻也随之增大。当结温达到最大额定值 150oC,其对应的导通电阻也达到最大值,由此构成了第一个限制条件:RDS(on)限制。该边界具有恒定斜率,表明直线上的每个点都表示相同的阻值,对应最大导通电阻。

限制2:封装散热限制:

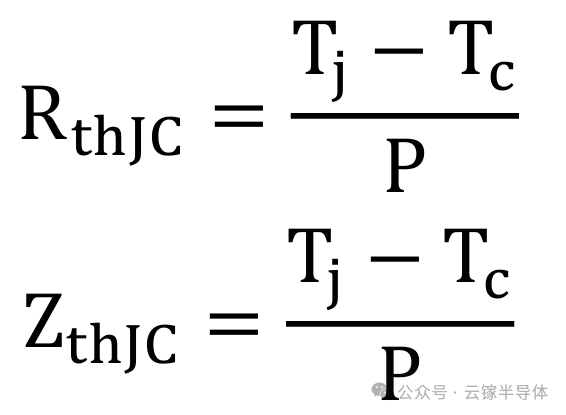

两条水平线表示电流极限,分别对应于直流电流ID (Continuous current, drain-source),以及脉冲电流 ID,pulse (Pulsed current, drain-source), 主要受结壳热阻RthJC 的限制,即封装的限制。而且,相较于直流电流,由于脉冲电流仅施加一定的时长,因此能够承受更大的电流。直流电流 ID具体计算公式如下:

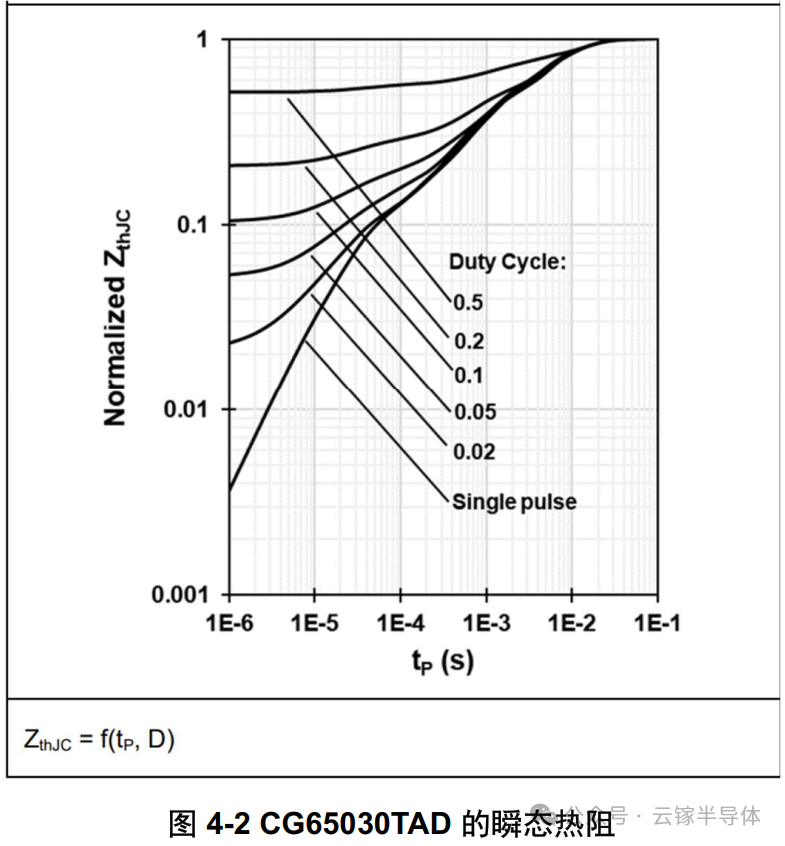

同理可以得到脉冲电流ID,pulse,其中瞬态热阻ZthJC可在瞬态热阻图中读到。

限制3:最大功率限制:

最大功率受到最大结温的限制,该边界上的每个点都表示相同的恒定功率。ID, ID,pulse与 VDS关系如下。需要注意的是,对于脉冲电流,SOA 只给出了单脉冲情况的限制条件,由于瞬态热阻 ZthJC取决于脉冲长度及其占空比,当使用周期脉冲时,其瞬态热阻会根据占空比变化,具体数值可参考瞬态热阻图。

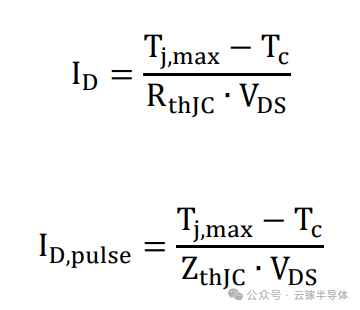

3.3 VGS

云镓的 VGS范围并非 GaN FET 的栅极极限能力,而是确保器件完全开启、长期工作可靠安全且 ESD 泄放电路未打开的电压范围。GaN 器件因为结电容小,ESD 防护能力较弱,故云镓 GaN 产品芯片内部单片集成了 ESD 泄放电路,能够有效提升 GaN 器件 HBM/CDM 等级。云镓 ESD 电路具有自主 IP,拥有正向和反向 ESD 泄放能力,同时满足负压关断的应用需求。正、反向皆具备 ESD 泄放通路,VGS 设计范围为-7~7V。

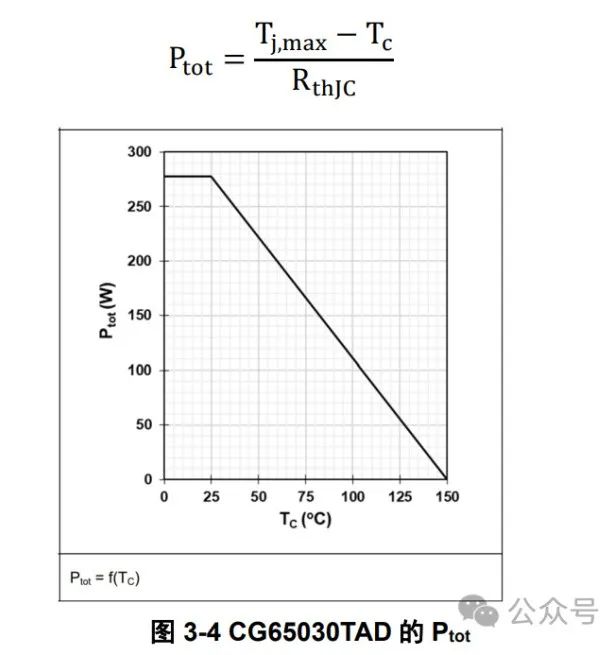

3.4Ptot

Ptot为器件的最大功率,对应器件结温达到Tj,max时的功率。器件的结壳热阻RthJC决定了最大功率随结壳温差变化的斜率,以CG65030TAD为例,下图展示了其在不同壳温下的最大功耗:

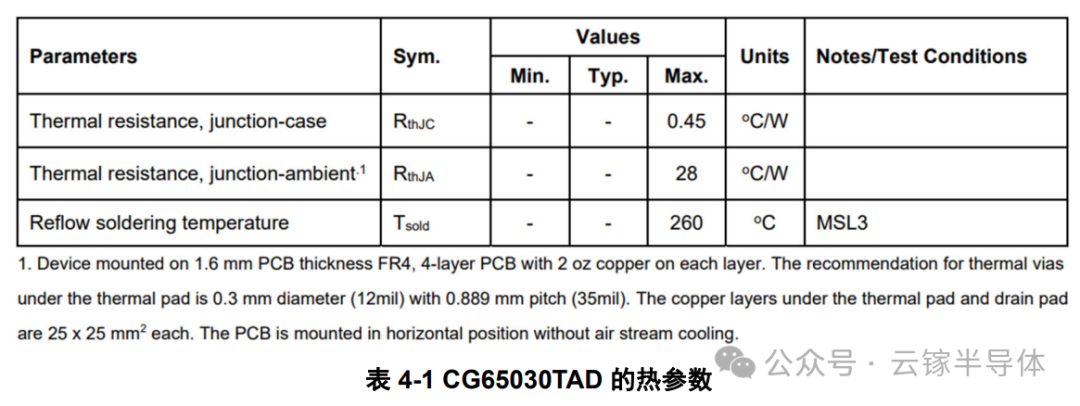

4.热参数

4.1结壳热阻

5. 静态参数

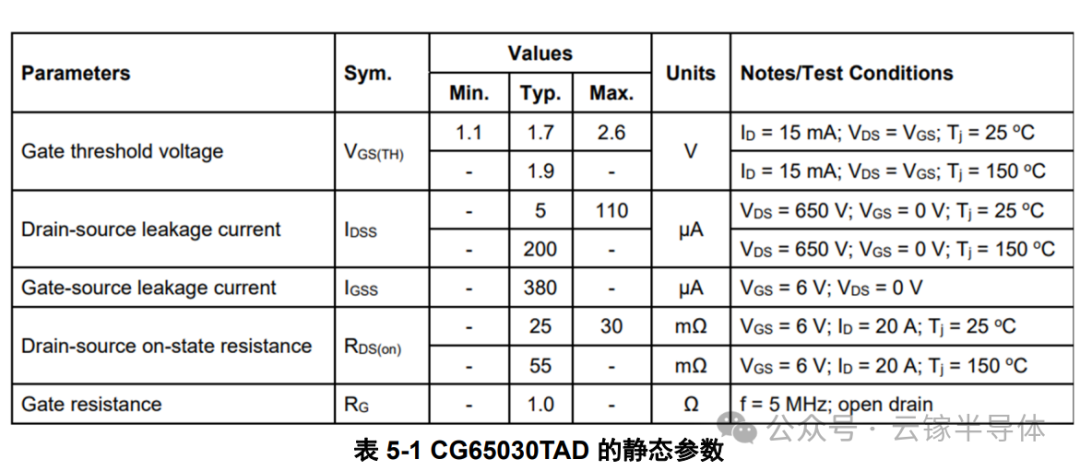

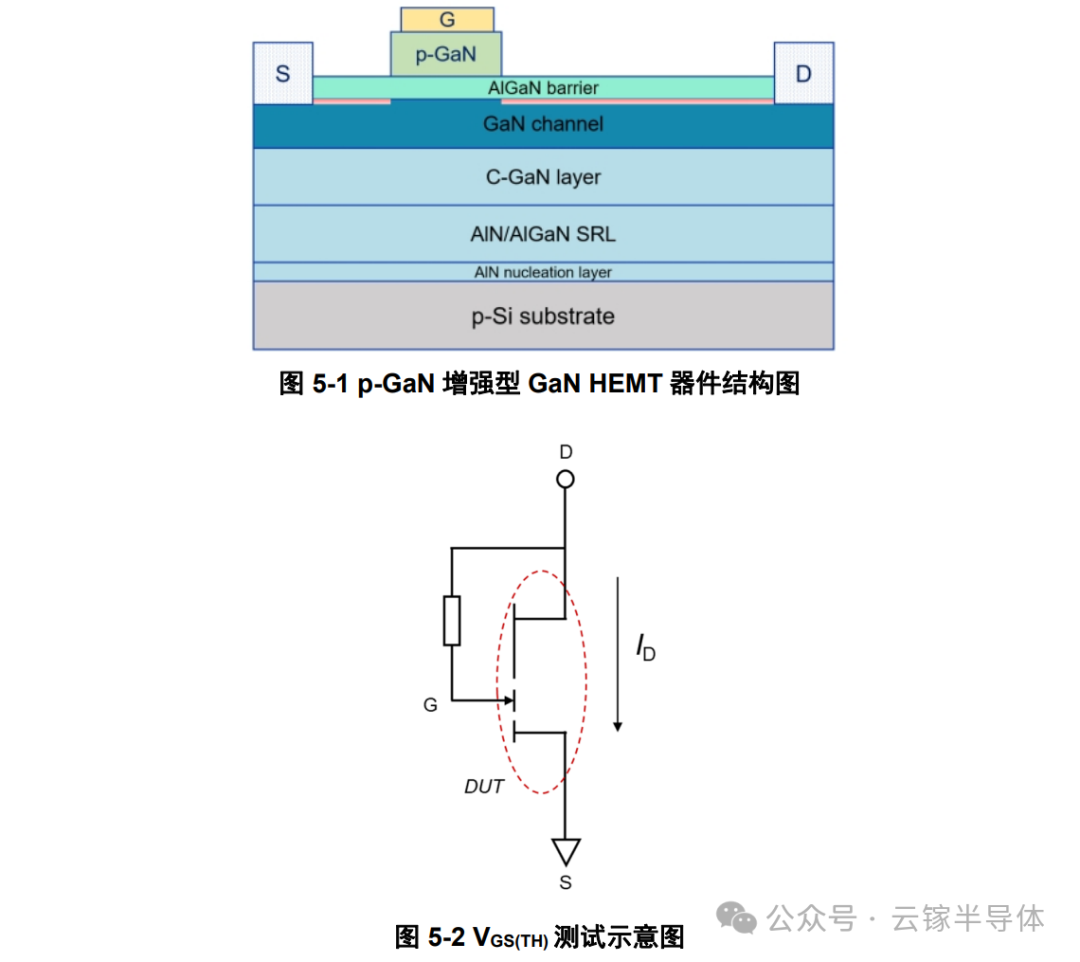

5.1阈值电压VGS(TH)

VGS(TH)阈值电压,即能使器件开启的栅极电压,一般采用常数电流法或最大跨导法来定量。测试方法如下:短接栅极和漏极并灌入目标电流,此时的栅源电压差即为阈值电压VGS(TH)。

5.2漏电流IDSS

IDSS为栅极和源极短路的情况下,在漏极与源极之间施加 650V 电压时测得的漏电流,其具有正的温度系数。

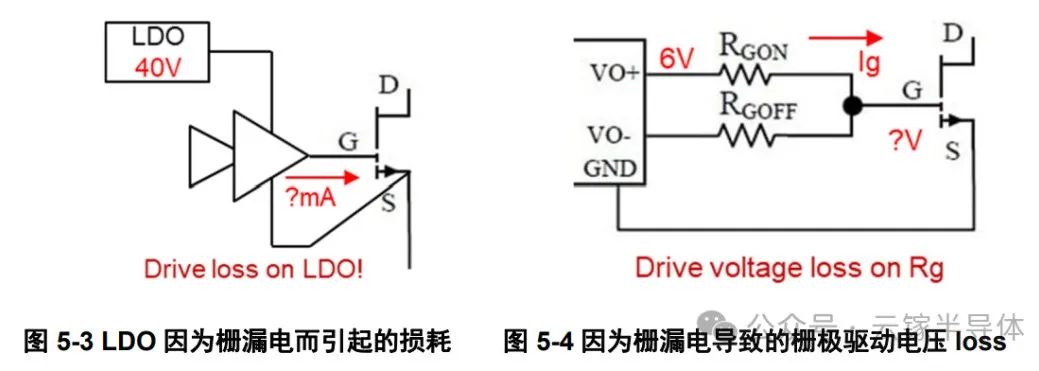

5.3栅电流IGSS

IGSS为器件正常工作时的栅极漏电。测试方法如下:短接器件的漏极和源极,在栅极上加 6V 电压并测得对应漏电流。在应用中,栅漏电的影响主要体现在驱动电路损耗上,若数值过大还会使栅极电压显著低于驱动电压,影响器件 drive margin。这里需要注意的是,因为 IGSS是正温度系数的,其数值会随器件发热而明显增加。

5.4栅极电阻RG

RG (Gate Resistance) 即器件的栅极电阻,是在栅极电压改变时,引起栅极电流变化的电阻。在器件工作时,其与驱动电路中的开启/关断电阻串联,决定器件的导通/关断速度。更低的栅极电阻对应更快的栅极电压切换速度和更低的开关损耗,但栅极电阻也可以抑制在栅极回路上由于寄生电感和电容引起的振荡。

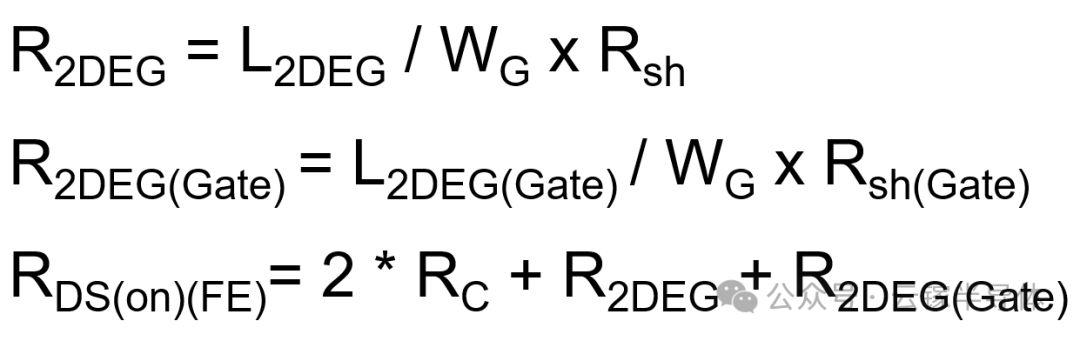

5.5导通电阻RDS(ON)

6. 动态参数

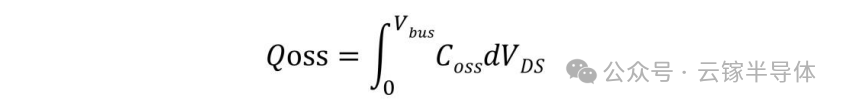

6.1Ciss,Coss和Crss

类似于 Si 基器件,GaN 器件的电容主要由 CGS、CGD和 CDS三部分极间电容组成。如左下图所示,元胞内的电容主要来自于电极-电极,电极-场板,以及垂直方向的bufer电容。此外,互联金属层上下或左右的交叠也会引入极间电容。输入电容Ciss = CGS+ CGD,输出电容 Coss = CDS+ CGD,反向传输电容 Crss = CGD。右下图为 CG65030TAD 的 C-V 曲线,可以发现 Coss, Crss随电压的变化并非连续的,而是在特定电压出现明显拐点,这对应着沟道中 2DEG 被各级源场板“夹断”。

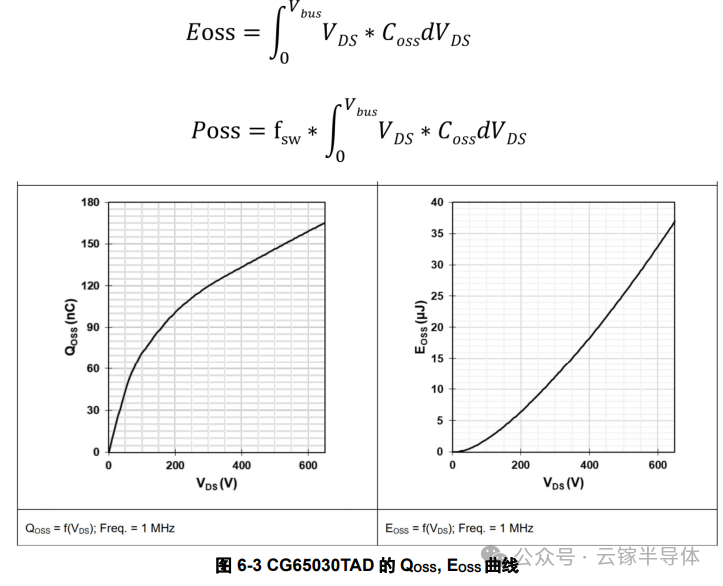

6.2Qoss,Eoss

QOSS即 GaN 器件的输出电荷,通过输出电容对输出电压积分得到,其计算公式如下:

EOSS即输出电容 COSS对应产生的损耗。在硬开关应用条件下,输出电容 COSS产生的能量损耗 EOSS和功耗 POSS可通过以下公式计算:

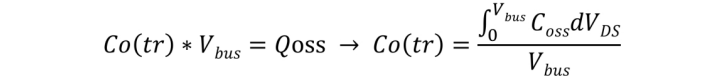

6.3Co(er),Co(tr)

由于功率器件的 Coss是与 VDS相关的非线性曲线,对于评估开关速度以及开关损耗不够直接。对于输出电荷以及开关速度,电源工程师可以用等效的 Co(tr)进行评估,

对于硬开关下 Coss引起的开关损耗,电源工程师可以用等效的 Co(er)进行评估,

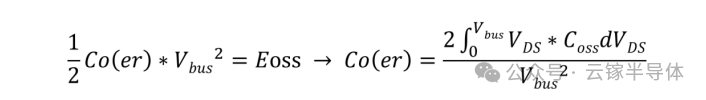

6.4开关参数

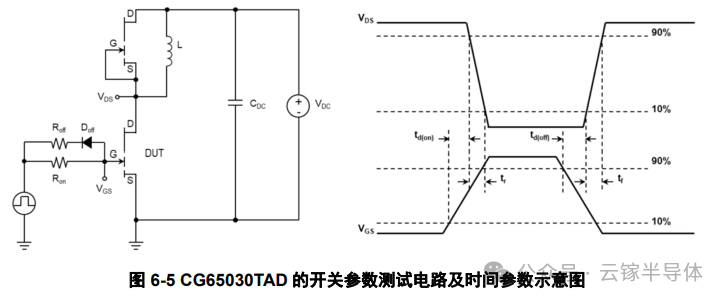

云镓采用感性负载电路,来评估 GaN 的开关特性,并提取器件的开关过程参数。

td(on), 导通延迟时间,指从栅源电压升高超过 VGS的 10%,到漏源电压达到 VDS的 90% 的时间。

tr, 上升时间,漏源电压从 VDS的 90% 降至 10% 的所需时间。

td (off), 关断延迟时间,指从栅源电压降至 VGS的 90%,到漏源电压达到 VDS的 10% 的时间。

tf, 下降时间,漏源电压从 VDS的 10% 升至 90% 的用时。

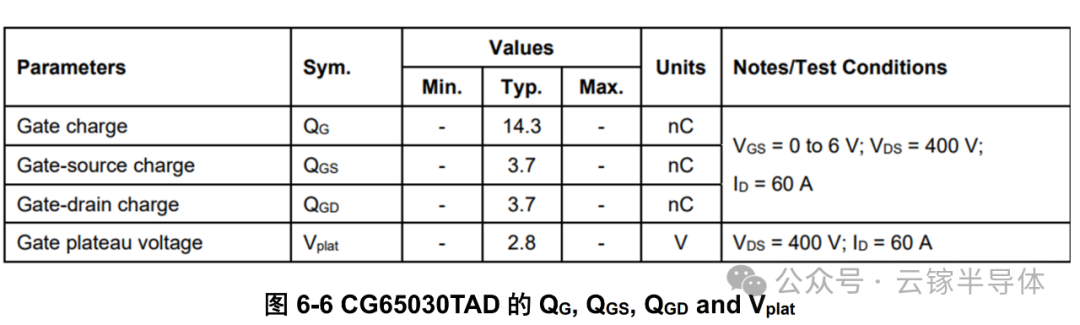

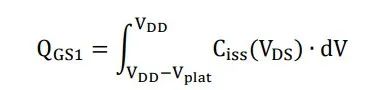

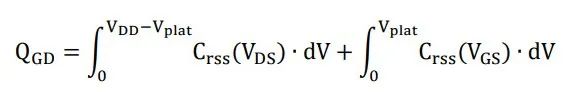

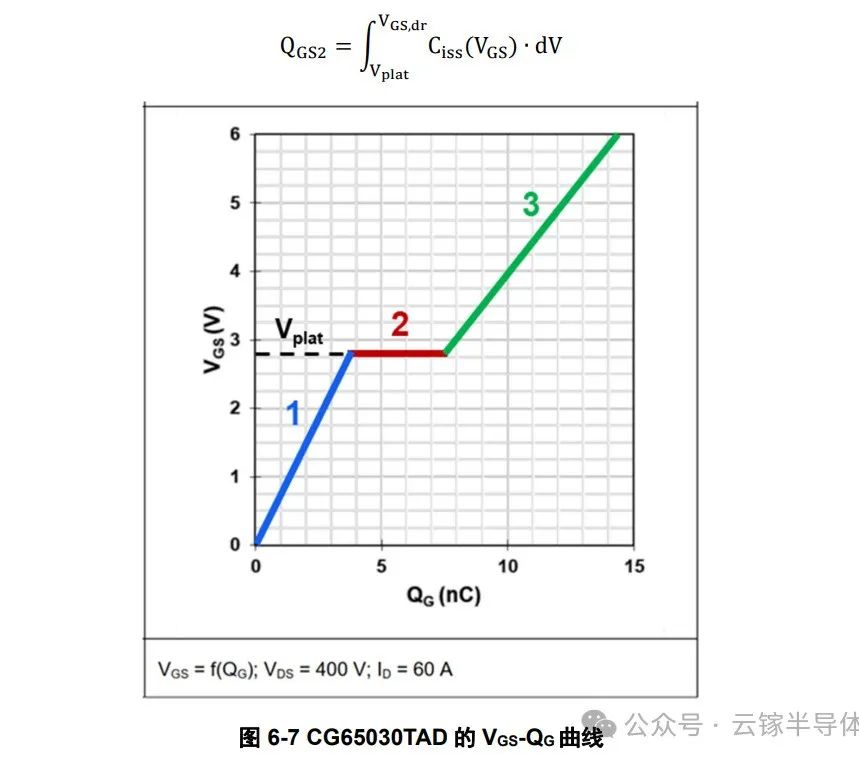

6.5QG,QGS,QGD和 Vplat

这里的米勒平台电压与器件的负载电流相关,可以由器件的输出特性曲线读出,或者根据器件的跨导值估算出,即

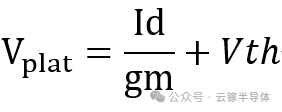

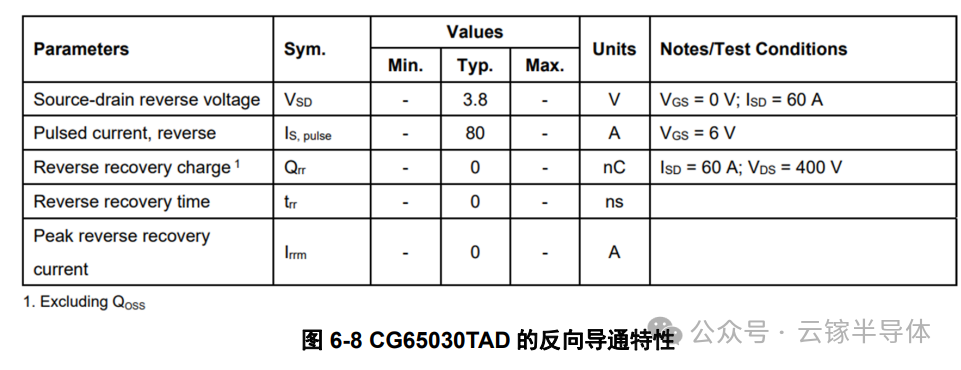

6.6VSD,Qrr

GaN 器件是通过材料极化产生的沟道。无需形成 PN 结,没有体二极管。其反向导通(第三象限导通)的基本原理是 VGS – VDS > VGS(TH):

1)在零压关断场景下(VGS =0),当VSD = VGS(TH)时,器件开始导通续流;

2)在负压关断场景下(VGS< 0),当VSD = VGS(TH)+|VGS| 时,器件开始导通续流。

不同于 Si 器件,GaN 器件在反向导通过程中没有体二极管参与,所以反向恢复电荷Qrr=0,因此在高压的桥式电路以及中低压的同步整流电路中效率很高。

关于云镓

云镓半导体科技有限公司 (CloudSemi) 成立于2021年11月,是一家专业从事GaN功率器件及解决方案的设计公司,现有上海、杭州、深圳三个研发及办事机构。公司核心团队具有多年GaN器件量产经验,具备工艺开发、器件定制、IC设计、封装测试、可靠性评估和系统应用等全建制能力,可以提供定制化设计和全套解决方案服务,帮助客户实现系统竞争力。目前,公司已推出多款氮化镓功率器件及IC类产品,应用场景可覆盖消费电子、数据中心、再生能源以及汽车电子等领域。

公司现有三个研发及办事机构

★ 研发中心:上海市浦东新区锦绣东路2777弄3号楼602室

★ RE实验室:杭州市西湖区留下街道西溪路698号15号楼211室

★ 应用中心:深圳市南山区桃源街道留仙大道4093号南风楼B座512室

更多信息请访问云镓官网:www.cloudsemi.net

或联系我们:info@cloudsemi.net.