1导言

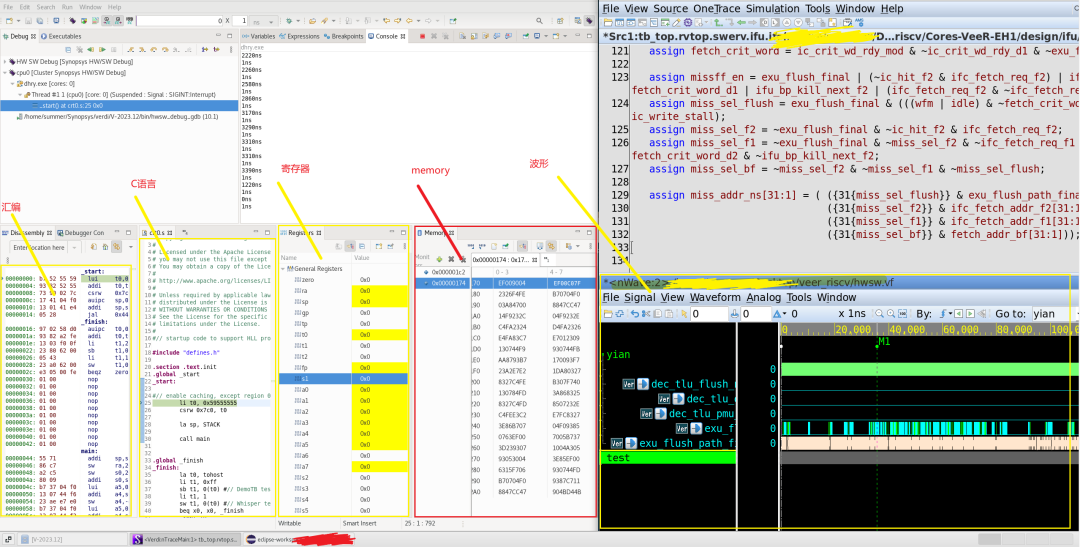

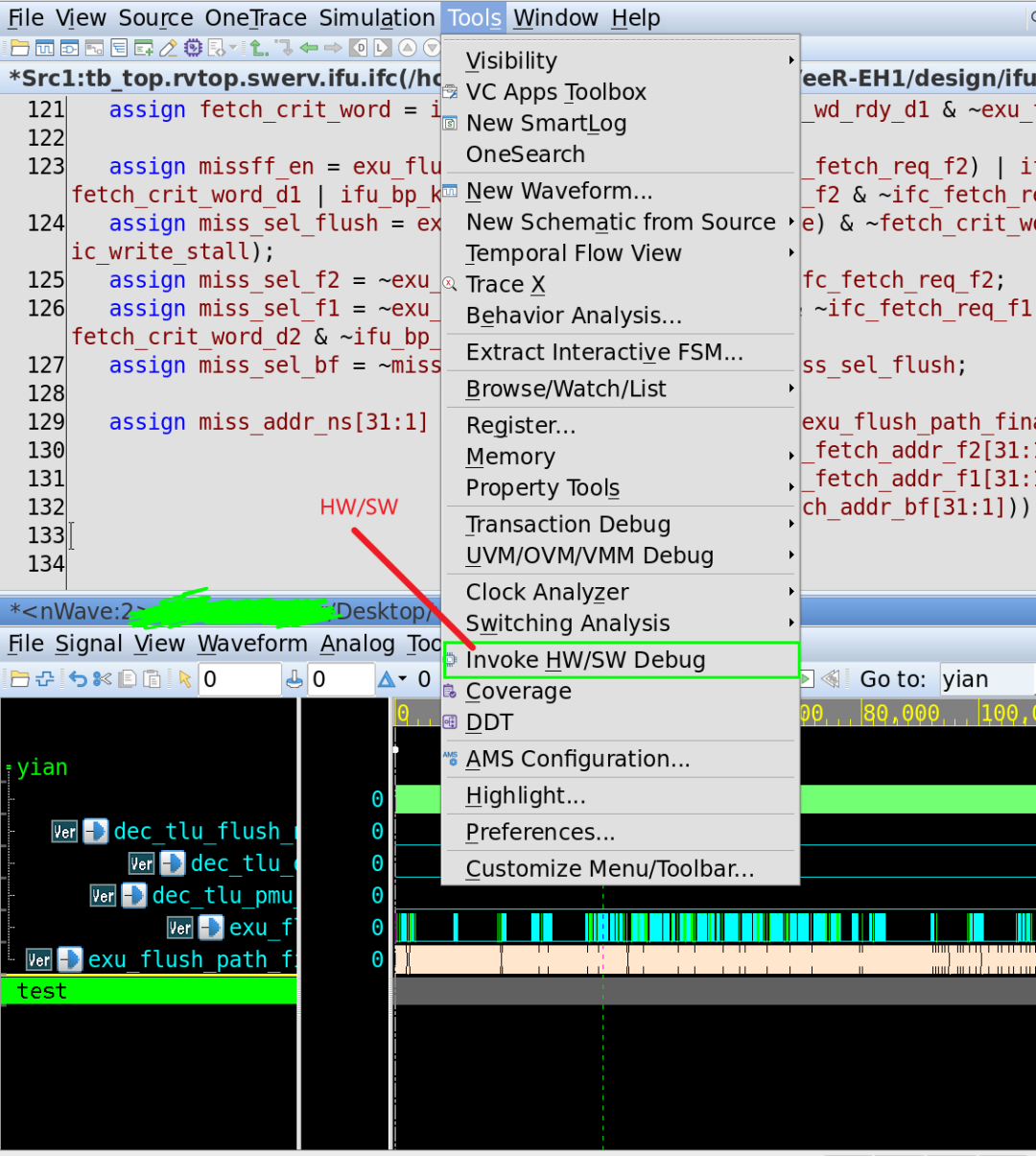

今天介绍的工具是Verdi自带的HW/SW,特点是将汇编语言/C语言/寄存器状态/memory状态和Verdi的波形同步,便于debug。

越来越多的设计包含嵌入式处理器内核。这意味着这些设计的验证涉及在嵌入式内核上运行的代码,通常是开发系统的一个组成部分。同样,测试代码的开发通常是整体验证策略的一部分。硬件调试在硬件级别工作,硬件状态可视化为信号,而嵌入式代码则以汇编或C级别编写。这导致了抽象水平的差距。目前,弥合差距涉及对嵌入式核心工作的扎实理解。它通常通过开发临时脚本来完成,以将捕获的跟踪数据细化到程序集级别。回到C级通常只能通过繁琐的体力劳动来实现。(官方的介绍)

来点直观的感受:

左边是eclipse,分别展现汇编(包含pc,opcode等),C语言,通用寄存器,memory等信息。右侧是Verdi展示的硬件执行波形。

波形-汇编-C语言-寄存器-memory完全同步,数据对debug而言一目了然,非常直观。左侧可以单步执行,其他模块(包括Verdi波形)也同步变化。如果调试右侧波形,左侧的eclipse信息也是同步变化。

2基本介绍

目前手册明确说支持的平台有RedHat和SUSE。亦安自己使用的平台:RedHat7.9(64),Verdi2023.12,VCS2023.12。

官方特别支持的核包括ARM的所有核以及部分合作商的核。对RISC-V架构也同样支持。

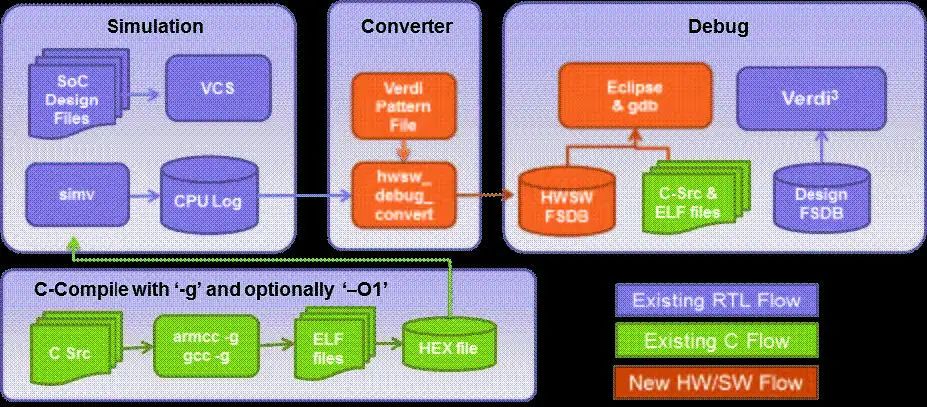

如果你使用的是ARM的核,那么就属于官方支持的架构和核,我们只需要指定仿真核的参数,即可生成hwsw.fsdb用于HW/SW仿真。流程如下:

转换流程如下:

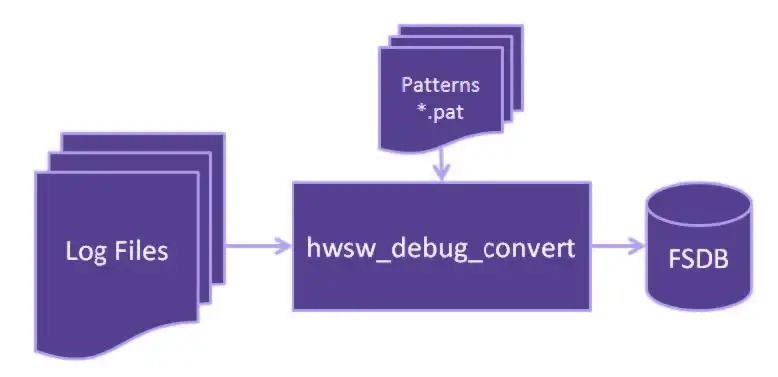

转换命令:

hwsw_debug_convertcpuType=Cortex-M3exeFile=test.elf\

-itarmac.log-ohwsw.fsdb

hwsw_debug_convert:转换命令

cpuType=Cortex-M3:这个命令指示的是tarmac.log/cpu.log的格式,对应的是*.pat文件,该文件解释了log的打印格式。具体tarmac.log格式由vendor决定。*.pat位置在$VERDI_HOME/share/hwsw_debug/patterns。如果是定制化的格式,那么可以自己写一个mycpu.pat放入这个目录下,然后将转换命令换成:

hwsw_debug_convertcpuType=mycpuexeFile=test.elf\

-itarmac.log-ohwsw.fsdb

-i tarmac.log:该命令指示的是输入的log文件,该log文件记录了仿真时的各种状态,例如:

//Cycle:#insthartpcopcodereg=value;mnemonic

//---------------------------------------------------------------

24:#1000000000595552b7t0=59555000;luit0,0x59555000

25:#200000000455528293t0=59555555;addit0,t0,1365

26:#30000000087c029073;csrrwzero,csr_7c0,t0

32:#400000000cf0044117sp=f004400c;auipcsp,0xf0044000

34:#5000000010e4410113sp=f0043e50;addisp,sp,-444

34:#600000001400002805ra=00000016;c.jal0x44

56:#700000004400007155sp=f0043d80;c.addi16sp-208

57:#80000000460000c786;c.swspra,0xcc[f0043e4c]

58:#90000000480000c5a2;c.swsps0,0xc8[f0043e48]

58:#1000000004a00000980s0=f0043e50;c.addi4spns0,0xd0

59:#1100000004cf00437b7a5=f0043000;luia5,0xf0043000

62:#12000000050f6440713a4=f0043db4;addia4,s0,-156

62:#13000000054e0e7ae23;swa4,-484(a5)[f0042e1c]

63:#14000000058f00437b7a5=f0043000;luia5,0xf0043000

63:#1500000005cf3440713a4=f0043d84;addia4,s0,-204

64:#16000000060e0e7ac23;swa4,-488(a5)[f0042e18]

64:#17000000064f00437b7a5=f0043000;luia5,0xf0043000

65:#18000000068e187a783a5=f0043d84;lwa5,-488(a5)[f0042e18]

65:#1900000006cf0043737a4=f0043000;luia4,0xf0043000

66:#20000000070e1c72703a4=f0043db4;lwa4,-484(a4)[f0042e1c]

67:#210000000740000c398;c.swa4,0(a5)[f0043d84]

67:#22000000076f00437b7a5=f0043000;luia5,0xf0043000

68:#2300000007ae187a783a5=f0043d84;lwa5,-488(a5)[f0042e18]

72:#2400000007e0007a223;swzero,4(a5)[f0043d88]

72:#25000000082f00437b7a5=f0043000;luia5,0xf0043000

73:#26000000086e187a783a5=f0043d84;lwa5,-488(a5)[f0042e18]

对上面log格式解释的*.pat的文件如下:

#PARAMETERS:configName=RISC-V32IriscvFixes

#Instructions:

%CYCLE%:(\#%DEC%)?0(%PC%)?(%OPCODE%)?(%REGNAME%=%REGDATA%)?;%DISASM%

#ignore

//.*

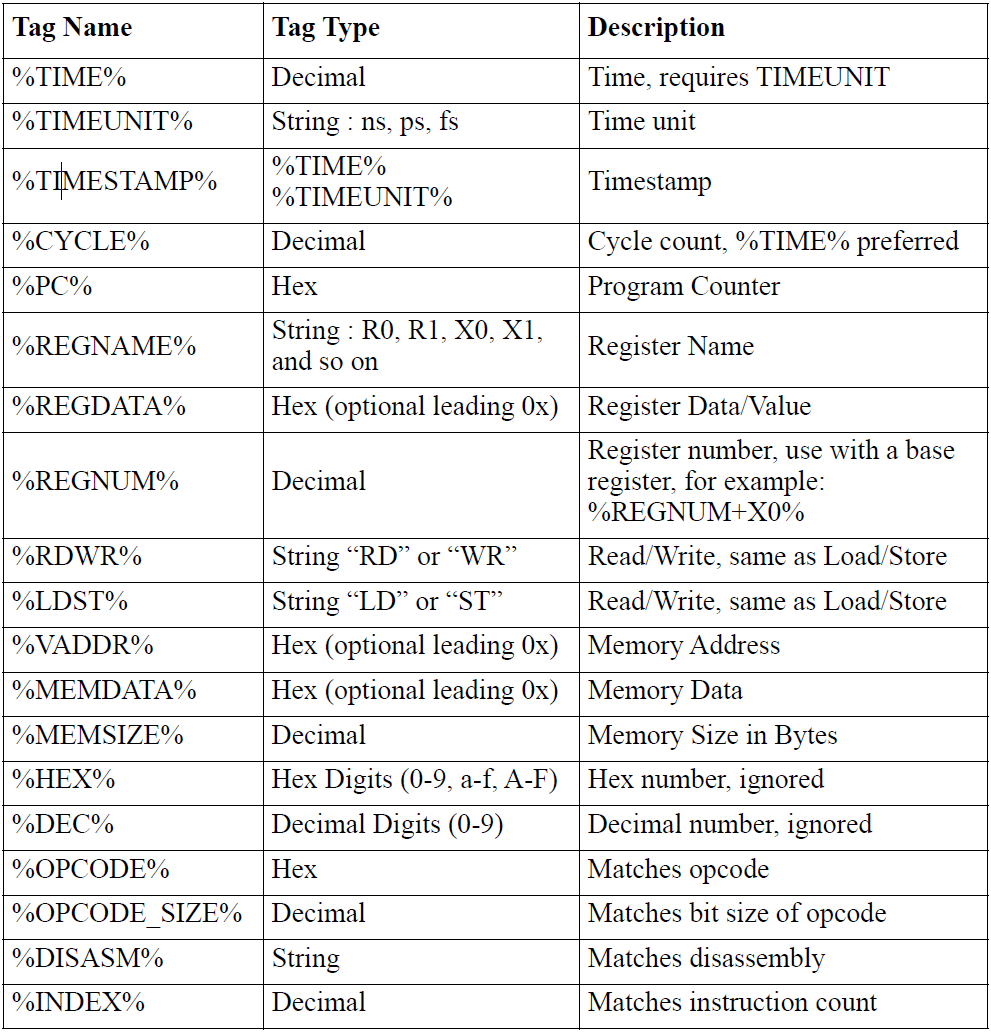

*.pat支持的表述:

-o hwsw.fsdb:这个命令指示的是输出的文件。

转换完成后使用:verdi -dbdir sim.daidir -ssf hwsw.vf打开verdi,并打开HW/SW即可实现硬件软件同步的仿真。

hwsw.vf是对两个fsdb文件的合并,即design.fsdb和log转换来的hwsw.fsdb。

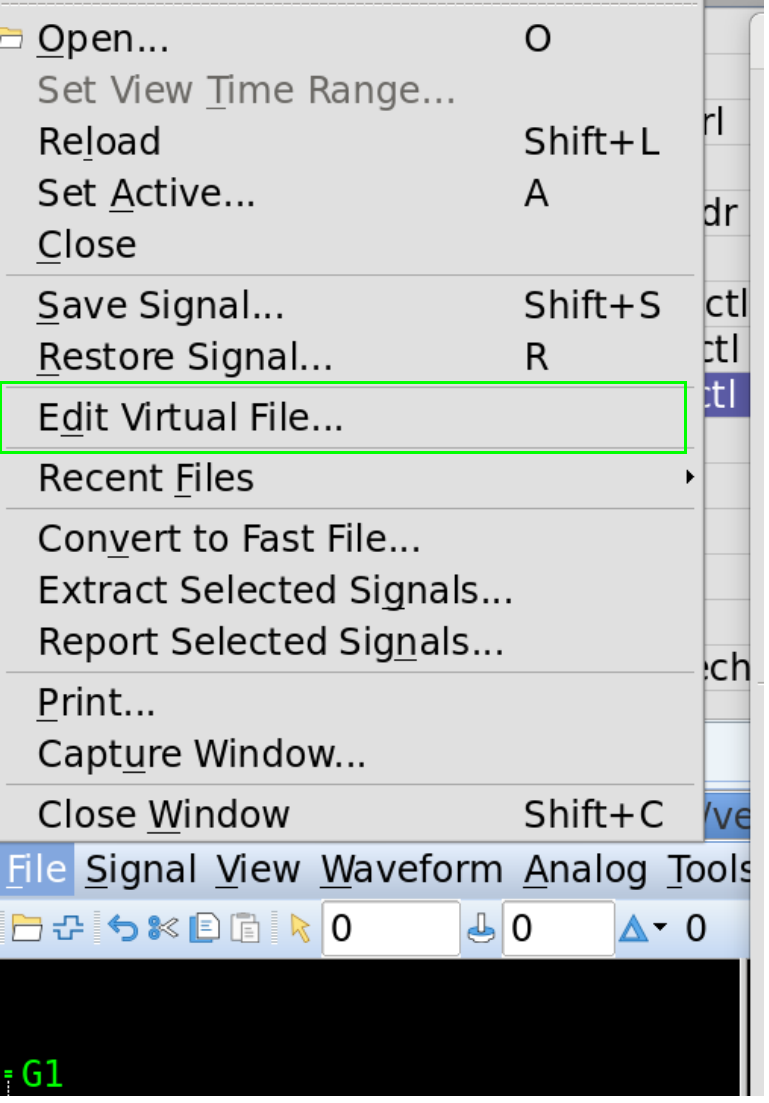

在nwave里面点击File/Edit Virtual File合并两个文件,即可生成上述的hwsw.vf。如下:

3## DEMO

有些细节可能没有讲清楚,这里的关键个人觉得是生成tarmac.log其他基本没有技术含量,手册里面描述的非常清晰,亦安只是把一些宏观流程展现给大家,如果还有问题,请参阅Verdi手册。

官方给了个RV32的Demo,在$VERDI_HOME/demo/hwsw_debug/veer_riscv这个demo可以直接跑,感兴趣的朋友可以体验一下流程。