在每个新的工艺节点上,器件缩放变得越来越困难。甚至定义它的含义也成为一个挑战。

过去,栅极长度和金属间距下降,器件密度上升。今天,由于以下几个原因,这要困难得多:

• 短沟道效应限制了栅极长度缩放;

• 寄生效应限制了器件密度;

• 金属电阻限制了金属间距;

因此,新的器件架构必须平衡这些因素以优化整体电路性能,而不是简单地缩小所有电路尺寸。随着晶体管不断缩小,它们之间的最小间隔正成为进一步增加器件密度的一个至关重要的障碍。

出于这个原因,纳米片晶体管很有吸引力,因为它们增加了相对于 finFET 的沟道宽度,从而使器件能够在相同的整体占板面积中承载更多的驱动电流。然而,整体器件密度受到最小 pMOS/nMOS 间隔的限制。虽然埋入式电源轨有助于减少整体电池占地面积,但它们保持 p/n 分离不变。

forksheet架构在两个沟道之间放置了一个绝缘层,减少了这种最小间隔。但最终,可用空间将非常小,电子可以隧道穿过势垒。

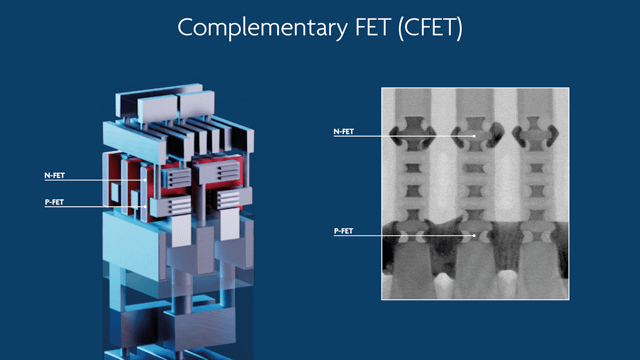

这就是CFET(complementary FETs)的用武之地。CFET 将 nMOS 器件直接堆叠在 pMOS 器件之上,中间有绝缘层。横向 p/n 分离降为零。单个垂直结构中的两个沟道简化了信号路由。

图 1:显示 nFET 和 pFET 位置的 CFET

当然,CFET 架构也带来了一组新的制造步骤(见图 1)挑战。一种方法,即“单片”CFET,将 p 沟道和 n 沟道堆叠在单个纳米片异构结构中。在最近的 SPIE 先进光刻和封装会议上展示的工作中,imec 的 Hsiao-Hsuan Liu 解释说,pMOS 器件通常位于底部,增加的应力有助于减少电子和空穴之间的迁移率差异。作为替代方案,“顺序”(sequential)CFET,在单独的晶圆上制造 pMOS 和 nMOS 器件,然后使用层转移工艺将两者结合起来。这两种选择都不容易,但相对于现状都有优势。

顺序 CFET 可能性能更好,但成本更高

顺序 CFET 方法似乎有很多值得推荐的地方。通过分别处理 pMOS 和 nMOS 器件,制造商获得了独立优化它们的能力。当两层分别处理时,应变工程等性能助推器和 SiGe 等替代沟道材料更容易结合。另一方面,使用两个单独的晶圆会重复许多 FEOL 步骤。层转移过程也显著增加了成本。

位于纽约州奥尔巴尼的 TEL 技术中心的 Lars Liebmann 及其同事估计,单片 CFET 的成本与具有埋入式电源轨的 finFET 工艺大致相同,而顺序 CFET 将使晶圆成本增加约 12%。imec 和 SOITEC 最近的工作估计,相对于纳米片晶体管,单片 CFET 的总成本增加了 15%,而顺序 CFET 相对于纳米片增加了 30%。因此,许多研究都集中在独有的单片 CFET。

虽然分别优化这两层应该可以提高顺序 CFET 的性能,但两者之间精确对齐的需求将限制特征尺寸。特别是,两个器件连接的金属层和栅极层中的特征需要足够大以适应对准误差。Imec 的 Liu 预计单片 CFET 的面积缩小最多可达 15%。

单片 CFET 制造可能更便宜,部分原因是几个 FEOL 步骤只需要执行一次。例如,典型的集成方案可能会为 pMOS 和 nMOS 层构建单个 Si/SiGe 异质结构——使用类似于纳米片晶体管的工艺。然后,整个堆栈在一个步骤中被蚀刻。

Liebmann 还估计,单片工艺可以通过减少 M0 层中的导线拥塞来消除 EUV 曝光步骤——这是一个显著的节省。单片 CFET 工艺还可以利用自对准的优势,例如,在晶体管旁边使用 SiN 间隔物来对准后续的金属沉积。由于没有层转移步骤,因此没有层转移步骤可能使单片 CFET 可能更适合进一步缩放。

沟槽底部的源极和漏极

尽管如此,这种理论成本计算掩盖了相当大的工艺复杂性。通过厚异质结构转移垂直侧壁轮廓需要仔细优化蚀刻条件。在 CFET 设计中尤其如此,它插入 SiN 绝缘层来分隔两个器件。

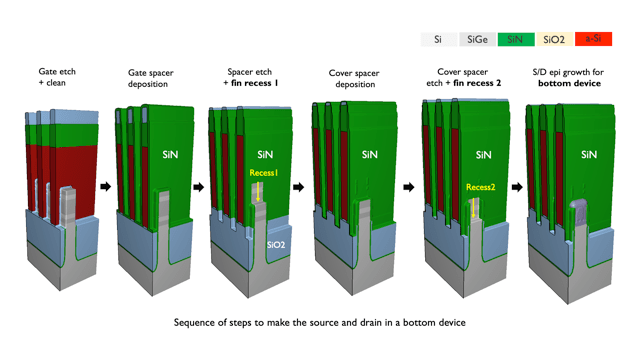

imec 的 Geert Mannaert 及其同事向完整的 CFET 工艺迈出了第一步。他们没有尝试构建完整的堆栈,而是分析了一个带有两个由 SiGe 层隔开的硅通道的鳍,重点关注间隔物和源/漏图案化步骤。栅极蚀刻后,他们沉积了共形 SiN 间隔层,然后对其进行蚀刻,为底部器件源极/漏极创建凹槽。

即使是整个过程的这个简化部分也会带来重大挑战(见图 2)。

图 2:创建 CFET 的流程

即使是整个过程的这个简化部分也会带来重大挑战。要蚀刻的结构在 48nm 的接触多晶硅间距下具有 11:1 的纵横比。间隔物蚀刻应该是各向异性的,以最小化横向 SiN 间隔物消耗。剩余的间隔物材料应与源极/漏极凹槽对齐,以便在源极/漏极生长期间最小化栅极材料的暴露。

栅极氧化物硬掩模将作为未来 CMP 步骤的停止层,因此间隔蚀刻工艺应避免腐蚀它。为了保持电隔离,间隔蚀刻需要相对于隔离氧化物的高选择性。最后,源极/漏极凹槽的轮廓和横向 SiGe 消耗的控制对于器件的最终电气性能至关重要。

Mannaert 表示,在传统的纳米片间隔蚀刻工艺中,主要蚀刻步骤打开源/漏区和栅极顶部的 SiN。在此步骤中调整等离子体条件以创建碳盖层可以保护栅极硬掩模,但也可能阻碍后面的腔蚀刻。在主蚀刻之后,过蚀刻步骤沿着鳍将间隔物拉回。去除 SiN 会暴露氧化物,因此这些步骤通常使用高选择性、高各向异性的氟基化学物质。

最后,源/漏腔蚀刻通常使用基于氯或溴化氢的等离子体。为了针对 CFET 工艺流程优化此工艺,imec 小组专注于源/漏腔蚀刻中的侧壁轮廓控制。钝化不良会导致弯曲的轮廓,但过厚的“聚合物”会产生富氧蚀刻停止层。用氩气代替氦气增加了离子动量,同时调节氧气浓度有助于控制钝化层的厚度。

不过,正如 Mannaert 强调的那样,这项工作仅仅是个开始。开发完整的单片 CFET 工艺将进一步提高整体纵横比,因为需要在两个器件之间插入绝缘体。这将需要进一步改进蚀刻选择性。

与许多其他工艺决策一样,特定设备制造商的需求可能会发挥作用。成本控制和整体器件密度可能有利于单片 CFET,而顺序器件可能提供卓越的性能。不过,由于难以将图案化的有源器件层从一个晶圆转移到另一个晶圆,因此更简单的顺序 CFET 工艺是否会转化为更高的产量尚不清楚。

【免责声明】文章为作者独立观点,不代表功率半导体生态圈。如因作品内容、版权等存在问题,请于本文刊发30日内联系功率半导体生态圈进行删除或洽谈版权使用事宜。