随着尖端电子产品不断推动汽车、工业和航空航天等行业,未来在连接性和自主性方面的不断发展,开发能够符合安全标准的半导体芯片变得至关重要。

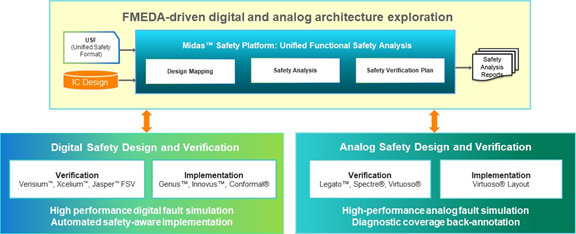

Cadence FMEDA 驱动的安全解决方案包含多款产品,专门针对高级安全分析、安全验证以及数字驱动模拟和数字全流程的兼顾安全的实现进行了优化。

现代汽车内电子元件的复杂性不断增加,促使汽车行业在整个供应链中采用更严格的流程。由于没有合适的工具和方法学来实现可追溯的安全生命周期或者安全相关信息的交换,我们需要一种针对半导体行业的安全要求,并且能够在整个供应链中使用的集成式设计流程。

这就需要一个可以提供无缝衔接的安全方法学来填补安全分析和传统芯片设计之间的缺口(如安全验证和兼顾安全的实现) 。此外,开发安全关键型半导体元件和 IP是一项涉及到大量运算的复杂的任务,为了提高安全方法学的置信度和生产效率,实现流程的自动化是十分必要的。

扫码收听视频解说

优化升级的安全方法学

常用的安全分析方法学,比如FMEDA并没有被集成到IC设计工具或流程中。因此,现在没有一个正式的渠道将FMEDA中定义的安全设计意图传递到IC设计流程,进而驱动相应的安全工具(“自上而下”的方法)。反过来,也没有这样的渠道把故障注入仿真得到的准确数据反标回FMEDA(“自下而上”的方法),用来替换之前预估的失效率。

要充分支持“自上而下”和“自下而上”的安全方法学,一些需要改进的关键点如下:

FMEDA 和安全 IC 设计流程之间的紧密结合

所有 IC 设计工具都支持且遵循的对芯片安全设计意图的形式化描述

导入芯片设计数据,在FMEDA 和芯片层次结构之间建立形式化联系

将仿真结果反标到 FMEDA,提升预估值的准确度

为了弥合这些差距,Cadence 推出了新的

Midas Safety Platform。Midas 与所有 Cadence IC 设计流程紧密集成,支持模拟/混合信号和数字半导体及 IP 进行FMEDA驱动的设计、分析、验证和实现。这个框架提供了一个可以指导安全工程师完成所有关键步骤的工作流程,包括 FMEDA 创建、安全分析、安全验证和兼顾安全的实现。

支持的行业标准

尽管有 ISO 26262 标准,但缺少一种形式化的安全标准来描述安全意图,包括支持的工具流程,因此只能借助电子表格和脚本来开发内部安全解决方案。但是,Accellera 和 IEEE 等标准机构已经成立了专门的工作组,旨在制定充分的安全标准,以满足这些安全要求。Midas 工具,作为 Cadence 功能安全解决方案的一部分,提供了带有多种接口的安全框架,能够在各种工具和流程组成的生态系统内运行:

Cadence Midas Safety Platform 支持 FMEDA 驱动的安全方法

Midas是一个模块化的开放式解决方案,在现有的功能安全标准的基础之上,可以轻松地适用于不同的应用和场景。这就是Midas 集成了支持 ISO 26262(汽车)和 IEC 61508(工业)标准的安全分析引擎的主要原因。

该安全分析引擎既可以借助用户预估的数据 (如面积、触发器数量或内存位),也可以使用Cadence IC 设计工具Genus (综合),Innovus (布局布线) 或 Xcelium (故障仿真)自动计算出硬件安全数据。

此外,Midas 还提供了基于 IEC TR 62380 标准定义的集成电路可靠性模型的基础失效率(BFR)计算引擎。要计算 BFR,需要先输入一些信息,如半导体工艺制程、自定义配置文件和封装信息。

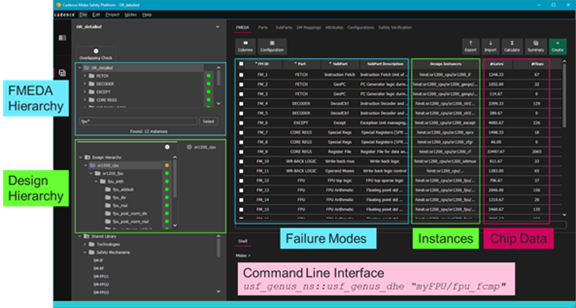

FMEDA 的创建

安全工程师可以从“架构级FMEDA分析”做起,这是在项目初期对不同安全架构进行分析,从中选取可以达到安全目标的最优安全机制组合。

要创建一个FMEDA,需要将SOC按功能模块拆分成元件和子元件,以此来定义 FMEDA 层次结构:

FMEDA 图形用户界面和设置

安全验证完成后,可以将仿真结果反标到 Midas 平台。现在,失效分布和诊断覆盖率的值是基于真实的设计和仿真数据,因此重新计算得出的硬件安全指标要更加准确。

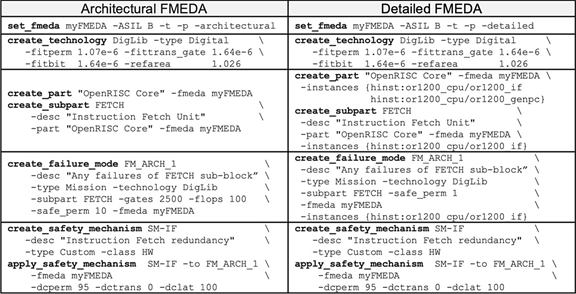

统一的安全格式

统一安全格式 (USF) 是一组命令,用于定义和验证电子设计中的功能安全意图。功能安全意图包括建模、指定、分析、实现和验证安全关键系统、半导体和知识产权 (IP) 所需的信息,以便支持相同的信息在各种商用 EDA 工具之间共享。USF促进了安全分析的自动化,成为设计、验证和实现安全关键系统的通用框架。安全分析引擎也可以通过命令行窗口操作,这使得 Midas 可以完全实现脚本化运行,并支持不同等级的自动化。

利用USF,安全工程师可以通过描述失效模式(包括安全机制及其物理实现),针对 FMEDA 及其对系统行为的影响(失效模式)进行建模。同时,FMEDA 流程也是可以被完整记录的,可以通过修改和重复使用 USF 来自动创建其他项目的 FMEDA。

下图是USF 命令的简单示例,描述了架构 FMEDA(在失效模式层面估算设计信息)和详细 FMEDA(从实际设计中收集设计信息):

USF 示例 — 架构和详细 FMEDA

Midas Safety Platform

Midas 平台的图形用户界面集成了各种功能安全任务:

安全分析编写(设计拆分、失效模式定义、安全机制选取和失效模式映射)

生成安全报告并导出相对指标(例如单点故障率、潜在故障率)和绝对指标(例,随机硬件失效率)

安全配置,用于创建、保存和重建不同的安全场景,在这些场景中可以更改一个或多个参数(例如,通过添加或删除安全机制来分析对诊断覆盖的影响)

支持映射到安全对象(例如元件、子元件、失效模式和安全机制)的自定义属性

安全验证流程

Midas 工具依托 Cadence 在 EDA 供应商中的核心地位,提供了一套安全解决方案和安全控制中心,支持 FMEDA 驱动的安全验证和兼顾安全的实物理现。

Midas 与 Cadence 安全验证流程紧密集成,提供了一种灵活的验证解决方案,可以证实安全分析阶段做出的各种假设。

Verisium Manager Safety 在验证过程中发挥关键作用。它提供统一的故障仿真管理平台,实现自动化地调用各种安全引擎 (例如 Xcelium、Jasper Functional Safety Verification (FSV) App、Spectre® AMS Designer 和 Spectre)执行复杂的故障注入仿真。

Verisium 平台覆盖了多种功能,比如故障仿真执行、测试用例删选和排序、故障分类、覆盖率、故障调试、故障报告生成以及将仿真结果反标到 Midas 等。

故障注入后,安全验证流程从使用 Jasper FSV App 进行故障分析开始。Jasper FSV App 可以通过结构和形式化故障分析,识别出在随后的故障仿真中可以被忽略的不可测试、不可观测和等效的故障点。这大大缩减了故障列表,加快了整个安全验证进程。故障分析后,Xcelium Safety App 利用串行或并发引擎对剩余的故障进行故障注入仿真。

同时,Midas 平台还与 Spectre Simulation Platform 和 Legato Reliability Solution 集成,解决模拟/混合信号故障识别和仿真问题。与数字安全流程类似,Midas 平台可以从 Spectre Simulator 收集模拟设计信息。

兼顾安全的实现流程

Midas 平台支持 FMEDA 驱动的兼顾安全的实现,其中综合工具和布局布线工具可以协同工作。

USF 可以定义安全机制,例如双核锁步、安全岛、三重模块冗余 (TMR)、逻辑隔离等。完成定义后,可以由 Genus Synthesis Solution 生成安全机制。Innovus 可以保存并读取描述安全机制实现的 USF 文件,以便相应地推动物理实现。

Midas Safety Platform 是市场上第一款针对模拟/混合信号和数字方向,真正支持 FMEDA 驱动的安全方法学的解决方案。Midas 平台是所有 Cadence 安全流程的统一控制中心,将 FMEDA 与 SoC 安全验证和兼顾安全的实现联系起来。所有 Cadence 安全流程都使用 USF 作为定义安全意图的基础,从而实现自动化的安全设计、验证和实现。

扫一扫二维码,立即下载技术白皮书

白皮书:《FMEDA 驱动的整体安全设计和验证:面向模拟、数字和混合信号设计》

注:请用公司邮箱注册, 通过Cadence 审核的注册用户,我们将注册成功且通过Cadence审核的用户可获得完整版资料。审核通过后Cadence会将白皮书发送至您的邮箱,提供您的公司邮箱地址通过审核的几率更大哦!

如需了解更多信息, 您也可以点击阅读原文,填写表单申请相关白皮书。