由于存在物理学定律,电阻、电容和电感将继续成为挑战。我们对此无能为力,所以自热离子真空管问世以来,电子设计人员就学会了通过开发巧妙的电路拓扑来解决这些问题。事实证明,物理学就是物理学,过去适用于真空管的理论同样适用于如今的高性能半导体。了解更多信息。

这篇博客文章最初由 United Silicon Carbide (UnitedSiC) 发布,该公司于 2021 年 11 月加入 Qorvo 大家庭。UnitedSiC 是一家领先的碳化硅 (SiC) 功率半导体制造商,它的加入促使 Qorvo 将业务扩展到电动汽车 (EV)、工业电源、电路保护、可再生能源和数据中心电源等快速增长的市场。

任何东西都打破不了物理定律。电阻器会将电能转为热能耗散,同时降低电压;电容器需要时间来储存和释放电荷;电感器需要时间来产生和消除电磁场。我们对此无能为力,所以自热离子真空管问世以来,电子设计人员就学会了通过开发巧妙的电路拓扑来解决这些问题。事实证明,物理学就是物理学,适用于真空管的理论同样适用于如今的高性能半导体。

以米勒效应为例。20 世纪 20 年代,美国电气工程师 John Milton Miller 发现将简单三极真空管用作放大器时,栅极与阳极之间存在内部电容,这会导致一个问题。当电容阻抗随工作频率的上升而下降时,会施加越来越多的负反馈,从而降低放大器的带宽。

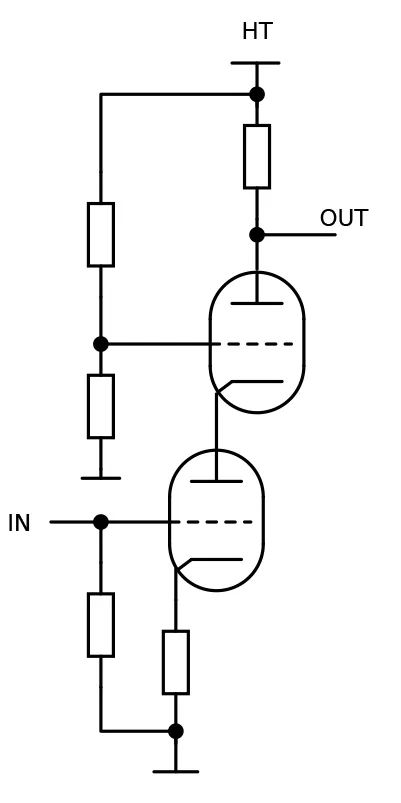

Miller 发现采用级联三极管或共源共栅拓扑结构,将两个三极真空管串联可减少输入至输出的总电容,如图 1中所示。鉴于上部电子管栅极处于固定电压下,所以上部三极真空管的阴极电压由下部三极真空管控制。开发出带内部屏栅极的四极管后,这种内部电容及其相关影响就会降低,从而制造出工作频率为数百兆赫的单管放大器。

图 1:初始的级联三极管或共源共栅电路

当设计人员开始使用固态半导体替换热离子真空管时,米勒效应又出现了,并且开始再次限制高频操作。

为什么会这样?在基于 MOSFET 的开关电路中,米勒效应会限制开关速度,因为驱动电路必须以可靠的低损耗方式对输入电容进行充放电。这种米勒电容效应(即 CGD)会随着栅极电压的不同而变化。

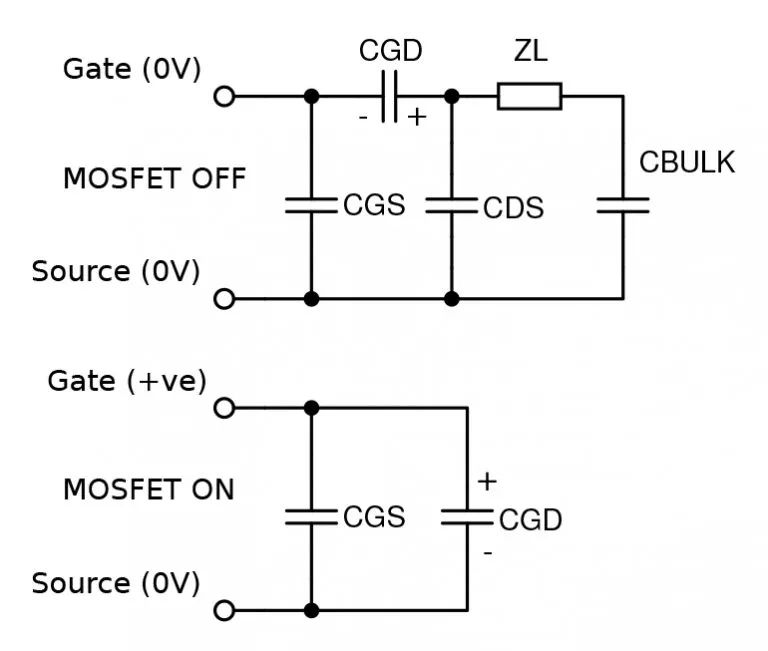

例如:考虑使用在栅极费电压为 0V 时关断的增强模式 MOSFET 开关。总栅极输入电容如同一个网络(见图 2),包括 CGS、CGD、CDS、负载 ZL 以及大电容 CBULK。此外,CGD 两端为正电压。MOSFET 接通时,漏极电压降至几乎为零,且总电容变为 CGD 与 CGS 并联,与断开状态相比,CGD 两端为负电压。在接通到断开以及断开到接通的开关过程中,输入电容必须在上述情况之间切换。

图 2:断开和接通时,MOSFET 的等效输入电容

图 2:断开和接通时,MOSFET 的等效输入电容

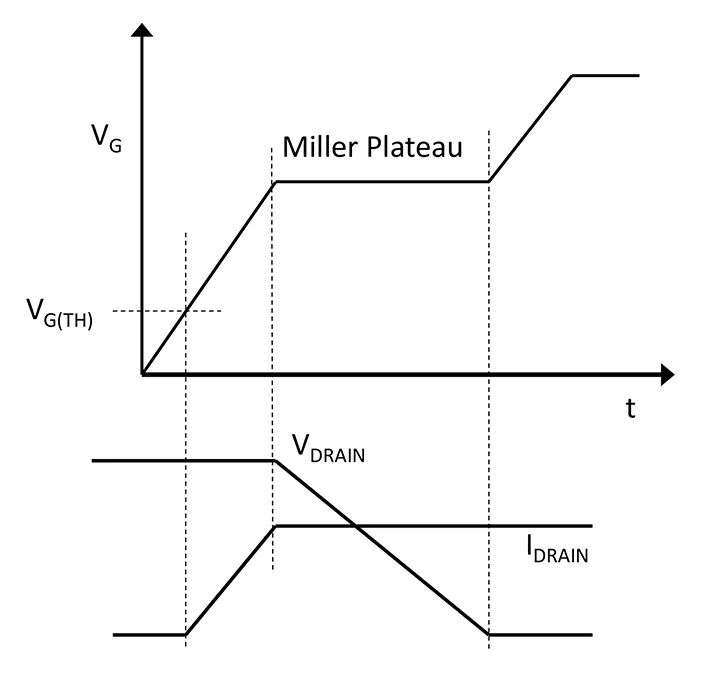

MOSFET 栅极开关波形中正向部分的平稳段(见图 3)表示两个输入电容状态之间的过渡,因为驱动器必须突然提高工作负荷,所以转换速度变慢。更糟糕的是,当漏极电压下降时,会试图“推动”栅极负压经过 CGD,与正导通电压命令相抵触。当断开 MOSFET 时,这个过程就会反过来。CGD 会试图“拉动”栅极正电压,所以我们鼓励使用 MOSFET 和 IGBT 的设计人员使用负的关态栅极电压来抵消这种影响。这会反过来增加驱动栅极所需的功率。

图 3:栅极驱动电压的米勒电容 “平稳段”

图 3:栅极驱动电压的米勒电容 “平稳段”

器件的栅极-漏极电容 (CGD) 会受半导体器件的架构影响,其变化因器件是横向构建还是纵向构建而异。我们可以通过缩小 CGD 来获得低电压 MOSFET,但这在高压下会变成一个问题,尤其是当设计人员想要使用碳化硅 (SiC) 或氮化镓 (GaN) 等材料构建宽带隙器件时。有些物理问题是无法回避的:这些技术的开关速度仍受限于其米勒电容,而使用共源共栅电路拓扑是消除这种影响的最佳方法。

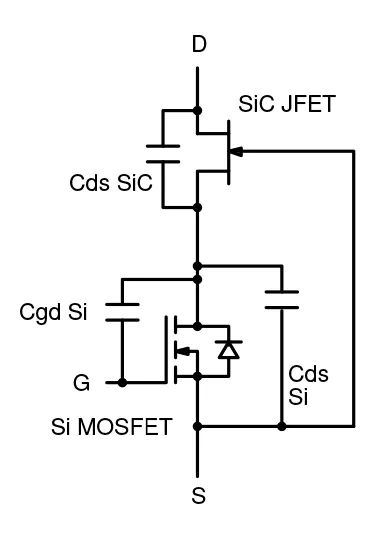

LINKS NEEDED 基本的 SiC 开关使用结 FET (JFET) 架构。如果 JFET 为纵向结构器件,则其 CGD 可以达到较有利的低点,且其漏极-源极电容 CDS 还可以更低。但是,JFET 为常开器件,其栅极电压为 0 V,需要负栅极电压才能关断。这是桥式电路中存在的一个问题。在桥式电路中,所有器件在瞬时通电时默认为导通状态。最好使用常闭器件来构建此类电路,该器件可通过将 Si MOSFET 和 SiC JFET 布置在级联型拓扑中来实现,见图 4。

图 4:Si/SiC 共源共栅

当 MOSFET 的栅极和源极电压均为 0 V 时,其漏极电压会上升。JFET 栅极也为 0V,所以当其源极电压(来自 MOSFET 漏极)上升至 10 V 时,JFET 栅极与源极之间的负电压为 -10V,从而会使 JFET 关断。当 MOSFET 栅极为正时,MOSFET 处于接通状态,并且会使 JFET 的栅极-源极短路,从而接通 JFET。这种电路拓扑可实现 MOSFET 栅极电压为 0V 的常闭器件。此外在该拓扑中,串联输入-输出电容(包括 JFET 的 CDS)接近于 0,从而可以减少米勒效应及其对高频增益的影响。

在开关时,由于 JFET 的源极电容 CDS 几乎为零而 MOSFET 的 CDS 不为零,所以 Si MOSFET 漏极电压会 “全然涌入” JFET 漏级,使得 MOSFET 漏极始终保持在低电压状态。换句话说,MOSFET 可以是低电压类型,且漏极与源极间导通电阻非常低,因此栅极驱动变得更容易。其另一个优势在于,低电压 MOSFET 的体二极管具有非常低的正向压降,且快速恢复性能出色。JFET 没有体二极管,所以在换向桥接电路或同步整流等应用中,需要进行第三象限换向开关导通时,MOSFET 体二极管就会导通。这会将 JFET 栅极-源极电压保持在大约 +0.6 V,确保能够硬接通 JFET,使反向电流以低压降流动。

SiC 共源共栅拓扑能够解决米勒电容问题,同时轻松实现栅极驱动、常关运行和高性能体二极管。这与 SiC MOSFET 和 GaN HEMT 均不同——前者的体二极管的性能比较差,后者的 CDS 比较高。物理学定律的不变性导致了热离子器件中出现限制高频增益的米勒效应,也在半导体器件中带来了许多问题。然而,这种不变性也意味着基于共源共栅的解决方案在现代 SiC 器件中的作用与在老式真空管中的一样有效。事物越是看似在变,就越是亘古不变。

https://unitedsic.com/downloads/

了解更多有关 UnitedSiC 以及共源共栅优势的信息。