- 第88期 -

PART 01

失效模式

首先,何谓失效?

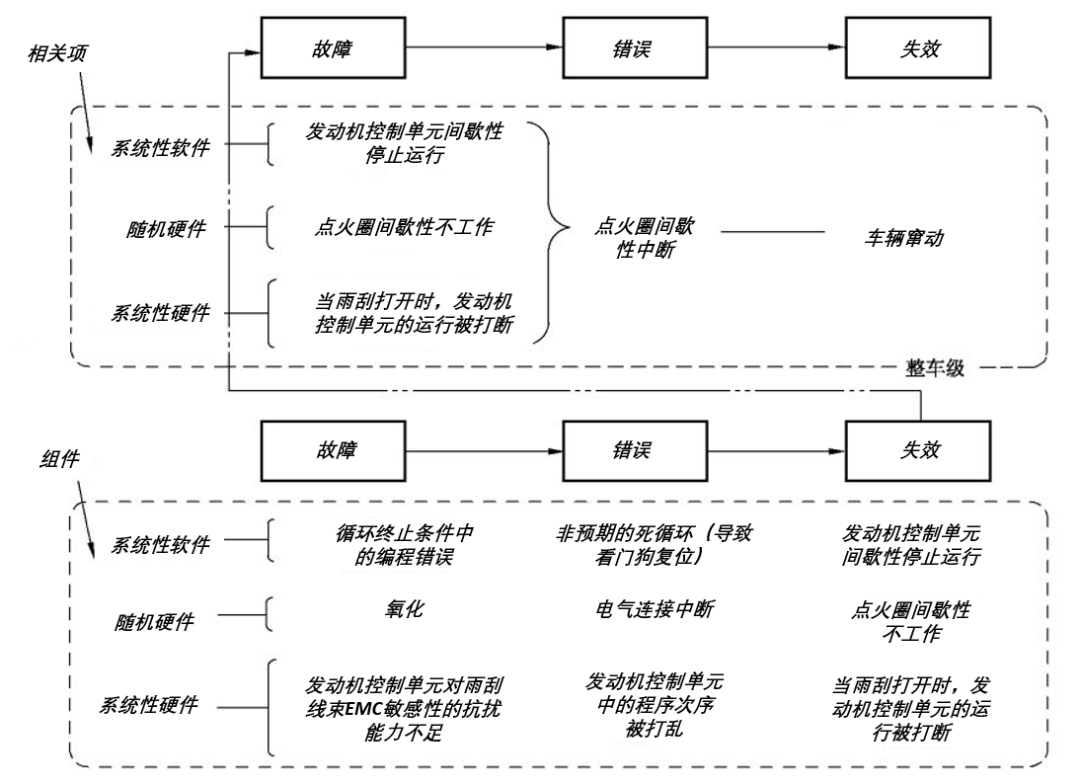

ISO 26262中对“故障”、“错误”、“失效”的定义如下:

故障(Fault): 可引起要素或相关项失效的异常情况。

错误(Error): 计算的、观测的、测量的值或条件与真实的、规定的、理论上正确的值或条件之间的差异。

失效(Failure):要素按要求执行功能的能力的终止。

同一个层级中,故障是失效的原因,失效是故障的结果;错误是故障的表现形式。

不同层级间,组件层级的失效最终会引发系统层级的故障。

如上图故障分为三类:

系统性软件故障

系统性硬件故障

随机硬件故障

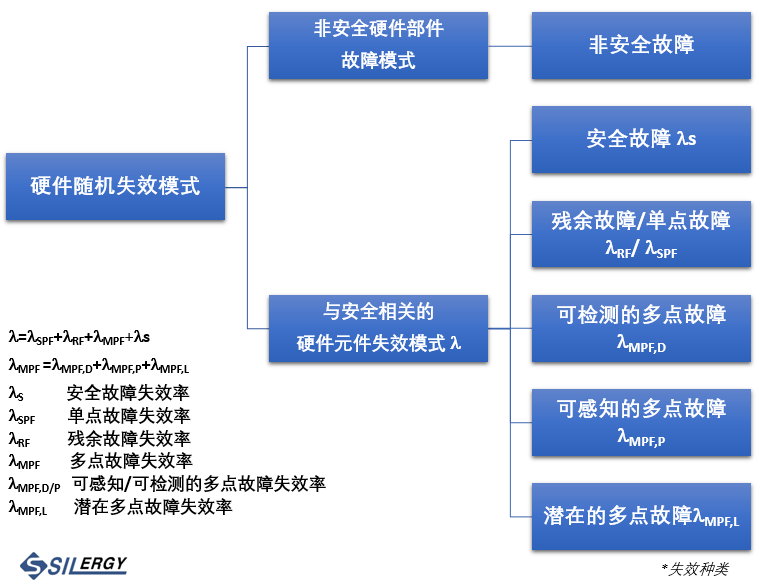

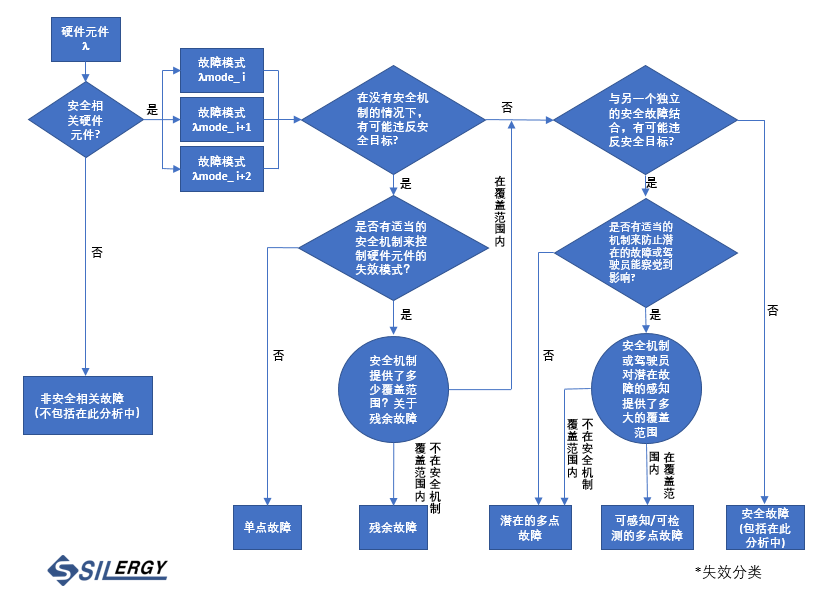

这里我们重点讨论随机硬件故障。一块ECU由数以万计的元器件组成,每个元器件都有发生随机失效的可能,但并不是所有元器件的失效都会导致违背安全目标;有些元器件的失效会直接导致违背安全目标;而有些元器件需要与另一个元器件同时发生失效才会违背安全目标。因此,我们将随机硬件故障类型进行进一步的细分为:单点故障、 残余故障、 可探测的双点故障、可感知的双点故障、 潜伏的双点故障和安全故障等。

1.单点故障

直接导致违背安全目标;

硬件要素故障,对于该硬件要素,没有任何安全机制预防其某些故障违背安全目标。

2.残余故障

可直接导致违背安全目标

硬件要素的故障,对于该硬件要素,有至少一个安全机制预防其某些违背安全目标的故障。

3.可探测的双点故障

仅与另一个(双点故障有关的)独立硬件故障联合才能导致安全目标的违背。

被防止其潜伏的安全机制所探测。

4.可感知的双点故障

仅与另一个(双点故障有关的)独立硬件故障联合才能导致安全目标的违背

在规定的时间内被驾驶员所感知(有或无安全机制探测)。

5.潜伏的双点故障

仅与另一个(双点故障有关的)独立硬件故障联合才能导致安全目标的违背。

不被安全机制所探测也不被驾驶员感知。直到第二个独立故障发生前,系统始终可以运行且驾驶员也不知道发生了故障。

6.安全故障

指某个故障,它不会显著地增加违反安全目标的概率。

PART 02

FMEDA

什么是FMEDA?

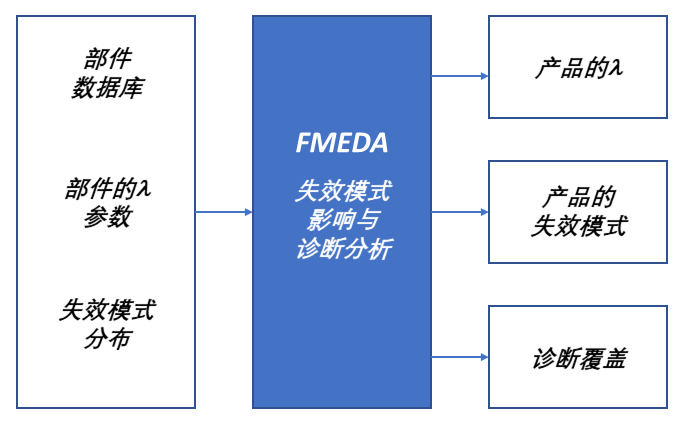

FMEDA-失效模式影响与诊断分析(Failure Mode Effect and Diagnostic Analysis)是产品设计定量分析的基础,可以用来分析整个系统也可以用来分析系统的某个模块单元。

系统失效的过程往往是从单元(器件)的异常情况(故障)开始导致测量值与规定值不符(误差),最终使系统或单元失去执行某项功能的能力(失效)。失效率指系统或零件在单位时间内失效的概率,其单位通常用FIT表示,1FIT=10-9 /h。

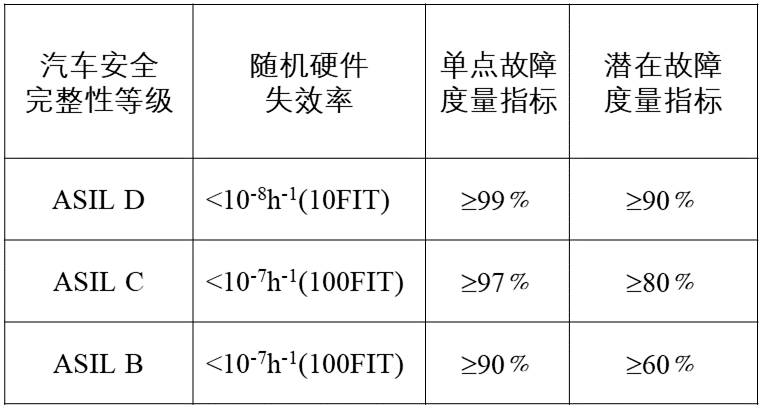

产品设计过程中, FMEDA可以同时分析以上三个指标,度量产品的硬件设计是否符合相应的安全要求。产品设计的过程中SPFM 和LFM 可以用来验证硬件构架设计应对随机失效的鲁棒性,PMHF用来评估随机硬件失效率导致违反安全目标的风险已经足够小。

FMEDA计算公式:

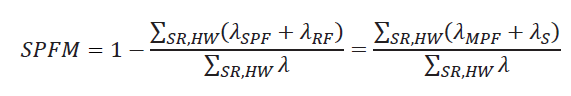

1.单点故障度量指标SPFM:

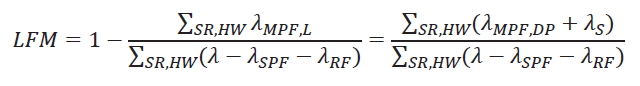

2.潜在故障度量指标LFM:

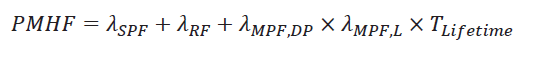

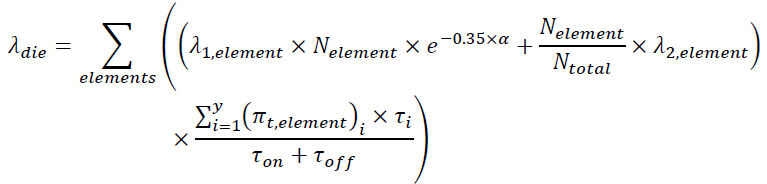

3.随机硬件失效率PMHF:

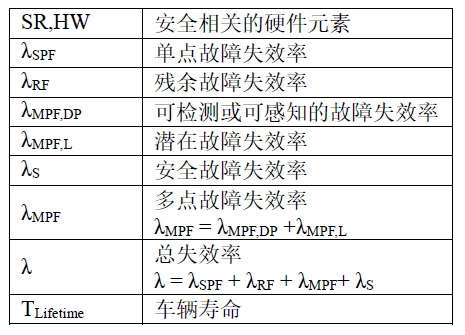

上式中各个符号的含义如下:

下面的公式为IEC TR 62380中关于半导体的可靠性数学预测模型:

其中各个参数含义如下:

裸片失效率λdie:

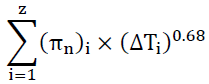

对于某一种器件工艺类型,λ1和λ2均可以通过查表法获得,N可以通过芯片设计EDA工具统计得到,器件工艺类型的温度系数:

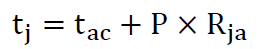

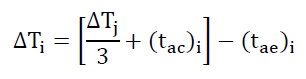

参数πt是器件工艺类型在对应的芯片结温tj下获得的,芯片的结温tj可以通过以下公式计算得到:

其中,tac即为工作剖面中的参数,Rja为封装的热阻,P为芯片的功耗。

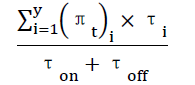

其中各项参数都和工作剖面有关,即产品在完成规定任务这段时间内所经历的时间和环境的时序描述。芯片在工作时环境温度是在不停变化的,同时也存在运行状态和非运行状态。

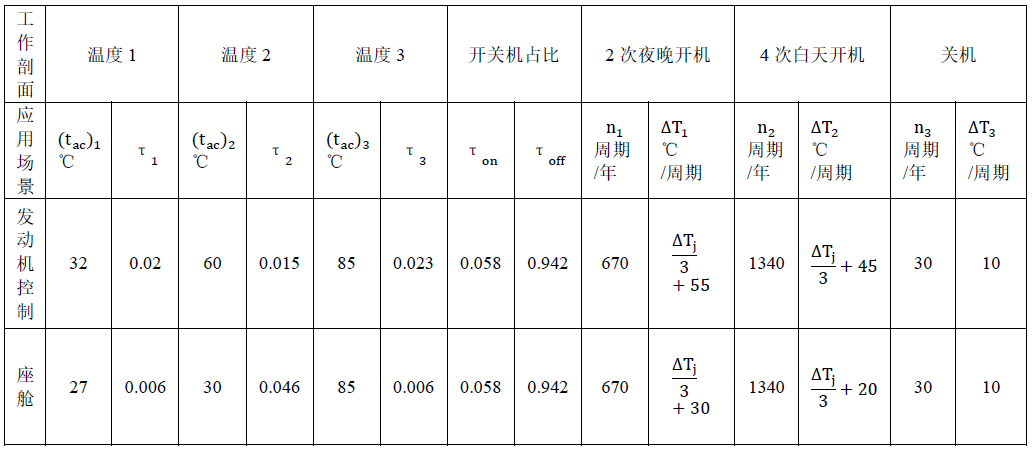

IEC TR 62380中列举了如下表的2种典型的工作剖面,带入工作剖面前半部分的各项参数,即可获得对应的温度系数。

裸片中往往混合着多种工艺类型的器件,可以通过叠加求和的方式得到整个裸片的失效率。其中由于λ2是有关集成电路工艺技术的失效率,和晶体管数量无关,因此λ2推荐在叠加求和的时候要根据各个工艺器件的晶体管数N进行加权平均得到。因此对于混合工艺的裸片的失效率计算公式如下:

封装失效率λpackage:

对于某一特定封装,πα和λ3均可以通过查表法简单计算获得,而温度循环系数:

其中的各项参数也都和工作剖面后半部分的参数有关,根据IEC TR 62380:

ni表示的为1年内的循环次数,每年不使用车辆的天数为30天,则使用的天数为335天,进而夜晚启动的次数为每年670次,相应的白天启动的次数为每年1340次,则:

其中,(tac)i取工作剖面中的加权平均值计算得到(tac)i=60℃,(tae)i则根据下表给出:

可见,通过“世界范围”方式计算出的结果和在工作剖面中直接给出的公式是一致的。

另外,λpackage是包括了封装内部的失效率(框架连接和焊盘)和封装外部与PCB的焊点失效率,作为芯片开发者,FMEDA只要在计算的时候考虑其中占比80%的封装内部的失效率即可。

电过应力失效率λoverstress:

由于λEOS电子过应力属于系统性失效,因此在FMEDA时,这部分不应该被计算在内。

由于不同的产品应用导致的危害不同,ISO26262引入了安全等级和量化指标。FMEDA作为定量分析的核心技术得到从业者越来越多的关注。

矽力杰致力于为您提供全球最优的模拟芯片解决方案,

其他方案敬请继续关注。

矽力杰官网:

http://www.silergy.com

地址:

杭州市滨江区联慧街6号矽力杰大厦

联系电话:

+86-571-87759971