CMOS逻辑电路的制造技术是超大规模集成电路(VLSI)半导体工业的基础。

3.1 逻辑技术及工艺流程3.1.1 引言

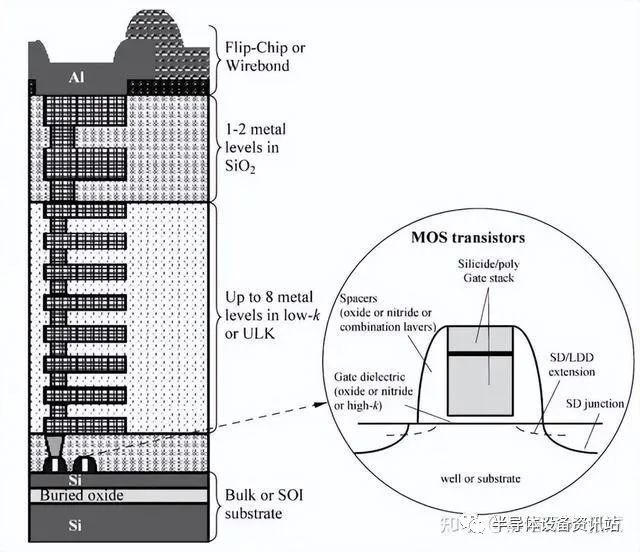

本节将介绍CMOS超大规模集成电路制造工艺流程的基础知识, 重点将放在工艺流程的概要和不同工艺步骤对器件及电路性能的影响上。图3.1显示了一个典型的现代CMOS逻辑芯片(以65nm节点为例) 的结构,包括CMOS晶体管和多层互联。典型的衬底是P型硅或绝缘体上硅(SOI),直径为200mm(8″)或300mm(12″)。局部放大图显示出了CMOS晶体管的多晶硅和硅化物栅层叠等细节,由多层铜互连,最上面两层金属较厚,通常被用于制造无源器件(电感或电容),顶层的铝层用于制造封装用的键合焊盘。

图3.1 现代CMOS逻辑芯片结构示意图

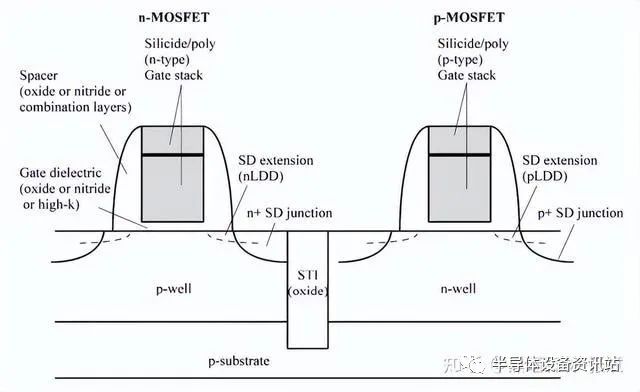

现代CMOS晶体管的主要特征如图3.2所示。在90nm CMOS节点上,CMOS晶体管的特征包括钴-多晶硅化物或镍-多晶硅化物多晶栅层叠、氮化硅栅介质、多层(ONO)隔离、浅源/漏(SD)扩展结和镍硅化物SD深结。

内部核心逻辑电路的晶体管典型操作电压(1~1.3V),其沟道长度更短(50~70nm),栅介质更薄(25~30Å), SD扩展结更浅(200~300Å)。IO电路的晶体管(即是连接芯片外围电路的接口)的典型操作电压是1.8V、2.5V或3.3V,相应的其沟道更长(100~200nm),栅介质更厚(40~70Å),SD扩展结更深(300 ~500Å)。核心逻辑电路较小的操作电压是为了最大限度减小操作功耗。在65nm及45nm CMOS节点,另一个特点是采用了沟道工程 ,通过沿晶体管沟道方向施加应力来增强迁移率(例如张应力对NMOS中电子的作用和压应力对PMOS中空穴的作用)。未来CMOS在 32nm及以下的节点还会有新的特点,例如新的高k介质和金属栅层叠 , SiGe SD ( 对于PMOS ),双应变底板,非平面沟道 (FinFET)等。

图3.2 CMOS晶体管(包括NMOS和PMOS)

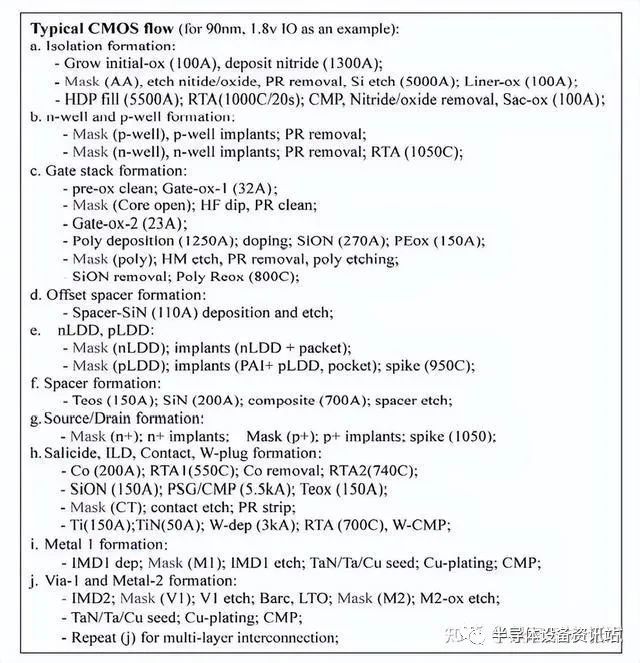

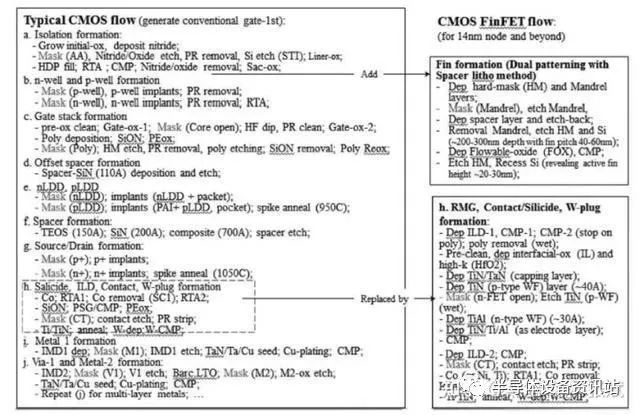

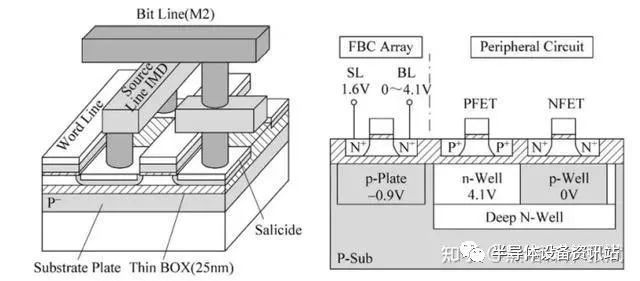

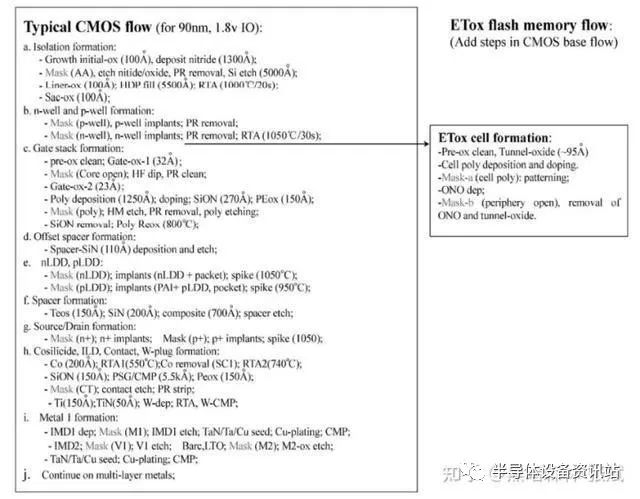

现代CMOS逻辑工艺流程的顺序如图3.3所示,工艺参数对应于90nm节点。CMOS逻辑超大规模集成电路的制造通常是在P型硅或绝缘体上硅(SOI)上,直径为200mm(8″)或300mm(12″)。

工艺首先形成浅槽隔离(STI),然后形成n-阱区域(对于PMOS晶体管)和p-阱区域(对于NMOS晶体管)并分别对阱区域进行选择性注入掺杂。然后为NMOS和PMOS晶体管生长栅氧,接下来形成多晶栅层叠。多晶栅层叠图形化以后形成再氧化,补偿和主隔离结构,接着完成NMOS和PMOS的LDD和源/漏注入掺杂。

在这之后,沉积一层介质层,通过图形化,刻蚀和钨塞(W-plug)填充形成接触孔。至此, NMOS和PMOS晶体管已经形成了,这些工艺步骤通常被称为前端制程(FEOL)。然后通过单镶嵌技术形成第一层铜(M1),其他的互连通过双镶嵌技术实现。后端制程(BEOL)通过重复双镶嵌技术实现多层互连。

图3.3 CMOS晶体管和金属互连的制造流程

图3.3中,步骤(a)~步骤(h)用于实现CMOS晶体管,称为前端制程(FEOL);步骤(i)~步骤(j)用于重复制造多层互联,称为后端制程(BEOL)。最顶层的两层金属和铝层被用于制造无源器件和键合焊盘,没有在这里进行介绍。

3.1.2 CMOS工艺流程

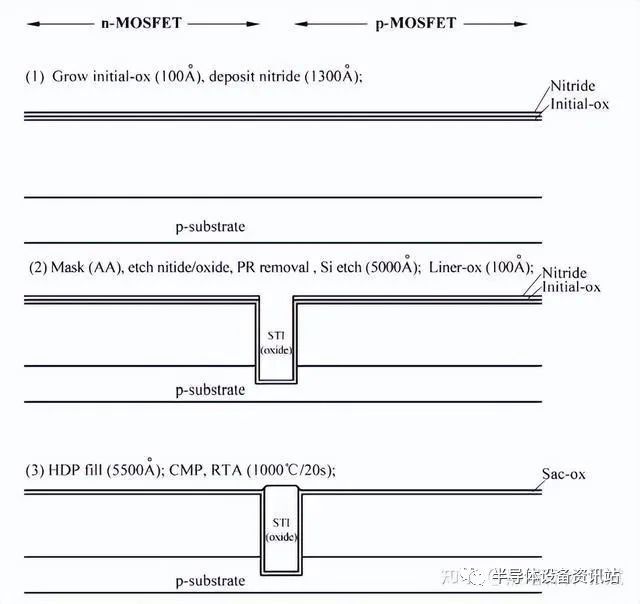

1.隔离的形成

浅槽隔离(STI)的形成如图3.4所示,工艺参数对应于90nm节点。工艺首先对硅衬底进行热氧化(被称作初始氧化,initial-ox),厚度100Å,然后通过LPCVD的方式沉积一层氮化硅(1300Å)。接下来进行光刻,首先旋涂一层光刻胶(PR),然后进行紫外线(UV)曝光,光刻胶通过光刻版(被称作AA)显影,有源区不会受到紫外线 的照射(或者说隔离区域将会曝露在紫外光下)。

在这之后,氮化硅和初始氧化层通过离子干法刻蚀的方法除去,去掉光刻胶后进行Si的刻蚀,露出的氮化硅充当刻蚀的硬掩模,通过离子刻蚀在Si衬底上刻蚀出浅槽(5000Å)。当然,掩模材料(例如PR一类的软掩模和氮化硅之类的硬掩模)必须足够厚,能够经受得住后续对氮化硅、二氧化硅和硅的离子刻蚀。

图3.4 浅槽隔离(STI)形成的图解

在硅槽形成以后,进行氧化已在槽内形成一层“衬里”,接下来通过CVD的方法在槽内填充氧化物(厚度稍微超过槽的深度)并且进行快速热退火(RTA)使CVD沉积的氧化物更加坚硬。在这之后通过化学机械研磨(CMP)的方式使得表面平坦化,随后去除残余的氮化硅和二氧化硅。接下来,在表面生长一层新的热氧化层(被称作牺牲氧化层或SAC-ox)。相对于以前的LPCVD沉积氧化物工艺,高离子密度(HDP)CVD有更好的间隙填充能力,因此被广泛地用于现代 CMOS制造工艺(例如0.13μm节点及更新的技术)。

2.n-阱和p-阱的形成

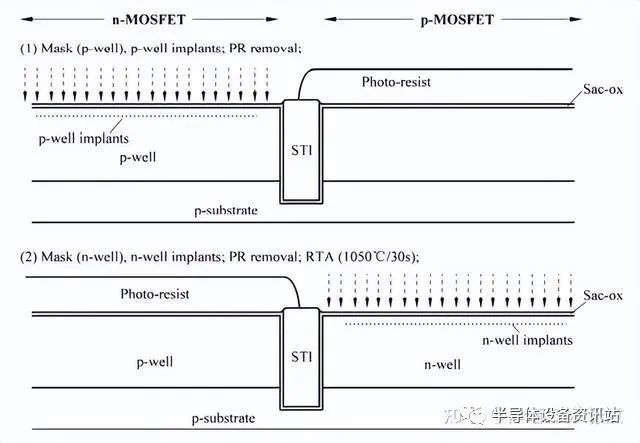

n-阱和p-阱的形成如图3.5所示,包括掩模形成和穿过薄牺牲氧化层(SAC-ox)的离子注入。n-阱和p-阱的形成顺序对最终晶体管的性能影响很小。后面会在n-阱中形成PMOS,在p-阱中形成NMOS,因此,n-阱和p-阱的离子注入通常是多路径的(不同的能量/剂量和种类),这些注入不仅用于阱的形成,同时也用于PMOS和NMOS阈值电压Vt 的调整和防止穿通。n-阱离子注入后使用RTA激活杂质离子推进杂质深度。

图3.5 n-阱和p-阱的形成的图解

3.栅氧和多晶硅栅的形成

双层栅氧和硬掩模栅层叠示意图如图3.6所示。用湿法去掉Sac-ox以后,通过热氧化生长第一层栅氧(为了高质量和低内部缺陷),然后形成打开核心区域的掩模(通过使用掩模core),接着浸入到HF溶液中,随后在核心区域通过热氧化的方式生长晶体管的第二层栅氧。

注意到 I/O 区域经历了两次氧化,因此正如所期待的,I/O晶体管的栅氧要更厚一些。当核心区域和 I/O 区域都已经生长了晶体管以后,沉积多晶硅层和硬掩模层(薄的SiON和PECVD二氧化硅)。在沉积了栅层叠之后,将硬掩模进行图形化(使用掩模poly,并用对多晶硅表面有高选择性的离子刻蚀二氧化硅和SiON),然后去除光刻胶,使用SiON和二氧化硅做硬掩模刻蚀多晶硅。去除SiON以后,使用氧化炉或快速热氧化(RTO)形成多晶硅栅层叠侧壁的再氧化(30Å),来对氧化物中的损伤和缺陷进行退火(对栅层叠的离子刻蚀可能导致损伤或缺陷)。因为栅的形状决定了晶体管沟道的长度,也即决定了 CMOS节点中的最小临界尺寸(CD),因此它需要硬掩模方案而不是光刻胶图形化方案来对栅层叠进行图形化,以期获得更好的分辨率和一致性。

图3.6 栅氧和栅层叠形成的图解

两次栅氧化的结果使得I/O晶体管的栅氧较厚(没有在这里显示出来)而核心晶体管的栅氧较薄。相对于简单的光刻胶图形化方案,硬掩模方案可以获得更好的分辨率和一致性。

4.补偿隔离的形成

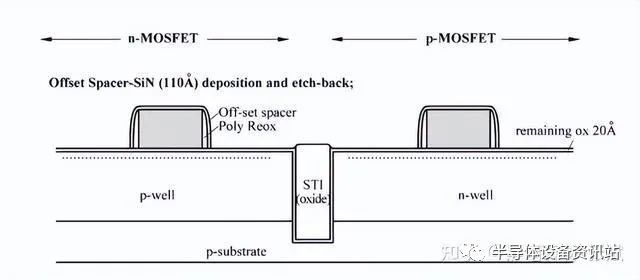

补偿隔离的形成如图3.7所示。沉积一薄层氮化硅或氮氧硅(典型的厚度为50至150Å),然后进行回刻蚀,在栅的侧壁上形成一薄层隔离。补偿隔离用来隔开由于LDD离子注入(为了减弱段沟道效应)引起的横向扩散;对于90nm CMOS节点,这是一个可以选择的步骤,但对于65nm和45nm节点,这一步是必要的。在补偿隔离刻蚀后,剩下的氧化层厚度为20Å,在硅表面保留一层氧化层对于后续每步工艺中的保护而言是十分重要的。

图3.7 补偿隔离的形成

补偿隔离可以补偿为了减少段沟道效应而采取的LDD离子注入所引起的横向扩散。

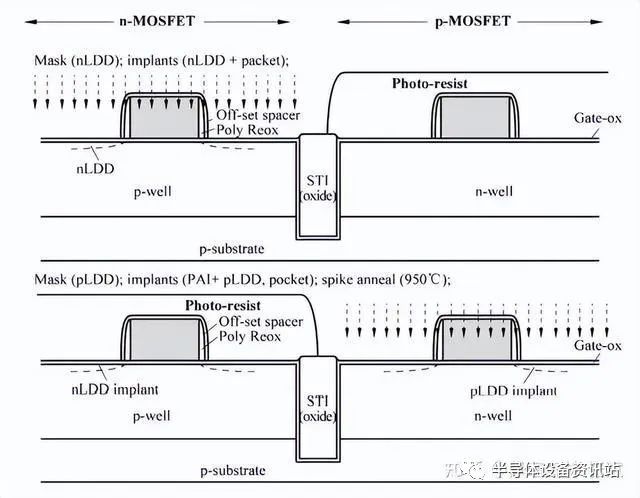

5.nLDD和pLDD的形成

有选择的对n沟道MOS和p沟道MOS的轻掺杂漏极(LDD)离子注入如图3.8所示。完成离子注入后,采用尖峰退火技术去除缺陷并激活LDD注入的杂质。nLDD和pLDD离子注入的顺序和尖峰退火或RTA的温度对结果的优化有重要影响,这可以归因于横向的暂态扩散。

图3.8 nLDD和pLDD形成的图解

6.隔离的形成

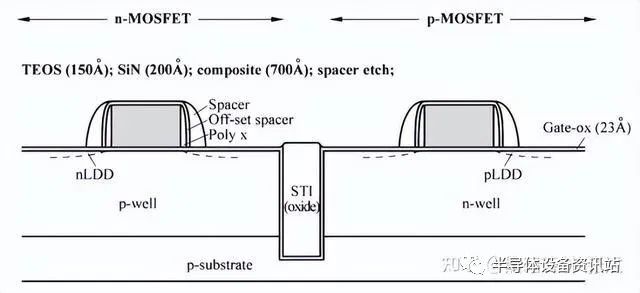

接下来是主隔离的形成,如图3.9所示。沉积四乙基原硅酸盐-氧化物(Teos-oxide,使用Teos前驱的CVD氧化物)和氮化硅的复合层,并对四乙基原硅酸盐-氧化物和氮化硅进行离子回刻蚀以形成复合主隔离。隔离的形状和材料可以减小晶体管中热载流子的退化

图3.9 隔离形成的图解

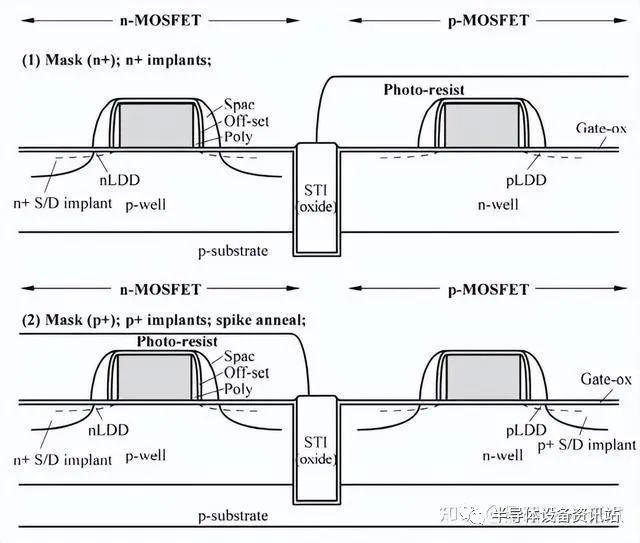

n+ , p+ 的源和漏(S/D)的形成如图3.10所示。RTA和尖峰退火被用来去除缺陷并激活在S/D注入的杂质。注入的能量和剂量决定了S/D的节深并会影响晶体管的性能,较浅的源漏节深(相对于 MOSFET的栅耗尽层宽度)将会显著地减小短沟道效应(SCE)

图3.10 源漏形成的图解尖峰退火被用来去除缺陷并激活在S/D注入的杂质

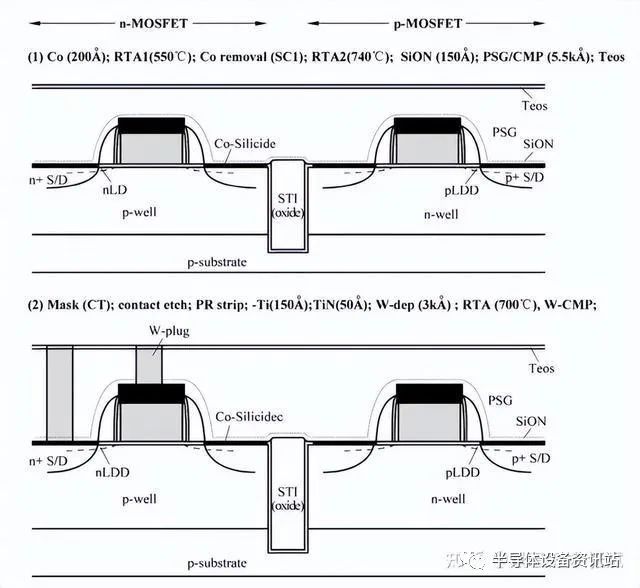

7.自对准多晶硅化物,接触孔和钨塞的形成

自对准多晶硅化物,接触孔和钨塞的形成如图3.11所示。在湿法清洁去除有源区(AA)和多晶硅栅表面的氧化物以后,溅射一薄层 (200Å)钴(Co),紧接着进行第一次RTA(550℃),和硅接触的钴将会发生反应。然后,氧化硅上剩余的没有反应的钴将用SC1溶剂去掉,并进行第二次RTA(740℃)。因此,有源区和多晶硅栅区域会 以自对准的方式形成钴的硅化物,这被称为自对准多晶硅化物工艺。

图3.11 自对准多晶硅化物,接触孔和钨塞形成的图解

然后,通过沉积氮氧硅(150Å)和磷硅玻璃(PSG,5.5kÅ)形成多金属介质(PMD),并使用CMP进行平坦化。沉积一层CVD氧化物 (Teos-oxide)用来密封PSG。然后形成打开接触孔的掩模(掩模CT),随后刻蚀接触孔上的PSG和SiN。接下来溅射Ti(150Å)和 TiN(50Å),用CVD法沉积钨(W,3kÅ)并用RTA(700℃)进行 退火。Ti层对于减小接触电阻十分重要,侧壁上覆盖的TiN用以保证W 填充工艺的完整性 ,使得填充到接触孔中的W没有空隙。对钨表面进行抛光(使用CMP)直到露出Teos-oxid表面,此时接触孔内的钨塞就形成了。

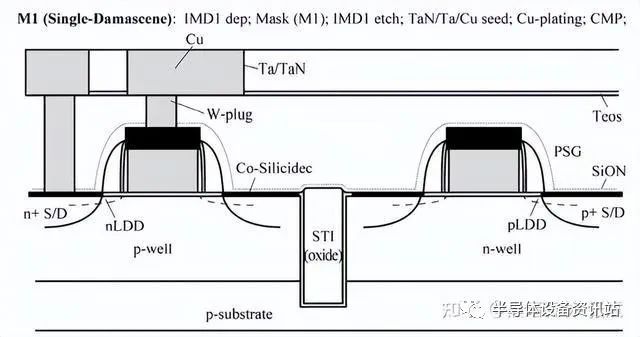

8.金属-1的形成(单镶嵌)

这之后沉积金属间介质层(IMD),例如SiCN(300Å)含碳低k PECVD氧化硅(2kÅ)和Teos-oxide(250Å),并进行图形化(使用 掩模metal-1)和氧化物刻蚀。IMD1层主要是为了良好的密封和覆盖更加多孔的低k介质。然后沉积Ta/TaN和铜种子层,随后填充铜(通过ECP法)并用CMP进行平坦化。金属-1互连就形成了。这是单镶嵌技术 ,见图3.12。

图3.12 通过单镶嵌技术实现金属-1的图解

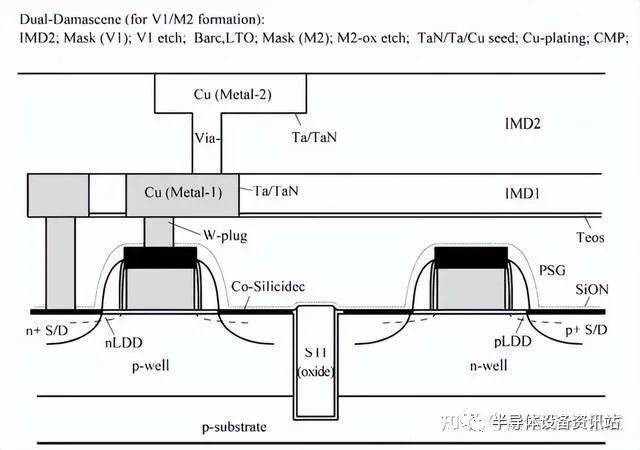

9.通孔-1和金属-2的形成(双镶嵌)

通孔-1和金属-2互连的形成是通过先通孔双镶嵌工艺实现的, 如图3.13所示。首先沉积IMD2层(例如SiCN 500Å,含碳低k PECVD 氧化硅-黑金刚石6kÅ),然后形成通孔-1的图形并进行刻蚀。多层的 IMD1主要是为了良好的密封和覆盖更加多孔的低k介质。然后在通孔中填充BARC(为了平坦化)并沉积一层LTO。随后形成金属-2的图形并可使氧化物。去除BARC并清洗后,沉积Ta/TaN和Cu种子层,随后进行Cu填充(使用ECP法)并进行CMP平坦化,这样金属-2互连就形成了。这就是双镶嵌工艺。通过重复上述的步骤,可以实现多层互连。

图3.13 通过双镶嵌工艺实现通孔-1和金属-2的图解

3.1.3 适用于高k栅介质和金属栅的栅最后形成或置换金属栅CMOS工艺流程

CMOS逻辑产品工艺流程是制造32nm或更早工艺节点的主导工艺流程,如图3.14中左边所示。随着CMOS工艺特征尺寸继续按比例缩小到28nm及更小时,需要采用能够减少栅极漏电流和栅极电阻的高k栅介质层和金属栅电极以提高器件速度。

这些新功能通过采用栅最后形成或置换金属栅(Replacement Metal-Gate,RMG)工艺成功地整合到CMOS制造工艺流程当中,它类似于栅先形成的常规CMOS工艺流程,只是在S/D结形成后,多晶硅栅极材料被移除并且被沉积的高k介质层和金属层所取代。以这种方式,可以降低高k材料的总热预算,提高高k栅介质层的可靠性。RMG形成之后,继续常规的流程,如接触电极,金属硅化物(接触区域内形成的)和钨插栓工艺流程。继续完成后段工艺流程,形成第1层铜(M1)(单镶嵌)和互连 (双镶嵌)结构。

图3.14 高k栅介质和金属栅电极特性,通过采用后形成栅(Gate-last)或置换金属栅极

(RMG)工艺,已成功地整合到CMOS工艺流程当中,其中多晶硅担任“虚拟”栅的作用,在 S/D结形成之后被除去,被沉积的高k电介质层和金属层所取代。

3.1.4 CMOS与鳍式MOSFET(FinFET)

伴随着CMOS器件工艺特征尺寸持续地按比例缩小到14nm及以下技术节点以后,通过采用三维器件结构,从垂直方向进一步增大沟道宽度,进而增加沟道电流。这种具有垂直方向沟道的新颖三维晶体管被称为鳍式场效应晶体管或FinFET。

目前成熟的14nm节点制造工艺,在单一方向,晶圆上组成沟道的鳍片薄而长,宽为7~15nm,高为15~30nm,重复间距为40~60nm。图3.15给出鳍式场效应晶体管集成制造工艺流程,采用了间隔墙双重图案化技术来形成鳍 片并采用RMG流程来形成高k介质与金属栅极。

图3.15 随着CMOS持续缩小到14nm以下技术节点以后,可以通过在垂直方向形成沟道来增强沟道电流,形成所谓的FinFET(其工艺流程如图所示,其中在目前14nm工艺节点,采用了间隔墙双重图案化技术来形成鳍片。鳍片宽为7~15nm,高为15~30nm,重复间距为40~60nm)

3.2 存储器技术和制造工艺3.2.1 概述

在广泛应用于计算机、消费电子和通信领域的关键技术中,半导 体存储器技术占有一席之地。存储器的类别包括动态随机读取存储器 (DRAM)、静态随机读取存储器(SRAM)、非易失性存储器 (NVM)或者闪存(Flash)。当传统的CMOS技术在65nm及以后的 节点面临速度与功耗的折中时,应变工程和新型叠栅材料(高k 和金 属栅)可以将CMOS技术扩展到32nm以及以后的节点。然而在接近 32nm节点时,高层次的集成度导致在功耗密度增加时速度却没有提 升。有一种方法可以在系统层面降低功耗和提升速度,那就是将存储 器和逻辑芯片集成在一起构成片上系统(SoC)。有趣的是,DRAM 和闪存基于单元电容、选择晶体管和存储单元的尺寸缩小却导致了日 益复杂化的工艺流程与CMOS基准的偏差。因此,如果基于当前的 CMOS与存储器集成技术,要实现存储与逻辑集成在SoC上的应用将 是一个巨大的难题。

幸运的是,最近在集成领域有一些非常重大的进展,比如铁电材 料(如PZT(PbZrxTixO3 ),SBT(SrBi2Ta2O9 ),BTO(Bi4Ti3O12 )体系),结构相变(如GST硫化物合金),电阻开关(如 perovskite氧化物(SrTiO3 ,SrZrO3 (SZO),PCMO,PZTO等), 过渡金属氧化物(如Ni-O,Cu-O,W-O,TiON,Zr-O,Fe-O等), 以及加速铁电存储器(FRAM)发展出的旋转隧道结(如MgO基的磁 性隧道结)、相变存储器(PCRAM)、电阻存储器(RRAM)和磁性 存储器(MRAM)等。另外,这些各式各样的存储器在CMOS后端线 的集成与前端线流程完全兼容。因此,不仅这些存储器在将来有希望 替代NVM和eDRAM,而且逻辑和存储一起都可以很容易被集成到 MOS基准上。

3.2.2 DRAM和eDRAM

DRAM是精密计算系统中的一个关键存储器,并且在尺寸缩小和高级芯片设计的推动下向高速度、高密度和低功耗的方向发展。尽管DRAM的数据传输速度已达到极限并且远远低于当前最新科技水平的微处理器,但它仍然是目前系统存储器中的主流力量。

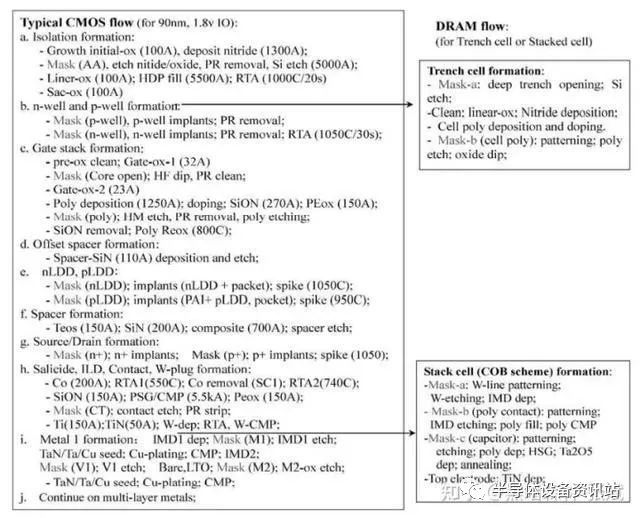

基于深槽电容单元或堆栈电容单元有两种最主要的DRAM技术。图3.16说明了在CMOS基准上添加深槽电容与堆栈电容流程来形成DRAM的工艺流程。堆栈单元在CMOS晶体管之后形成,主要应用于独立的高密度DRAM。深槽单元可以在CMOS晶体管构建之前形成,更适合嵌入式DRAM与逻辑的集成。然而,深槽工艺造价很高,同时在深槽周围可能会形成缺陷。图3.17展示了一个DRAM单元的深槽和传输晶体管的横截面。

图3.16 带有深槽电容和堆栈电容单元的DRAM的工艺流程

图3.17 带有深槽电容和镍硅化传输晶体管的嵌入式DRAM的截面图

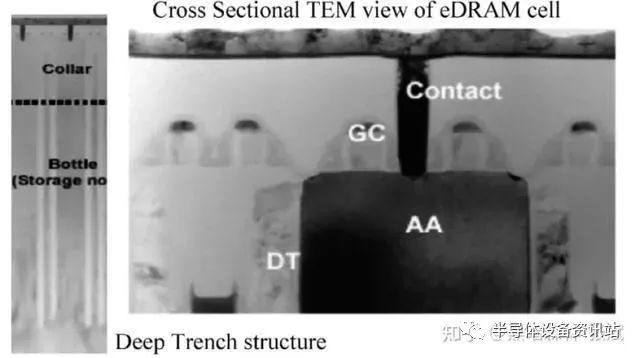

浮体单元是相当有前景的一种结构,它通过将信号电荷存储在浮 体上,产生或高或低开关电压和源漏电流(代表数字1或0)。这种浮 体单元结构已经在90nm技术节点下成功地应用于SOI和小单元尺寸 (4F2 )的体硅,可无损读取操作,具有良好的抗干扰能力和保存时 间。写操作可以基于接触电离电流或者GIDL(写1时)以及前向偏置 结(写0时)。因为结处漏电的缘故,SOI上FBC-DRAM的潜在记忆时 间要比在体硅上的久一些。整个制造流程和标准的CMOS完全兼容, 更加适合eDRAM应用。基于SOI的浮体结构的DRAM如图3.18所示。

图3.18 基于SOI的浮体结构的DRAM示意图

3.2.3 闪存

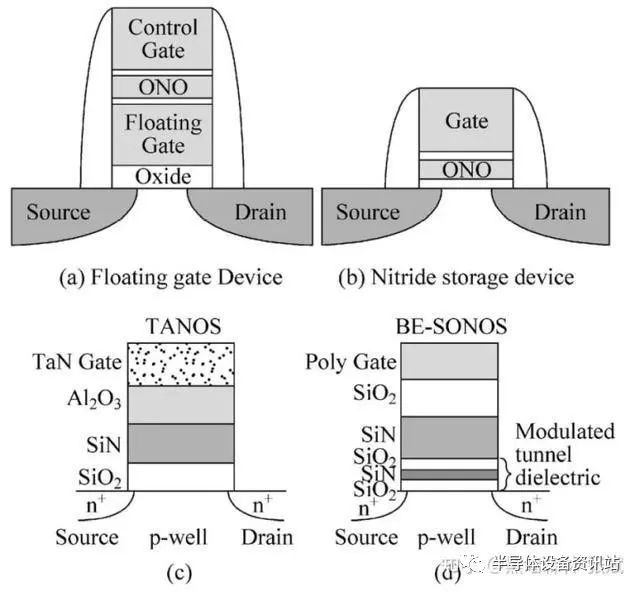

闪存自1990年以来就作为主流NVM被迅速推动发展,这也归结于数据非易失性存储、高速编程/擦写、高度集成等方面快速增长的需求。闪存是基于传统的多层浮栅结构(比如MOSFET的多层栅介质),通过存储在浮栅上的电荷来调制晶体管的阈值电压(代表数据1和0)。写和擦除的操作就简单对应为浮栅上电荷的增加和去除。

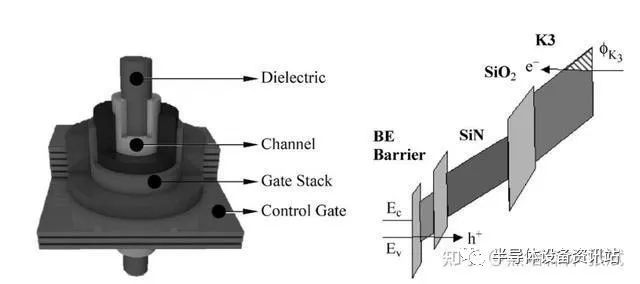

目前的闪存大体有NOR与NAND两种结构,它们的集成度已达到Gb量级,但局限也非常明显,比如高操作电压(10V),慢擦写速度 (1ms)和较差的耐久性(105 )。目前的NAND市场已经超越了DRAM在2006年时的市场容量。图3.19说明了一种典型双浮栅单元(被称作ETox单元)的工艺流程。这种浮栅单元(ETox)的尺寸很难 降到45nm节点,特别是由于浮栅的缘故导致相邻单元之间的干扰随尺寸减小而增大。图3.20展示了最新的进展,包括SONOS单元、电 荷陷阱式TANOS单元、带隙工程SONOS单元等,其中带隙工程 SONOS单元中,氮化层是用作电荷陷阱的(代替ETox单元中的浮栅)。

图3.19 一种典型的浮栅ETox闪存的工艺流程

图3.20 传统浮栅单元的示意图

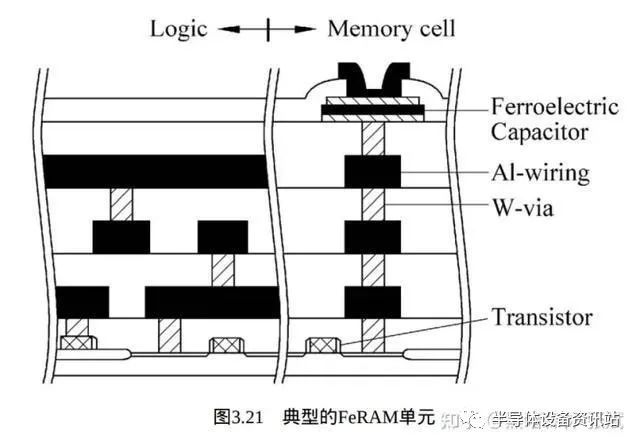

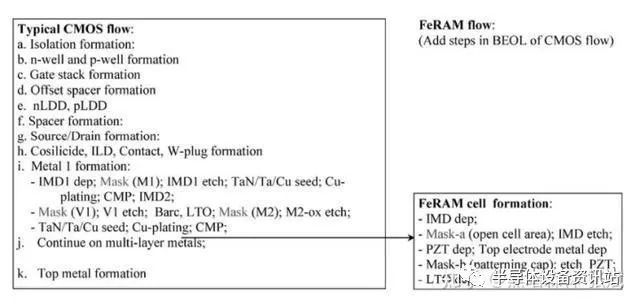

3.2.4 FeRAM

FeRAM基于电容中的铁电极化,(相对于传统的浮栅闪存)有低功耗、低操作电压(1V)、高写寿命(1012 )和编程快(<100ns)等优点。铁电MiM电容(见图3.21)可与后端制程(BEOL) 集成,电容被完全封闭起来(避免由磁场强度引起的退化)。铁电电容的工艺流程如图3.22所示。

FeRAM中研究最多的材料是PZT(PbZrxTixO3 ),SBT(SrBi2Ta2O9 ),BTO(Bi4Ti3O12 ),它们拥有抗疲劳、工艺温度低、记忆性好、剩余极化高等令人满意的特性 。 一晶体管一电容(1T1C)(作为非挥发存储单元)的单元结构是最常用的;而1T2C和2T2C单元则对工艺偏差有更强的适应性,并有更好的性能。需要注意的是拥有铁电栅介质的FET单元由于较差的记忆 性(几小时或几天)而使其应用受到限制,并且与前端制程 (FEOL)不兼容。

图3.22 一种典型的包含一个选择晶体管和MiM电容FeRAM单元的工艺流程

3.2.5 PCRAM

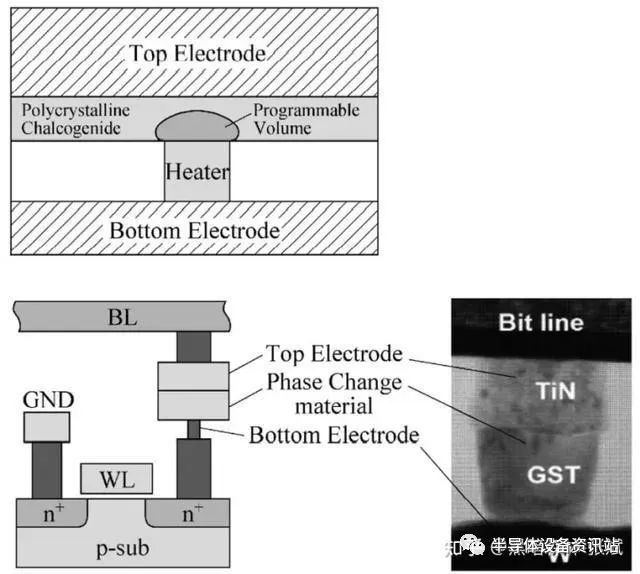

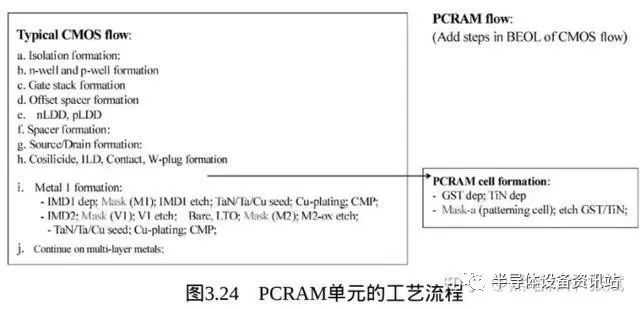

相变存储器顺利地朝向低操作电压、高编程速度、低功耗、廉价 和高寿命(~108~1014 )的方向发展,这种技术有望在未来取代NOR/NAND甚至是DRAM。相变存储器最常见的材料是在“蘑菇”形单元(见图3.23)中的带有掺杂(一些N和O)的GST硫化物合金(一种介于GeTe和Sb2Te3 之间的伪二元化合物)。减小单元结构中用于转换无定形(高阻)和晶化(低阻)状态的底部加热器尺寸和材料的临界体积可以获得更小的RESET电流。结晶化和结构弛豫的原理最终限制了尺寸和可靠性,超薄的相变材料厚度为3~10nm。工艺流程如图 3.24所示。PCRAM单元可以在钨塞上制成,其代价是仅仅在BEOL中 增加一块掩模版,其他所有流程与标准CMOS流程一致。

图3.23 PCRAM蘑菇型单元

3.2.6 RRAM

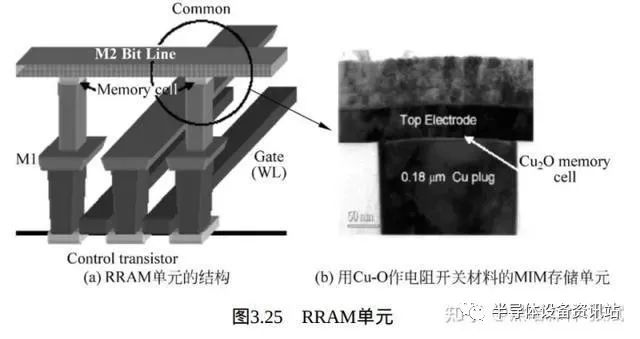

双稳定态电阻开关效应被发现存在于钙钛矿氧化物(如SrTiO3,SrZrO3(SZO),PCMO,PZTO)、过渡金属氧化物(如Ni-O,Cu-O,W-O,TiON,Zr-O,Fe-O)、固体电解质甚至聚合物中。开关机制(而不是结构相变)主要基于导电纤维的生 长和破裂,这与金属离子、O离子/空穴、去氧化、电子俘获/ 反俘获(mott过渡)、高场介电击穿和热效应有关。

RRAM单元主要 包括一个选择晶体管和一个MIM(金属-绝缘体-金属)电阻作为电阻开关材料(见图3.25)。RRAM看上去比较有前景缘于其可扩展性、 低电压操作以及和BEOL的兼容性(特别是以基于Cu-O和W-O的单 元)。目前,RRAM的耐久性在~103~105 之间。RRAM的工艺流程如图3.26所示。

图3.26 后端制程中制造在Via-1上的Cu-O基RRAM的工艺流程

3.2.7 MRAM

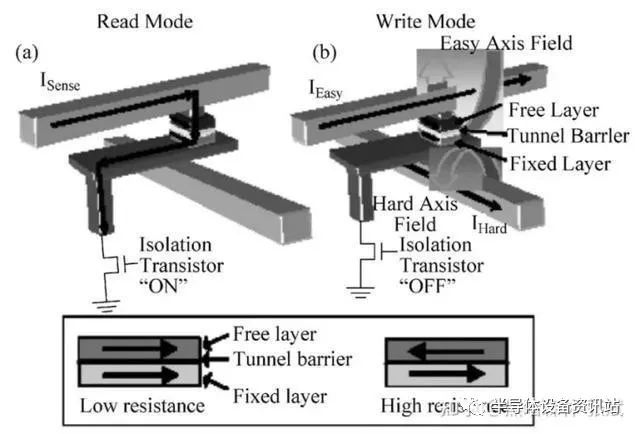

磁性隧道结(MJT),通常是2层铁磁层夹着一层薄绝缘壁垒层,显示出双稳定态的隧穿磁电阻(TMR),作为MRAM中的存储单元。TMR是由于“自由”的铁磁层相对于“固定”层自旋平行或反平行而产生的。

CoFeB/MgO/CoFeB结构的MTJ可以产生高达约500%的TMR比率(也就是说约5倍于传统基于Al-O的MJT) 。典型的MRAM单元 有1T-1MJT(即一个MJT垂直在一个MOS晶体管上),并且可以被2种阵列机制操纵开关,即场开关(由相邻的X/Y写入线产生 的磁场控制)和旋转扭矩开关(由通过MJT直接电流控制)。

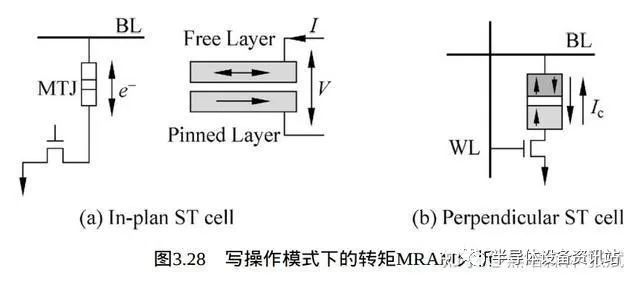

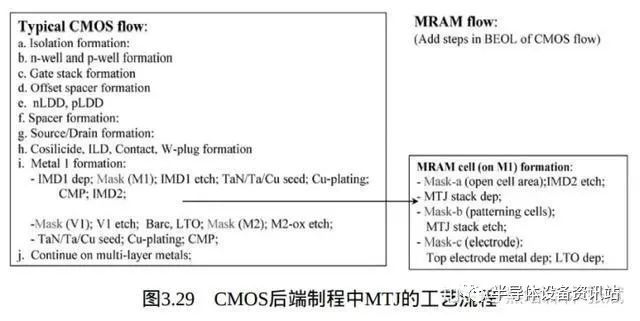

Freescale做了一款4Mb MRAM投入量产(基于0.18μm CMOS),基于旋转场开关(“切换”机制),如图3.27所示。旋转扭矩MRAM(见图3.28)使用了自旋极化电流通过MJT来对自由层的自旋极性进行开关操作,最近已展现出低写入电流(<106 Å/cm2 ,在10ns脉冲下),好的保留性(>10年),小单元尺寸( 6F2 ),快速读取 (30ns)和好的耐久性(1014 )。这个成果正积极展开工业化并且在取代DRAM、SRAM和Flash上展现了很好的前景。MJT的处理流程如图3.29所示。

图3.27 读模式和写模式下的场开关MRAM单元磁性隧道结中磁场层如小图所示

3.2.8 3D NAND

自1984年日本东芝公司提出快速闪存存储器的概念以来,平面闪 存技术经历了长达30年的快速发展时期。一方面,为了降低成本,存 储单元的尺寸持续缩小。但随着闪存技术进入1x nm技术节点,闪存单 元的耐久性和数据保持特性急剧退化,存储单元之间的耦合不断增 大,工艺稳定性和良率控制问题一直无法得到有效解决,从而从技术 上限制了闪存单元的进一步按比例缩小。另一方面,代替传统的浮栅 闪存存储器,通过按比例缩小的方式实现高密度集成,寻找更高密度 阵列架构的努力从未停止,三维存储器的概念应运而生。

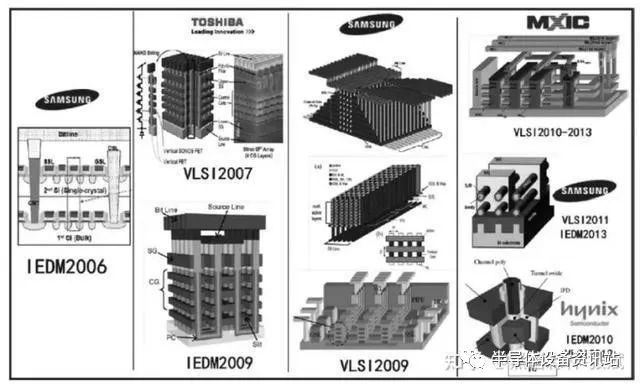

2001年,Tohoku大学的T. Endoh等人在IEDM上首先报道了基于多 晶硅浮栅存储层的堆叠环形栅的闪存概念,2006年,韩国三星电子公司的S. M. Jung在IEDM上报道了基于电荷俘获存储概念的双层闪 存阵列的堆叠结构。但直到2007年日本东芝公司的H. Tanaka在 VLSI会议上报道了BiCS(Bit-Cost Scalable)NAND闪存结构 [56] ,三 维存储器的研发真正成为各大存储器公司和科研院所的重要研发方 向。之后韩国三星电子公司先后提出了TCAT(Terabit Cell Array Transistor) 、VSAT(Vertical-Stacked-Array-Transistor)和VG-NAND(Vertical Gate NAND)结构 ,日本东芝公司提出了P-BiCS(Pipe BiCS)结构,韩国海力士半导体公司提出了STArT结构,台湾旺宏公司也提出了自己的VG NAND结构,这些结构 均采用了电荷俘获存储(charge trapping)的概念;美国美光公司和韩 国海力士公司也提出了基于多晶硅浮栅存储层的三维存储器结构。各研究机构与公司开发的不同架构三维存储器如图3.30所示。

图3.30 各研究机构与公司开发的不同架构三维存储器

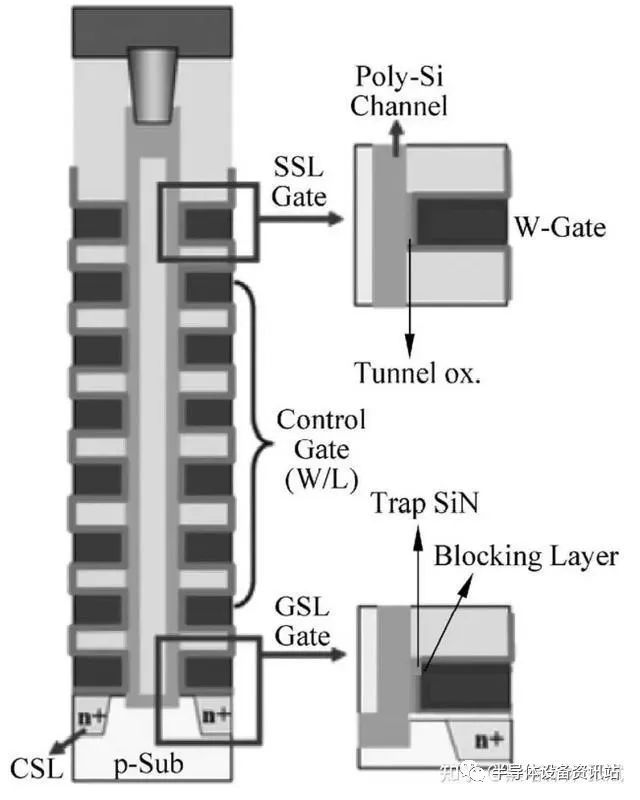

对于这些不同架构的存储器来说,按照存储层的材料可以分为三 维浮栅存储器和三维电荷俘获存储器。前者主要由美国美光公司推 介,在2015年底完成了技术上的准备,由于采用多晶硅浮栅作为存储 层,存储单元面积更大,在实现更多层存储单元层叠时工艺难度较 大,因此主要是通过把外围电路置于存储阵列下面来实现面积的缩 减。对于三维电荷俘获存储器,又可以划分为垂直栅型和垂直沟道 型。台湾旺宏公司推出的基于垂直栅结构的三维电荷俘获闪存结构, 工艺上要难于垂直沟道型,一直未见其宣告量产。垂直沟道型三维电 荷俘获存储器是最早实现大规模量产的闪存产品,2013年8月,三星电 子公司推出了第一代24层的三维垂直沟道型电荷俘获三维存储器, 2014年7月推出了第二代32层128Gb产品,2015年推出了48层256Gb的 产品。事实上,三星电子公司的垂直沟道型三维电荷俘获存储器单元 也是基于无结场效应晶体管结构,如图3.31所示。该芯片具有24层堆 叠的字线(WL)。除最底层的单元选择晶体管为常规反型工作模 式,其余每个字单元晶体管均为基于电荷捕获闪存无结薄膜晶体管 (JL Charge Trap Flash Thin-film Transistor,JL-CTF TFT)。该器件关 闭时要求多晶硅薄膜沟道(管状)处于全耗尽状态;因此,多晶硅薄 膜厚度(TCH)要尽量薄。此外,进一步增加存储单元密度的强劲需 求,也在不断推动缩小多晶硅薄膜沟道TCH。与工作在反型模式 (IM)的器件相比,该产品表现出更优异的性能,可提供更快速的写 入/擦除(P/E)速度,更大的内存窗口(>12V)和更好的耐力(> 104 次);在150℃测试条件下,还具有优良的10年数据保留能力。更 为出色的是该器件开关电流比大于 108 ,同时具备非常陡峭的亚阈值 摆幅(SS) 。

图3.31 基于电荷捕获闪存无结薄膜晶体管,镶嵌金属栅的三维垂直堆栈(V-NAND)闪存器件结构示意图

目前,各个存储器公司也相继发布了各自的闪存量产计划。相比 于三维浮栅闪存,三维电荷俘获闪存具有更好的器件可靠性,垂直沟 道型三维电荷俘获存储器目前已成为国际上最主流的三维存储器,为 了抢占市场有利地位,各大公司的竞争日趋白热化。图3.32为垂直沟 道型三维电荷俘获存储器单元与能带结构示意图。

图3.32 垂直沟道型三维电荷俘获存储器单元与能带结构示意图

垂直沟道型三维电荷俘获闪存的关键技术是超深孔刻蚀和高质量 薄膜工艺。32层的超深孔深宽比接近30:1,上下孔的直径差异要求小 于10~20nm。栅介质多层薄膜不仅要求顶层和底层的厚度基本一致, 对组份均匀性也提出了很高的要求。沟道材料一般为多晶硅薄膜,要 求具有很好的结晶度和较大的晶粒,同时还需要与栅介质之间有低缺 陷密度的界面。作为一种电荷俘获存储器,存储单元之间几乎没有耦 合效应。编程和擦除操作分别使用了电子和空穴的FN隧穿。为了提高 擦除速度,隧穿层通常会使用基于氧化硅和氮氧化硅材料的叠层结 构。存储层一般是以氮化硅为主的高陷阱密度材料。为了降低栅反向 注入,阻挡层则会使用氧化硅或氧化铝等材料。垂直沟道型三维电荷 俘获闪存可靠性方面的最大挑战是电子和空穴在存储层中的横向扩 散,随着三星电子公司推出产品,在存储材料方面的技术瓶颈已经获 得了突破。

3.2.9 CMOS图像传感器

CIS英文全名CMOS(Complementary Metal-Oxide Semiconductor) Image Sensor,中文意思是互补性金属氧化物半导体图像传感器。 CMOS图像传感器虽然与传统的CMOS电路的用途不同,但整个晶圆 制造环节基本上仍采用CMOS工艺,只是将纯粹逻辑运算功能变为接 收外界光线后转变为电信号并传递出去,因而具有CMOS的基本特点 和优势。不同于被动像素传感器(Passive Pixel Sensor),CIS是带有 信号放大电路的主动像素传感器(Active Pixel Sensor)。

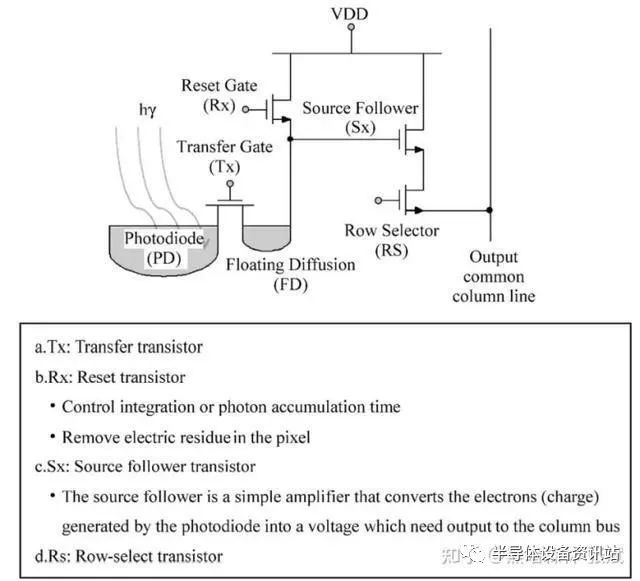

在目前最典型的4-Transistor Pixel Photodiode(像素光电二极管) 设计中,我们通过四个阶段来完成一次光电信号的收集和传递(见图 3.33):第一步打开Tx和Rx晶体管,对光电二极管做放电预处理;第 二步关闭Tx和Rx,通过光电效应让光电二极管充分收集光信号并转化 为电信号;第三步打开Rx,让Floating Diffusion释放残余电荷;第四 步关闭Rx并打开Tx,让光电子从Photodiode抽取到Floating Diffusion 中,最后就可以通过Sx将电荷转换成电压进行放大以提高传输过程中 抗干扰能力,并通过Rs做选择性输出。

图3.33 4T CIS像素单元工作模型

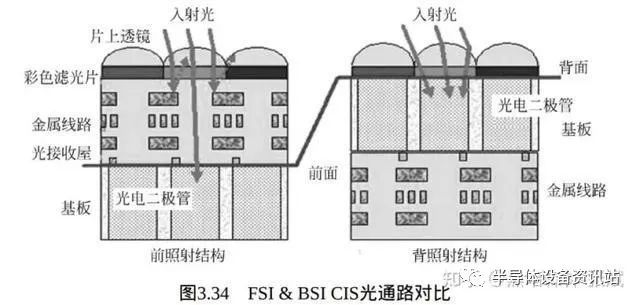

随着图像传感器的应用范围不断扩大,及市场对图像品质要求不 断提高,CIS技术已从传统的FSI(Frontside Illumination)过渡到当下 主流的BSI(Backside Illumination)(见图3.34)。在完成传感器所有 制程后(不包括PAD connection),就可以进入后端BSI制程。其主要步骤如下:

3.3 无结场效应晶体管器件结构与工艺

现有的晶体管都是基于PN结或肖特基势垒结而构建的。在未来的几年里,随着CMOS制造技术的进步,器件的沟道长度将小于10nm。 在这么短的距离内,为使器件能够工作,将采用非常高的掺杂浓度梯 度。进入纳米领域,常规CMOS器件所面临的许多问题都与PN结相 关。传统的按比例缩小将不再继续通过制造更小的晶体管而达到器件 性能的提高。半导体工业界正努力从器件几何形状、结构以及材料方 面寻求新的解决方案。无结场效应器件有可能成为适用于10nm及以下 技术节点乃至按比例缩小的终极器件。无结场效应晶体管与传统反型 模式MOS晶体管或其他结型晶体管相比有以下优点:

①它们与常规 CMOS工艺兼容、易于制作;

②它们没有源漏PN结;

③短沟道效应大 为减弱;

④由于避开了半导体/栅绝缘层粗糙界面对载流子的散射,载 流子受到界面散射影响有限,迁移率不会降低;

⑤由于避开了粗糙表 面对载流子的散射,器件具备优异的抗噪声能力;

⑥放宽了对降低栅极介电层厚度的严格要求;

⑦无结场效应晶体管属于多数载流子导电器件,靠近漏极的电场强度比常规反型沟道的MOS晶体管要低,因此,器件的性能及可靠性得以提高。

一些取代硅作为候选沟道材料 (包括锗硅、锗、III-V族化合物半导体、碳纳米管、石墨烯以及MoS2 等二维材料)在积极的探索与研究当中,甚至真空沟道也在考虑之列。这一新领域有望突破摩尔定律的藩篱,改变微电子学的面貌。新的后CMOS器件需要集成这些异质半导体或其他高迁移率沟道材料在硅衬底上。集成电路器件工艺与材料学家和工程师们要紧密合作,共同迎接未来新的挑战。

常规的CMOS晶体管,从源区至沟道和漏区由两个背靠背的PN结组成,沟道的掺杂类型与其漏极与源极相反。当足够大的电位差施于栅极与源极之间时,电场会在栅氧化层下方的半导体表面感应少子电 荷,形成反型沟道;这时沟道的导电类型与其漏极与源极相同。沟道形成后,MOSFET即可让电流通过,器件工作于反型模式(IM)。由 于栅氧化层与半导体沟道界面的不完整性,载流子受到散射,导致迁 移率下降及可靠性降低。进一步地,伴随MOS器件特征尺寸持续不断 地按比例缩小,基于PN结的MOS场效应晶体管结构弊端也越来越明显。通常需要将一个掺杂浓度为 1×1019cm−3 的N型半导体在几纳米范 围内转变为浓度为1×1018cm−3 的P型半导体,采用这样超陡峭掺杂浓 度梯度是为了避免源漏穿通造成漏电。而这样设计的器件将严重限制器件工艺的热预算。由于掺杂原子的统计分布以及在一定温度下掺杂原子扩散的自然属性,在纳米尺度范围内制作这样超陡峭的PN结变得 极困难,造成晶体管阈值电压下降,漏电严重,甚至无法关闭。这是未来半导体制造业难以逾越的障碍。

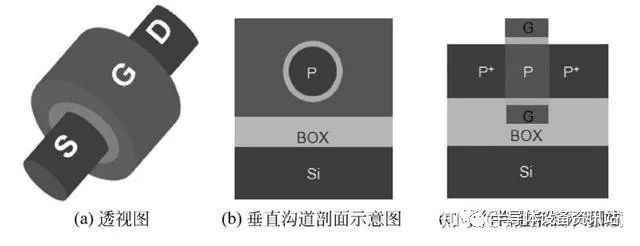

为克服由PN结所构成器件在纳米尺度所面临的障碍,2005年,中 芯国际的肖德元等人首次提出一种圆柱体全包围栅无结场效应晶体管 ( Gate-All-Around-Cylindrical Junctionless Field Effect Transistor , GAAC JLT)及其制作方法,它属于多数载流子导电器件。与传统的MOSFET不同,无结场效应晶体管(JLT)由源区、沟道、漏 区,栅氧化层及栅极组成,从源区至沟道和漏区,其杂质掺杂类型相 同,没有PN结,属于多数载流子导电的器件。图3.35描绘了这种简化 了的圆柱体全包围栅无结场效应晶体管器件的结构透视图和沿沟道及 垂直于沟道方向的器件剖面示意图。在SOI衬底上晶体管有一个圆柱 体的单晶硅沟道,它与器件的源漏区掺杂类型相同(在图中为P 型)。绝缘体栅介质将整个圆柱体沟道包裹起来,在其上面又包裹金 属栅。导电沟道与金属栅之间被绝缘体介质隔离,沟道内的多数载流 子(空穴)在圆柱体沟道体内而非表面由源极达到漏极。通过栅极偏 置电压使器件沟道内的多数载流子累积或耗尽,可以调制沟道电导进 而控制沟道电流。当栅极偏置电压大到将圆柱体沟道靠近漏极某一截 面处的空穴完全耗尽掉,在这种情况下,器件沟道电阻变成准无限 大,器件处于关闭状态。由于栅极偏置电压可以从360°方向将圆柱体 沟道空穴由表及里将其耗尽,这样大大增强了栅极对圆柱体沟道的控 制能力,有效地降低了器件的阈值电压。由于避开了不完整的栅氧化 层与半导体沟道界面,载流子受到界面散射影响有限,提高了载流子 迁移率。此外,无结场效应晶体管属于多数载流子导电器件,沿沟道方向,靠近漏极的电场强度比常规反型沟道的MOS晶体管要来得低, 器件的性能及可靠性得以大大提高。

图3.35 简化的圆柱体全包围栅无结场效应管器件结构示意图

在SOI衬底上的晶体管圆柱体沟道,与器件的源漏区掺有相同类型的杂质(在图中为P型)

我们发展了一种栅极将圆柱体沟道全部包围的GAAC JLT全新制 作工艺,如图3.36所示。首先,在SOI衬底上对N型与P型沟道分别进 行沟道离子注入掺杂,经光刻图形化,刻蚀半导体硅材料层和部分埋 入电介质层(BOX),形成半导体材料柱和电介质支撑柱;接下来, 使用缓冲氧化物蚀刻剂(BOE)进行埋入电介质层横向蚀刻工艺以选 择性地去除显露的底切部分氧化物使电介质支撑柱的中段形成镂空, 形成接近立方体形状的硅纳米桥;经多次氧化与氧化物去除将其圆角 化处理,最后在氢气氛围下进行高温退火,形成圆柱体硅纳米线桥; 接下来,在衬底上沉积栅介质层及金属层将中段镂空处圆柱体硅纳米 线全部包裹;经光刻,刻蚀金属层形成金属栅极;形成绝缘体介质侧 墙结构,对圆柱体硅纳米线两端的暴露部分进行与器件沟道掺杂类型 相同的离子注入重掺杂,形成源区和漏区,最后源漏区形成镍硅化物 以降低接触电阻。