PMOS管、NMOS管的对比

在CMOS设计里,PMOS管和NMOS管同等重要,不过因为一般的电路设计书籍都注重NMOS管的讲解,PMOS都是直接类比NMOS,所以让人不太清楚PMOS的工作原理。

1. 端口不同

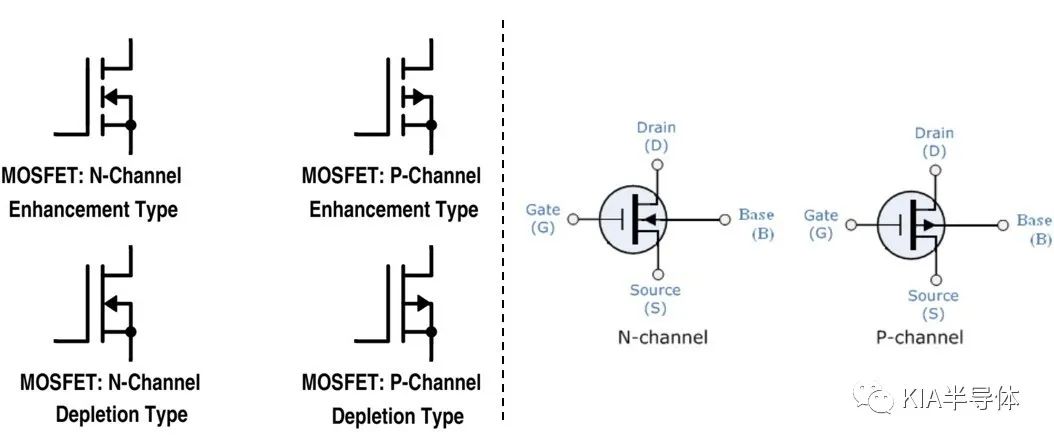

PMOS和NMOS的源漏方位相反,NMOS的漏端drain在上面,PMOS的源端source在上面,之所以这么做是借助方位来表明电位的高低。

NMOS的漏端drain和PMOS的源端source的电压都比栅端gate电压高,所以这么标注获得一个“visual aid”。电流方向是一致的,如果采用箭头表示电流方向,都是从上到下的。

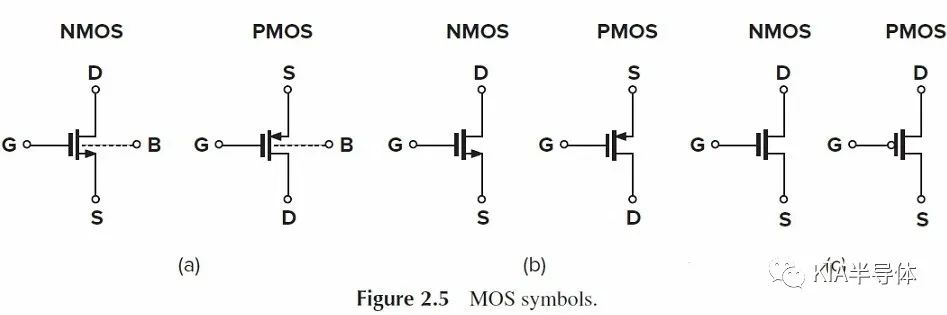

MOS符号

用于表示NMOS和PMOS晶体管的电路符号如图2.5所示。

图2.5(a)中的符号包含所有四个端子,基板用“B”(大块)而不是“S”表示,以避免与源混淆。PMOS器件的源极位于顶部作为视觉辅助,因为它具有比栅极更高的电势。

由于在大多数电路中,NMOS和PMOS器件的主体端子分别接地和VDD,因此我们通常在图中省略这些连接[图2.5(b)]。

在数字电路中,通常使用图2.5(c)中所示的两种类型的“开关”符号,但我们更喜欢图2.5(b)中的符号,因为S和D之间的视觉区别有助于理解电路的操作。

如果是四端口画法,箭头的方向就不是电流方向,而是衬底和沟道之间的PN结方向,和二极管一样,都是从P端指到N端。如下图所示。

NMOS是N型沟道,P型衬底,衬底接最低电位,PMOS是P型沟道,N型衬底接最高电位。这样是为了源漏端和衬底形成P-N结反偏,不然电流从源漏端直接正向导通到地。

击穿说的也是这个P-N结反向击穿。因为沟道和衬底的材料不同,所以栅压变化才会有耗尽层-反型层形成的说法。

NMOS的沟道材料是N型,而衬底材料是P型,所以栅极需要加正电压,才能排斥P型衬底里的空穴,吸引电子聚集在沟道的下方,和栅极的金属板构成栅电容。电容的介质材料是SiO2。

PMOS的沟道材料是P型,而衬底材料是N型,要想在N型材料里吸引空穴的话,自然栅极应该加负电压。和NMOS栅极正电压越大,沟道的导电能力越强一样,PMOS是栅极电压负向越大,沟道导电能力越强。

问题:MOS管是多数载流子导电,为什么,有什么好处?

空穴:带正电,实际中不存在,为方便处理设置的,是电子行为的反向等效。

说完栅极,我们说衬底极substrate。NMOS的衬底极接地,PMOS的衬底极接正电压,这都是根据P-N结反偏要求设定的。

也就是P极接负,N极接正。衬底的电压简单的是直接就近连接,NMOS一般和源端一起接地,PMOS衬底和源端一起连 VDD 。

2. 工作条件不同

1.沟道形成条件

NMOS,VGS>Vth和VDS>VGS-Vth,前者是用来保证导电沟道的形成,叠加后者的条件就是饱和状态。

导通条件到PMOS这,是以栅端电压对比衬底电压VDD较小为好,这样空穴就会被吸附到表面形成沟道,所以可以看出阈值电压Vth为负值。

这和NMOS的Vth的正值恰相反,注意这里不涉及增强型还是耗尽型管子的区分。考虑衬底和源端相连,导通条件是VGS<Vth,如果用绝对值表示|VGS|>|Vth|。

电流的流动从方位上和NMOS没有区别,都是从上方流到下方。

2.饱和条件

饱和区的条件类比较为麻烦,因为饱和区形成的微观机理稍微复杂一点。首先我们要弄清,为什么对于NMOS,当VDS>VGS-Vth就有ID饱和呢?

当满足了VGS>Vth,沟道里从漏端到源端的电压都是一样的,可以等效为简单的平行板电容器。

但是MOS管是个立体结构,除了平行板的垂直电场,要形成电流还需要水平方向的电场,也就是从漏极到源级的电场。水平方向的电场NMOS是漏端最高,源端最低,沿着沟道方向电势逐渐降低。

沟道处的电势由固定的衬底电势叠加水平方向的电势,就造成了栅平行板电容虽然栅极电压不变,但衬底边的电压不均匀。

对于NMOS来说,需要保证VGS>Vth,这里S换成sub(衬底)会更好理解,VG-Sub>Vth,但现在衬底电压因为施加了VDS不再保持均匀相等。

靠近漏端这一端的电压VGD要比VGS小,因为漏端电压高。随着漏端电压的提升,VGD会率先小于Vth,这样漏端这个地方就形成了夹断(pinch-off);

但这个夹断和VG-Sub<Vth时的截止不一样,称为预夹断,是通过VDS破坏了VG-Sub>Vth的条件形成的夹断,且只有漏端一点夹断了,不是整个沟道都夹断了。

但是,沟道的预夹断正是我们需要的,因为夹断后漏端和栅端就连接起来的了。

这里其实是有点问题的,因为按照前面的器件模型,夹断后VGD是等于Vth的,继续增大VD可以继续减小VGD,造成小于Vth的情况。

但这里的假设是,VGD减小到Vth的时候,栅端和漏端连接起来,这样无论VD如何变化,夹断点都等于Vth,整个沟道的水平电压也就保持不变了。

这里不考虑channel-length modulation的情况。夹断以后,器件模型就类似是diode-connected的电路拓扑了,栅端和漏端连接,器件始终工作在饱和区。

不过不同的是,器件里降低VD可以回到线性区,而在电路里,降低VD回不到线性区,只能直接进入截止区。

根据前面的分析,可以知道NMOS进入饱和区的要求是VGD<

PMOS因为栅端电压负与衬底端,所以施加VSD后,漏端的电压最低,且低的栅端电压高于漏端电压不超过阈值电压了,破坏了栅电压构筑的导通条件,所以有VGD>Vth,换算一下,VDS<VGS-Vth。

总结

对于NMOS,栅端gate比衬底端substrate高一个Vth,才能形成沟道,要破坏这个沟道,栅端gate比漏端drain高,但不能高于Vth,才能形成预夹断,工作在饱和区。

VGS>Vth,VGD<Vth,后一个条件即VDS>

对于PMOS,栅端gate比衬底端substrate低过负阈值电压Vth,才可以吸附空穴,形成反型层,栅端gate比漏端drain低,但不能低过Vth, 形成沟道破坏条件,才能工作在饱和区。

VGS<

〖资料推荐〗

往期精彩好文:

目前已有65475位人关注加入我们

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

KIA-MOS管

广东可易亚半导体科技有限公司

2005-2022,十六年品质保证

您的电源我来“管”

官方网站:www.kiaic.com

全国咨询热线:0755-83888366

咨询客服QQ:2880195519

请勿直接点击观看,先复制链接到浏览器上打开:

想要看什么影视 可以留言告诉我:我能找到你想要的影视