半导体制造行业一直在尝试解决的一个问题,就是如何在单位面积内塞进更多的晶体管。要解决这个问题有很多的思路,比如把晶体管做更小(制造工艺),或者把晶体管的排列、布线等方法改改(scaling booster),也可以把die叠起来(先进封装),或者还可以考虑引进新材料——目标当然也是把晶体管密度提高。

这两年媒体讨论比较火的主题是先进封装工艺,封装是制造之后的事情。原因很简单:要把晶体管做小已经没有过去那么简单了。所以行业探讨的重心有了一定程度的偏移。

不过无论如何,半导体制造热议的“尖端工艺”本质还是在于把晶体管做得更小。所以我们写了那么多文章来谈7nm、5nm、3nm工艺。晶体管在缩小的过程中,除了物理尺寸变小作为工艺进步的常规指标;另一个比较多人关注的话题是晶体管结构的变化——或者说晶体管外形在变。

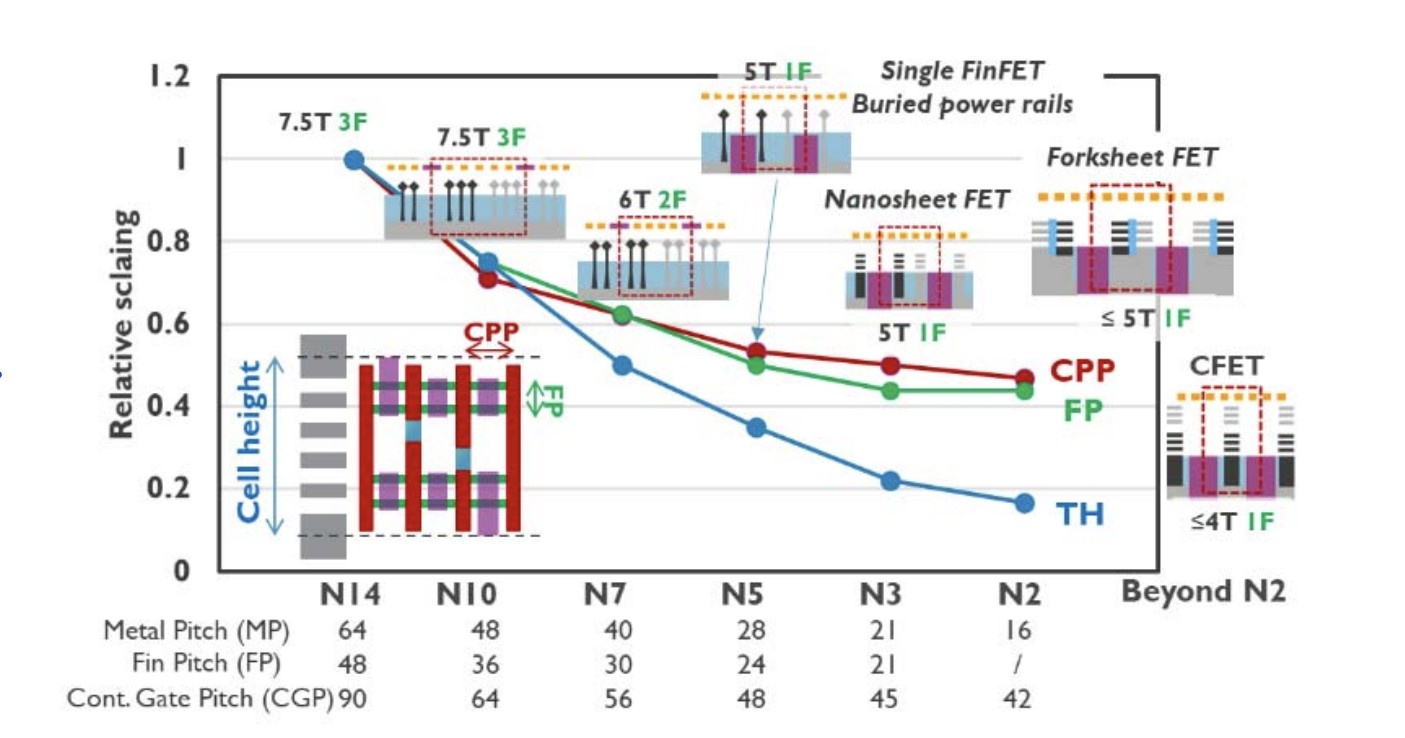

22nm工艺以前的Planar FET晶体管,现在常见的FinFET晶体管,以及很快就要见到的GAAFET晶体管(或nanosheet FET,以下所有表述都将以nanosheet FET来替代GAAFET),就是晶体管在“变形”。从IEEE的国际元件及系统技术蓝图(International Roadmap for Devices and Systems)来看,GAAFET不出意外会有3个节点的寿命,也就是3nm、2nm和1.5nm,延续时间预期是到2028年。

来源:Alessio Spessot, et al. Device Scaling roadmap and its implications for Logic and Analog platform. 2020 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium. DOI: 10.1109/BCICTS48439.2020.9392980

而在此之后会有一种CFET(complementary FET)晶体管在1nm节点问世,替代nanosheet FET。但Imec(Interuniversity Microelectronics Centre)就不是这么看的。Imec认为nanosheet FET晶体管会延续到2027年,随后会由forksheet FET接替;而CFET则将于2029年出现。这篇文章我们就来尝试探讨,近未来的晶体管结构可能往怎样的方向发展。我们主要基于Imec的paper来谈谈未来的晶体管结构演进路径。

需要一点免责声明

半导体制造行业有个有趣的事实,就是几乎所有人、所有企业都对未来过分乐观。导致现在在尖端制造工艺上,几乎没有什么新技术可以真正按期交付的。所以我们得写个(虚伪的)免责声明。万一5年以后,nanosheet FET都还刚刚接近成熟,那我们也并没有责任。

不光是foundry厂针对新工艺发布时间,普遍在对客户和股东放卫星(比如Intel 10nm比预期晚了3年,三星3nm实际延后至少1年);还在于尖端工艺的技术难度正大幅抬升。台积电最近才刚刚说了,预期N2节点风险生产是2024年,2025年末才可能量产;则我们真正见到N2,起码也得是2026年了(且极有可能2nm比我们预想得来得更晚)。而N2将是台积电的首个nanosheet FET结构晶体管,你相信2027年nanosheet FET就会淘汰吗?

实际上早在2018年,那会儿大家都还不确定nanosheet FET是否会成为接替FinFET的晶体管结构。毕竟考虑采用新的晶体管结构时,高迁移率、低漏电、低电压阈值、低供电电压等问题都需要纳入考量。彼时GAAFET、NCFET(negative-capacitance FET)、第三代半导体都正被热议。

即便单是GAAFET,nanowire FET和nanosheet FET谁更靠谱都还在争论。当时的专家普遍预测4nm和3nm工艺大概会在2020年上市,回头看当时的我们实在是太天真了。当年Imec就是GAAFET支持派,不过他们对于这种形态的晶体管预测为仅可应用1-2代节点,到2nm之时3T标准单元高度就会让GAAFET举步维艰。

事实和预期相差得还是有些遥远,毕竟几nm节点皆人为定义。FinFET实则延续到了3nm节点(Intel与台积电),而2nm才刚刚开始应用nanosheet FET又有谁能想到呢。可见不管是2018年,还是现在来做晶体管结构预测,大概都不是特别靠谱。

再聊聊明年就来的GAAFET

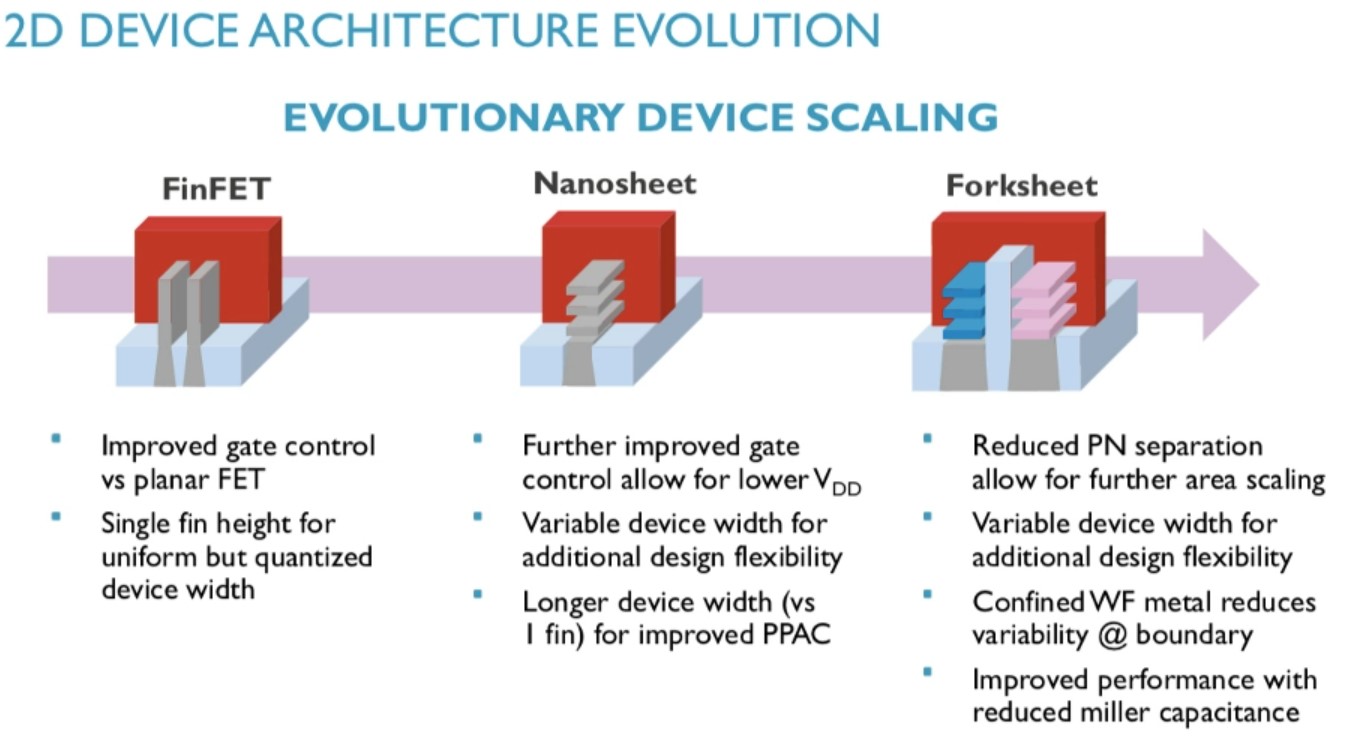

三星即将在3nm工艺节点采用nanosheet FET结构晶体管,我们过去花不少篇幅介绍过。不过基于对晶体管结构进化更进一步的认知,本文再花少许笔墨来谈谈这种把FinFET的fin翻转过来横置的晶体管结构。

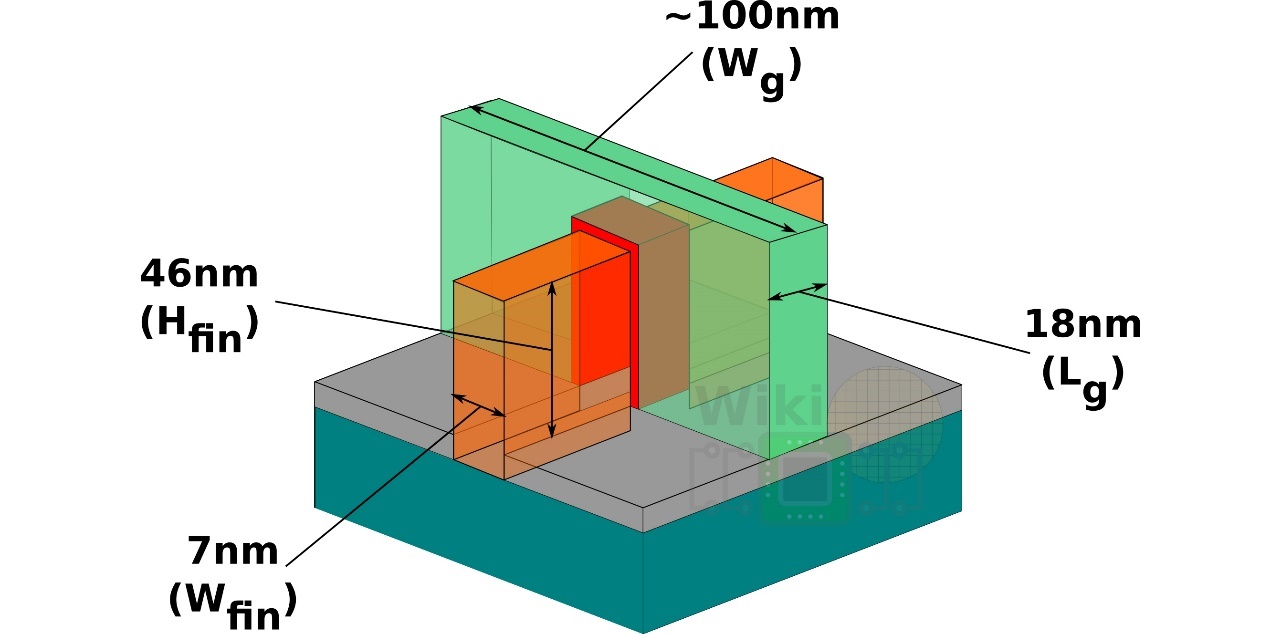

来源:Wikichip Fuse

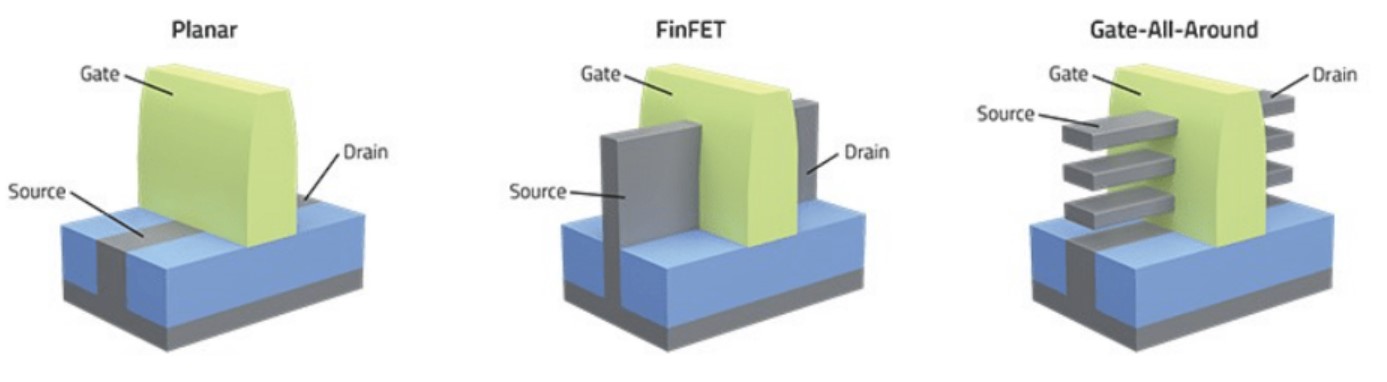

对于早期传统的planar FET晶体管来说,随着工艺发展,gate length(栅极长度,Lg)越来越短,到20nm工艺前后已经有了短沟道效应这种比较显著的问题,也就无法进行有效的静电控制。所以22nm时期FinFET出现了,fin伸了出来(上图橙色部分),有效增大了沟道接触面积。与此同时,只要把fin做得更高,那么更宽的有效宽度就能提升输出电流。

在时代进入3nm节点前后,FinFET结构本身也开始暴露问题。首先是随着gate length的进一步变短,FinFET结构也很难再提供有效的静电控制。

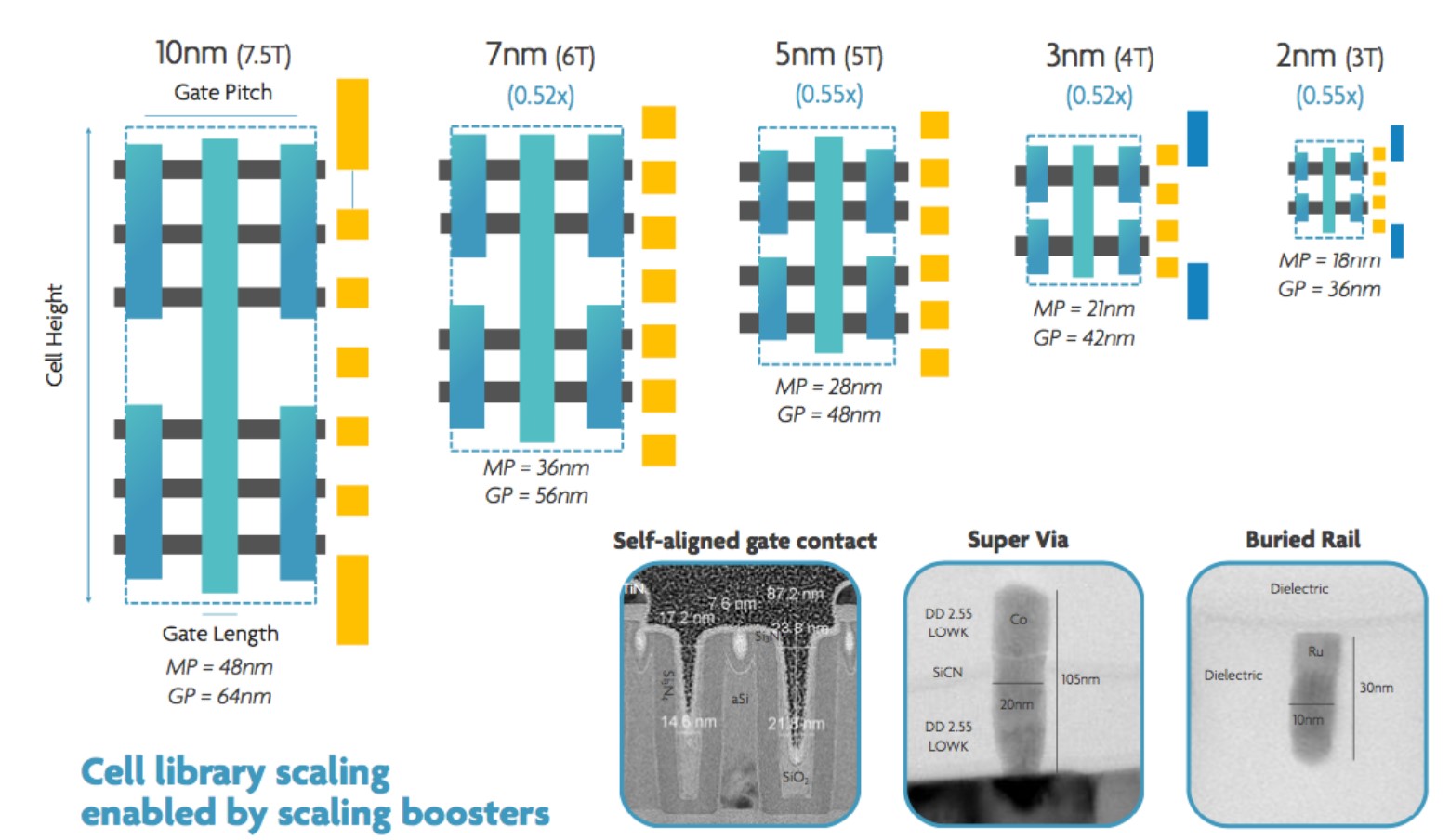

单元的尺寸进化,来源:Imec

第二个问题在于fin的数量——针对这个问题,需要理解一个基本概念:单元(cell)。多个晶体管(及其上的互联结构)构成一个标准单元——可以把单元看做是一个功能模块。而单元的大小实则才真正决定了其面积效益有多高。有个词叫scaling booster,是指不缩小晶体管,而是对单元做调整,也能提升某一个工艺节点的晶体管密度。

Scaling booster方案有一招就是缩减单元高度,以“T”(track)为单位来计高度。目前相对紧凑的6T高度标准单元,每个器件只用到2个fin。未来要往单个fin发展怎么办呢?fin数量的缩减实则也就限制了fin的有效宽度。这就是FinFET遭遇的第二个问题,fin数量再减,问题就变得更大了(所以我们应该期待一下台积电3nm工艺是如何更充分挖掘FinFET潜力的)。

来源:Lam Research

于是nanosheet FET晶体管出现,相当于把原来FinFET的fin给水平横置过来——以前叫fin,掉个方向就叫nanosheet了(如上图)。因为nanosheet被gate四面环抱,接触面更大。单位面积内,有效宽度得到增大,提供更好的沟道控制。对于三星的nanosheet工艺当前的已知信息,建议阅读这篇文章。

谈谈scaling booster

Intel 10nm工艺文章详细介绍过scaling booster。很多foundry厂也经常在IEDM之类的顶会上介绍自家的scaling booster方案。毕竟这是在晶体管本身结构不变、尺寸也基本不变的前提下,能够提升整体晶体管密度的方法,而且可能提升还非常大。比如三星5nm相比于7nm工艺,晶体管本身的物理尺寸基本不变,但scaling booster令其晶体管密度也有了全面提升。

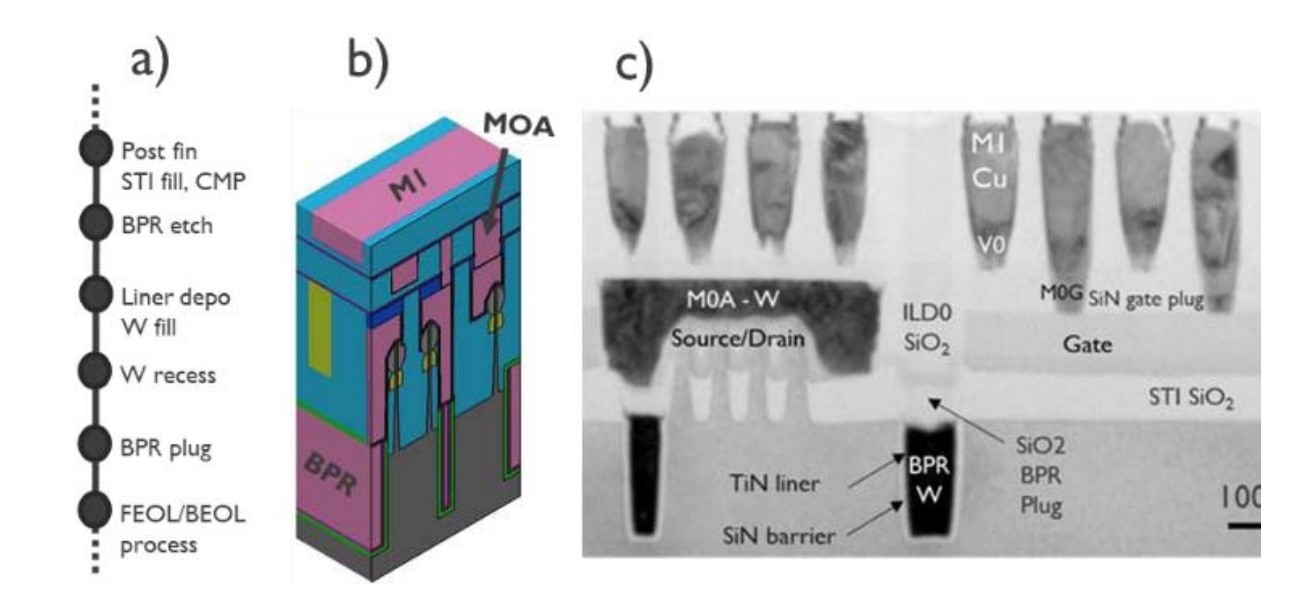

在FinFET转往nanosheet FET之后,6T高度的标准单元能够变为5T——但这种变化实际上也需要scaling booster的参与。Imec在去年题为Device Scaling roadmap and its implications for Logic and Analog platform的paper中提到,缩减单元面积可以采用buried power rails和wrap-around contacts之类的方案。

一般供电的电源轨(power trail)是在芯片的BEOL阶段互联金属线层级才部署的。而buried power rail(BPR)尝试的是把电源轨“埋”进STI(shallow trench isolation)和substrate中。据说能够达成更低的电阻,关键是尺寸更自由。这么做使得电源轨的制造过程,不再位于原本的M0互联层,而是埋于FEOL(front-end-of-line)工序,为后面的互联预留了更多的布线资源。

Imec介绍的另外一种名为wrap-around contact的技术,则是相关于源极漏极的接触方案——和buried power trails是配套的。这种方案能够进一步降低接触电阻,可应用于nanosheet FET(此前FinFET传统应用了一种名为Diamond Epi Contact的方案)。

接下来可能是forksheet FET

Imec这两年似乎一直在坚持,nanosheet之后肯定要出现一个变种的forksheet FET。Imec认为,要基于nanosheet FET实现尺寸缩减,就必须考虑把nFET和pFET隔离做得更加紧凑才行。一般来说n-to-p的分隔最小距离是有限制的,FinFET和nanosheet FET结构都难以突破这种限制。比如FinFET需要大约2个dummy fin的间隔,来将n和p分开。对于标准单元而言,就要占据至多40-50%的空间。

forksheet FET的提出就是为了解决这个问题。本质上forksheet FET仍然算是nanosheet FET。只不过这种新型结构有一堵“墙”会将nFET和pFET隔开。这就是“forksheet”名字的由来。而且这么做的确让n-to-p的间隔变得更为紧凑。

来源:Imec

这堵墙实际上就成为自对准gate以及contact(接触点)的天然屏障,它阻隔了锗化硅等向性蚀刻(isotropic etch)以及gate WFM(work function metal);形成了垂直堆叠的tri-gate(三栅)结构。如图所示。

据说forksheet FET晶体管的制造流程,大部分都和nanosheet FET类似,只不过针对中间那堵墙的成型需要一些额外的步骤。从工艺层面来看,它也能带来一些额外的好处,比如填充WFM(work function metal)金属层的流程得到简化。对性能和功耗带来的好处自然一方面在于节约了部分面积,单元高度可从5T下降到4.3T(单元面积缩减20%);而且相较nanosheet FET,性能有所提升,因为减少了gate-drain的重叠,也就降低了米勒效应的影响;节省的空间如果拿来加宽nanosheet,那么也可以提供更好的性能。

另外Imec还宣传说,forksheet对于SRAM bitcell来说也能带来较大的面积效益。

前两年Imec在宣传forksheet FET有多好的时候提到,这种结构的器件目标是2nm工艺。借助TCAD模拟,达成42nm CPP(Contact Poly Pitch,栅极间距)、5T标准单元、金属间距16nm,外加前文提到的scaling booster(buried power rails与wrap-around contacts)设计,则相较于nanosheet FET,相同功耗下可达成10%性能提升,相同速度下达成24%功耗下降。不过和foundry厂一样,这些数字近两年好像又有了调整...“没准”才是个常态。

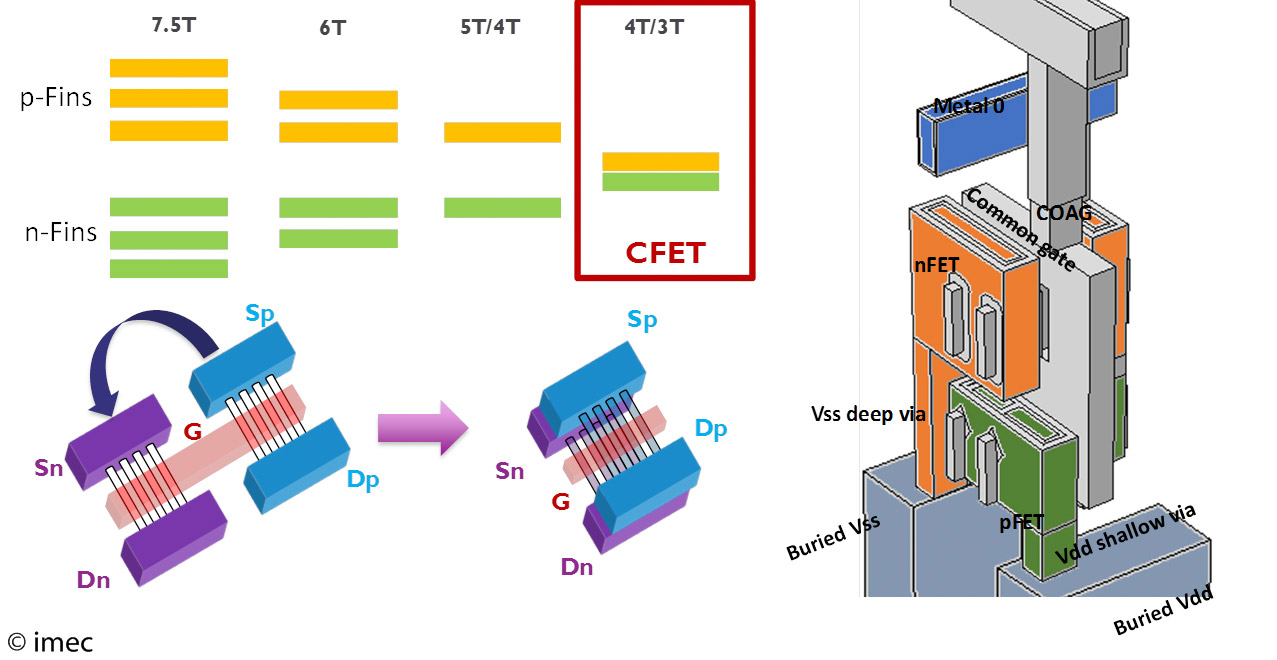

起码5年以后的3D“折叠”晶体管

业界比较瞩目的新结构器件应该是CFET(Complementary-FET),虽然可能我们短期内是不大能看到的。这是一种完全体的3D结构器件。CFET就器件级别的结构来做探讨时,其讨论维度和FinFET、nanosheet FET其实不大一样(即它更像是单元或者block层面的3D结构调整)。

来源:Imec

单元高度在5T以后要缩减很大程度受制于所谓的rountability问题,“可布线性”,或者说走线可施展的余地。CFET的诞生很大程度是对这一问题的优化。CFET是把nFET“折叠”到pFET上面(所谓的sheet-on-sheet),也极大程度消除n-to-p间距。从示意图来看,是将nFET与pFET 3D结构化了,更充分地利用了3D空间。

那么折叠过后多出来的单元空间,要么可以用于提升性能,或者就是单元本身面积减少了。基于这样的堆叠,达成了2层本地互联,对于单元内部的走线而言,其实也提供了更高的自由度。单元间连接走线当然也有帮助。所以总的来说,CFET有更好的设计弹性。

业界对这种结构器件的探讨这两年也非常多样。比如说留给BEOL布线的空间有多大,以及从性能分析来看CFET相较FinFET究竟怎么样。与此同时,CFET同样对SRAM面积缩减很有价值,有paper提到其潜在的面积红利能够达到50%。这是CFET被看好的很重要的一点。

Imec的评估提到,基于FinFET的4T CFET能够超过5T“标准”FinFET晶体管标准单元的性能与功耗表现。如果是基于nanosheet的CFET,还会提供更多的性能红利,包括将单元高度降到3T等。显然类似CFET这样的结构,DTCO在后续的尖端工艺节点上会非常重要。

更遥远的未来

远至2030年以后,有一种2D材料FET在开发中。这种2D FET的与众不同之处在于,沟道是基于TMD(transition-metal-dichalcogenide,二维过渡金属硫化物),比如说二硫化钼或者二硒化钨之类的材料。TMD可以达成更薄的沟道,实现gate length的缩减以及高沟道迁移率。

去年IEDM上,Intel曾介绍过采用nanosheet FET的2D材料FET器件。不过现在谈此类方案可能还为时过早,毕竟仅是材料方面的工程问题就一大堆。

除了这些,还有一些广为人知目前仅在实验室里的碳纳米管FET——由微小的纳米管来构成沟道;还有像是垂直FET(vertical GAAFET)——从方向上是gate环抱住源极和漏极……虽然其中的很大一部分可能永远都只会停留在实验室阶段。毕竟即便是前面这些谈到的近未来的器件结构变迁,都仍旧面临着大量的工程问题待解决。最终能否提枪上马、大规模量产都需要打问号。

不过人类工程研究的厉害之处在于,似乎我们经常在说某项技术发展到头之时,总会有柳暗花明又一村的缓解方案来为电子产业续命一波。就像几nm工艺节点“到头”喊了这么多年,其实也总没有到头。更何况,不是还有先进封装、AI技术、DSA之类的东西在当后备军吗?