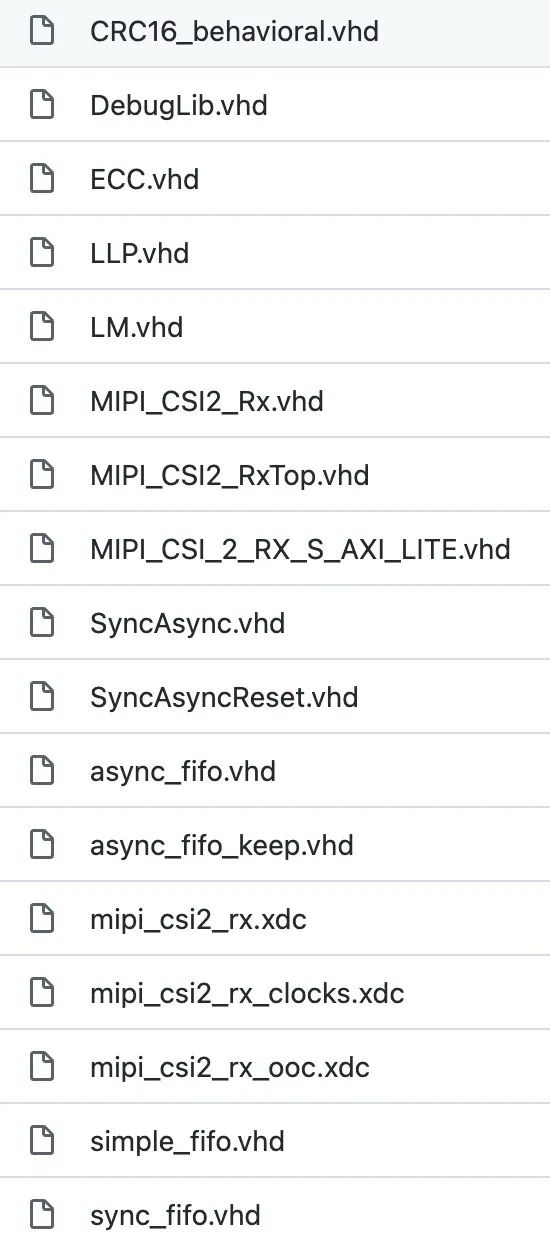

开源项目推荐已经有六期了,已经发了AXI,PCIe,以太网,低速接口等等,大家可以从往期文章阅读。本期主要带来VHDL的开源项目,也是第一次集中发VHDL的IP,包括:AXI-full(VHDL),AXI-lite(VHDL),Datamover(VHDL),MIPI_CSI2(VHDL),HDMI_Display(VHDL),Motor_controller(VHDL)等。

仓库地址:

https://github.com/KutuSystems/XilinxIP

经典开源项目了,并且经过完整的验证,如果大家有注意的话,国内有些开发板的CSI2例程用的就是这个IP,代码完全可见,质量有保证,很值得参考。

从代码注释看是赛灵思官方的代码,具体未知,比较久远的代码,但大厂代码还是值得参考的,注释非常好,比较有风格,下面是部分代码节选。

-- **************************************************************************

-- Read ID assignment

-- **************************************************************************

RID_REG : process(S_AXI_ACLK) is

begin

if (S_AXI_ACLK'event and S_AXI_ACLK = '1') then

if (S_AXI_ARESETN = '0') then

RID_i <= (others => '0');

else

RID_i <= axi_rid;

end if;

end if;

end process RID_REG;

-- ****************************************************************************

-- This process is used for generating the read response on AXI

-- ****************************************************************************

RD_RESP_REG : process(S_AXI_ACLK) is

begin

if (S_AXI_ACLK'event and S_AXI_ACLK = '1') then

if (S_AXI_ARESETN = '0') then

RRESP_1_i <= '0';

else

if (send_rd_data = '1') then

RRESP_1_i <= slv_err_resp or timeout_inprogress_s;

elsif (S_AXI_RREADY = '1') then

RRESP_1_i <= '0';

end if;

end if;

end if;

end process RD_RESP_REG;

代码来自 Digilent Inc,2014年份的IP,感兴趣可以仔细看看,下面是代码部分节选:

----------------------------------------------------------------------------------

-- Serialization PLL

-- This PLL generates the x2 and x10 pixel clock needed for TMDS serialization

----------------------------------------------------------------------------------

Inst_10_1_pll : PLL_BASE generic map(

BANDWIDTH => "OPTIMIZED", -- "high", "low" or "optimized"

CLKFBOUT_MULT => N, -- multiplication factor for all output clocks

COMPENSATION => "INTERNAL", -- "SYSTEM_SYNCHRONOUS", "SOURCE_SYNCHRONOUS", "INTERNAL", "EXTERNAL", "DCM2PLL", "PLL2DCM"

DIVCLK_DIVIDE => 1, -- division factor for all clocks (1 to 52)

CLKFBOUT_PHASE => 0.0, -- phase shift (degrees) of all output clocks

CLK_FEEDBACK => "CLKFBOUT",

CLKIN_PERIOD => CLKIN_PERIOD, -- clock period (ns) of input clock on clkin1

CLKOUT0_DIVIDE => PLLO0, -- division factor for clkout0 (1 to 128)

CLKOUT2_DIVIDE => PLLO2, -- division factor for clkout2 (1 to 128)

CLKOUT3_DIVIDE => PLLO3, -- division factor for clkout3 (1 to 128)

REF_JITTER => 0.025) -- input reference jitter (0.000 to 0.999 ui%)

port map (

CLKFBOUT => intfb, -- general output feedback signal

CLKFBIN => intfb_buf, -- clock feedback input

CLKOUT0 => pllout_xs, -- x10 clock for transmitter

CLKOUT1 => open,

CLKOUT2 => pllout_x1, -- x1 clock for BUFG

CLKOUT3 => pllout_x2, -- x2 clock for BUFG

CLKOUT4 => open, -- one of six general clock output signals

CLKOUT5 => open, -- one of six general clock output signals

LOCKED => PllLckd, -- active high pll lock signal

CLKIN => PCLK_I, -- primary clock input

RST => PllRst); -- asynchronous pll reset

intfb_buf <= intfb;

只介绍部分,大家可以到Github上下载详细的代码,本期主要介绍的是VHDL代码,目前市面上,VHDL代码确实不多,当前HDL语言,VHDL主要是欧洲用的比较多,国内主要还是Verilog,但这些IP同样可以在Verilog项目中进行调用。