前几天,星球的同学来问我时钟约束的问题。我给他丢了一个文档,然后打电话硬是跟他解释了十几分钟。挂了电话后,我才想起自己之前做的一些笔记。翻了一下,还是觉得有值得分享的地方的。于是有了今天的文章。

时钟这玩意就好比人的鲜血,它是给所有时序逻辑提供动起来的“营养的”。关于它的术语实在是太多太多了。今天就列一些我觉得大家需要了解的吧。(对于edge,period,duty和 transition time这些耳熟能详的术语这里就不讲了。没搞懂的请自个反省去)。

latency

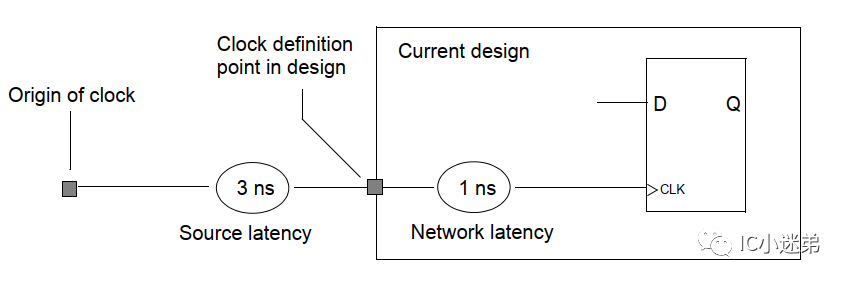

电路跟马路有很多相似之处。其中一处就是,从一个点到另一个点是需要时间的,这个时间就叫做latency,而不同的路段,会有不同的叫法。如下图,当我们在current design的port处定义了一个时钟,那么从时钟源到达时钟定义点的3ns延时叫做source latency;而从时钟定义点到达寄存器clk端的延时叫做network latency。

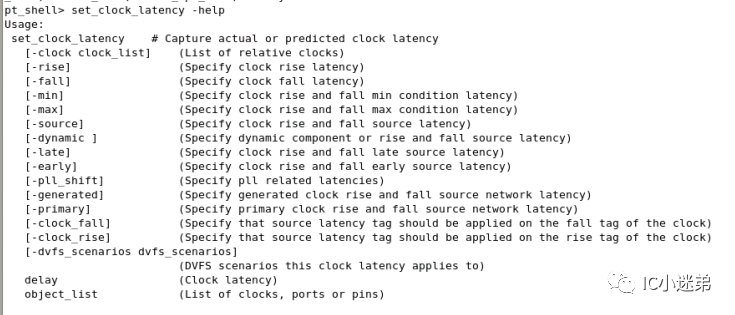

在SDC中,可以使用以下命令对clock latency进行设置。如果需要更加详细的解释,可以在工具中敲"man set_clock_latency",或者查看S司的galaxy doc。这些资料都已经放到martin的知识星球了。

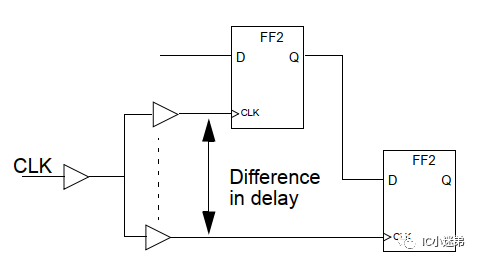

skew

就好比同一个起点到达不同目的地的路是不一样长的,时钟源到达每个寄存器CK端的lantency也是不一样的,如下图。我们管两个寄存器时钟latenccy之间的差叫skew,中文叫偏移。

jitter

即使是同一个源出来的时钟,在不同周期里的波形都可能存在差异。例如,频率差一点,duty差一点等。这个现象就叫jitter,中文叫抖动。jitter的来源主要有三个(摘自三星SOD):

PLL inherent jitter

Jitter magnification for clock divider logic

Clock network jitter due to dynamic supply fluctuation on clock propagation paths

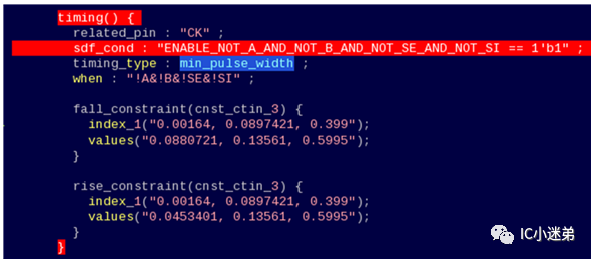

min_pulse_width

所谓min pulse width就是指信号的高电平和低电平的最小脉冲宽度,它是保证信号采样正确的一个重要因素。而由于空穴和电子的导电能力不一致,会导致信号在逻辑单元中的上升和下降时间不一致,进而导致信号脉冲宽度可能会越来越小。当时钟脉冲宽度小于某个特定的值时,寄存器内部可能会就采样出错。所以我们经常会在library或者某些协议上看到一些min pulse width的要求。例如,在standard cell的library里对寄存器的时钟和复位都有一个默认检查值。如下图所示,图中的index_1指的是CK端的input transition的值。STA工具会自动去检查min_pulse_width的。

ideal/propagated clock

一个时钟到底是ideal clock还是propagated clock,这取决于约束。当然约束取决于不同流程。通常,在CTS(时钟树综合,注意,这个不是我们平时所说的综合)之前,时钟路径的走线是还没确定下来,所以时钟需要被设成ideal的。ideal时钟的特点是:

时钟jitter为0,也就是说每个时钟周期的波形都是一模一样的;

时钟到达每个时序单元的时间是一样的,这意味着时序单元之间的clock skew为0;

时钟latency为0(除非通过其它方式指定)

而在CTS之后,时钟树已经长好,就好比马路已经修好,时钟源到达每个时序逻辑的latency已经是真实存在的了。这时我们只需要通过set_progapated_clock命令来告知工具,让工具按照progapated clock的计算方式来。真实latency的存在也就意味着clock skew也是真实存在的了。

uncertainty

所谓uncertainty,其实就是在当前流程中通过过约的方式给设计留足够多的余量,以避免芯片在往后的流程甚至是回片测试中出现时序上的问题。这里所说的流程,包含综合,CTS和P&R(布局布线)。那么,接下来,我会跟大家一一解释以下三个问题:

1. 每个流程的uncertainty覆盖了哪些内容?

2. 每个流程中的uncertainty要给多大?

3. 怎么在SDC设置uncertainty?

首先,我们先回答第一个问题——每个流程的uncertainty覆盖了哪些内容?

1)在时序约束中,并没有什么方法能够准确地约束到clock jitter。所以我们通常都是通过加uncertainty的方式去覆盖掉jitter。

2)从上文中可知,时钟在综合和CTS后的区别在于clock skew是否存在。所以在综合阶段,为了让时序更加接近真实情况,就要使用uncertainty去覆盖掉这个区别。

3)同一条马路不可能做到每一处都是平的,它总会有坑坑洼洼的地方,汽车在经过这些地方时,速度就可能慢下来。对于电路的同一条路径也是一样的,由于工艺本身和外界环境的影响,不同点的延时可能不一样,这就是我们常说的OCV(on chip variations)。还是那句话,CTS后的时钟是真实的,所以我们可以通过相应的约束方法和命令对时钟的OCV进行约束。但是对于数据路径,只有在P&R后才能确定。换句话说,数据路径的OCV要在P&R后才能约束得更接近真实。

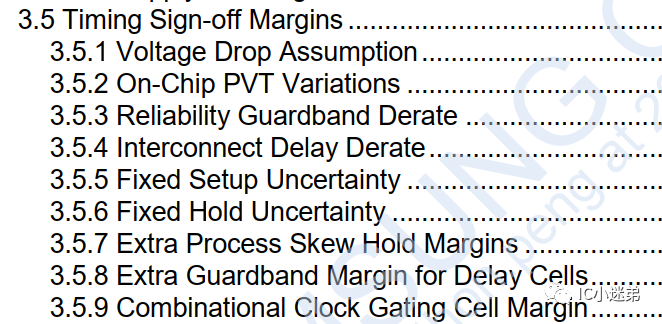

4)芯片的工作状态远不止我们想象的那么简单,它会面临各种各样的问题。例如就好人老了一样,芯片一样会面临老化的问题(这也是导致手机用久了会卡的一个原因)。为了覆盖这些问题,我们就要给自己的电路留有足够的margin,以保证万无一失。以下截图是三星28nm要求留的margin。

说到这里,不知道大家悟了没。但是有一点是比较明确的,随着流程越来越接近tapeout,越来越多的东西得到明确,需要通过uncertainty去覆盖的东西就越来越少。各流程要覆盖的东西分别是:

综合uncertainty = clock jitter + clock skew + margin

CTS uncertainty = clock jitter + margin(不包含时钟的OCV)

P&R uncertainty = clock jitter + margin(不包含时钟和数据的OCV)

接着,我们来回答第二个问题——每个流程中的uncertainty要给多大?

上面的分析可知,uncertainty的值是会随着流程越来越后而变得越来越小。这些值的约束依据主要来源于老师傅的经验和SOD(sign off文档)。

少部分SOD会告诉我们综合的margin要给多大,例如下图(摘自SMIC 40nm SOD)。我的经验是在综合的时候直接给到25%到40%之间。当然,如果是时钟周期很大,就可以直接给个绝对值,而不需要给个大的比例。否则,那样会吓死人的

CTS阶段的uncertainty可以在综合的基础上稍微减小一点。

P&R的uncertainty最小值在SOD上一般都会有严格规定,直接按照SOD上约束就好了。

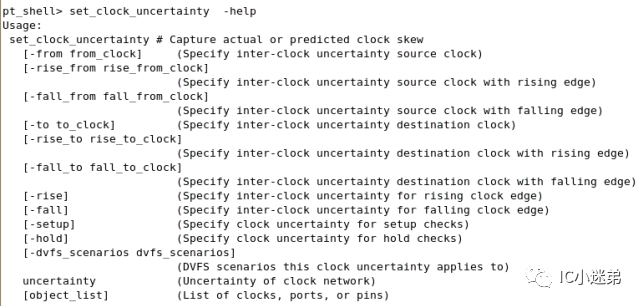

最后就是第三个问题——怎么在SDC设置uncertainty?大家直接去看下面这条命令吧。

clock attribute

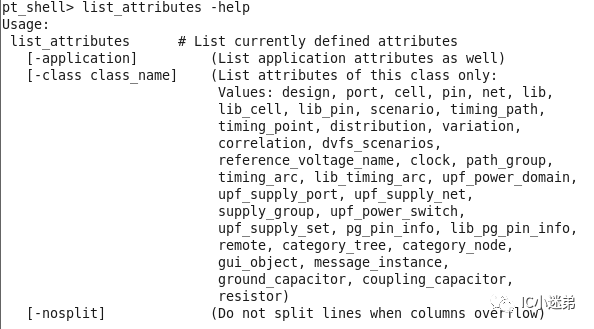

在EDA流程中,有一个叫object的概念,它包含了design,port,cell,pin,net,clock等。这些object都有自己独特的attribute。且对于同一个object,例如clock,在不同的流程中的attribute也有所区别,下图是PT和DC的对比。

那如何知道EDA工具支持的attribute有哪些呢?答案就是下面的"list_attributes"命令。例如,我们只需要在PT中敲入“list_attributes -application -classclock”就可以看到PT支持的所有clock attributes了。

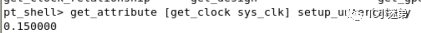

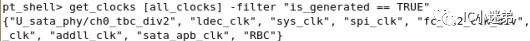

知道这些attributes,我们就可以很轻松的在SDC上做一些约束,下面举两个例子:

1.使用以下命令查看sys_clk的setup uncertainty是多少。

2.使用以下命令获取所有generated_clock。

至于创建时钟,生成时钟,时钟分组这些,后面有机会再跟大家分享吧。