物联网相关话题近年来持续发烧,引爆巨大的市场商机,根据研调机构Gartner的市场研调报告称,全球每秒接入物联网的设备将达63台,并预估2015-2020年物联网市场规模将达千亿美元量级。物联网已经渗透到各行各业与日常生活中,并极大地扩展监控并测量真实世界中发生的事情的能力。物联网将物品和因特网连接起来,含有物联网芯片装置可进行监控与测量进行信息交换和通信,而物联网芯片为了提供与储存更多的数据,在相关芯片设计上,使用到只读存储器(Read-Only Memory,ROM)与静态随机存取内存(Static Random-Access Memory,SRAM)的容量也比过往的大。

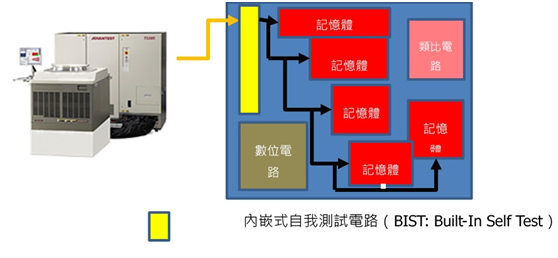

本文引用地址:http://www.eepw.com.cn/article/201801/374300.htm为确保芯片上的内存工作正常,内建自我测试技术 (BIST; Built-In Self -Test) 成为芯片实作中,不可或缺的一部分。因此,厚翼科技(HOY technologies)特别开发「整合性内存自我测试电路产生环境-BRAINS」,以解决传统设计之不足。自我测试电路 (Built-In Self-Test)可以提高测试的错误涵盖率,缩短设计周期,增加产品可靠度,进而加快产品的上市速度。传统的测试做法是针对单一嵌入式内存开发嵌入式测试电路,所以会导致芯片面积过大与测试时间过久的问题,进而增加芯片设计的测试费用与销售成本。此外,传统内存测试方法无法针对一些缺陷类型而弹性选择内存测试的算法,将导致内存测试结果不准确。

1.整合性内存自我测试电路产生环境-BRAINS

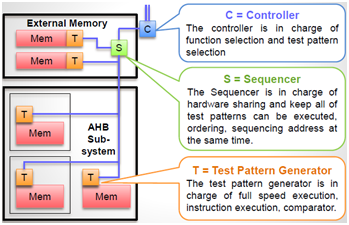

BRAINS是从整体的芯片设计切入,利用硬件架构共享的观念,创造使用者能轻易产生优化的BIST电路工具。

厚翼科技硬件架构共享

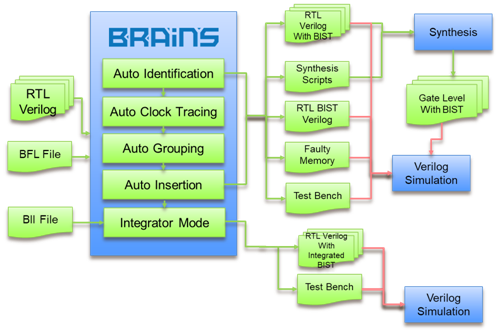

内存测试电路整合性开发环境-BRAINS,基本架构图如下:

BRAINS有下列功能:

n支持RTL和Gate-level格式

n透过BFL (BRAINS Feature List)设定BRAINS的功能

n自动进行内存判别

n自动产生Testbench

n自动嵌入BIST到原设计

n自动追踪 Clock Source

n透过UDM (User DefinedMemory) 档案支持用户自行定义的内存

在机台与BIST测试操作时,BIST的频率操作可以为由机台提供或芯片本身提供:

1.1.BIST的频率操作由机台提供时,BRAINS的相关设定为clock_trace= no与clock_switch_of_memory = yes,BRAINS在生成BIST电路,对于内存Clock接到MCK。

未来在机台与BIST测试时,机台提供Clock到BIST MCK进行BIST测试。

nclock_switch_of_memory :When this option set to “yes”, the clock signal of memory model will be changedto MCK by clock multiplexer in test mode. The clock frequency of MBIST circuitsand memories are running at same frequency in test mode.

1.2.BIST的频率操作由芯片提供BRAINS相关的设定如下:

BIST Function设定:

nclock_trace : Please setthis option to “yes”. It is in charge of disabling/ enabling clock tree tracingfunction.

ninsertion : Please set thisoption to “yes”. It is used to integrate generated MBIST circuits and originalsystem designs.

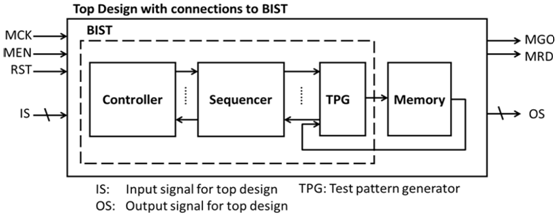

The block diagram forintegrated system design

The block diagram forintegrated system design

nintegrator_mode : Pleaseset this option to “yes”. It is used to add dedicated test port in top modulefor MBIST circuits based on interface option.

Ifthis option is set to “yes”, BRAINS will reserve signals internally for testonly. In this case (set to “yes”), users can use share pin

nauto_group : Please setthis option to “yes”. BRAINS provide auto-grouping function to group memorymodels based on settings in “GROUP” function block automatically.

Clock Fuction设定:

nsdc_file : The path of SDCfile.

ndefine{clock_name} : Setclock domain name

nclock_cycle : Set workingperiod (ns) of clock domain defined in “clock_name”.

nclock_source_list: Set source pin or port of clock domain defined in “clock_name”. please divideeach hierarchy by space. If there are more than one source, please divide eachsource by comma.

因应晶圆厂提供的cell library 不同,BRAINS 提供给使用者能将cell library的行为加入到BRAINS 数据中,能避免BRAINS在clocktracing的过程被中断。

BRAINS 的相关设定将要自定义的cell library的行为加入到BRAINS:

nset user_cell = ./cell_info_name.info

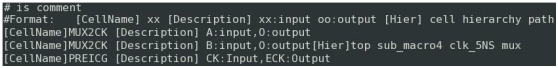

自定义的cell library的格式:

例如,cell library定义其中的MUX2CK(.A( ) , .B( ) , .O( ) , .SEL( )),MUX2CK的行为A 与 B为Inputport ,O为Outpot port,SEL为Select。在cellinfo中定义[CellName] MUX2CK[Description] A:input , O:output,BRAINS clocktracing执行时,当碰到MUX2CK时,Clock的来源会判断为由portA 提供。此外如果在cellinfo中相同的cell name需要有不同的输入源时,[CellName]MUX2CK [Description] B:input , O:output再加上[Hier] hierarchy定义时,BRAINS clock tracing执行时,当碰到hierarchy等于 [Hier]的内容时,当下cell的定义依据定义,选择不同的输入来源。

当产生BIST后,因为每一组BIST 控制电路的Clock 来源尚未和芯片上的Clock接通。要如何与芯片的Clock相接,BRAINS提供Integration 流程,方便用户整合芯片设计与 BIST电路。

1.3.BIST的频率操作由芯片提供与外部提供并存。

2.总结:

内存测试电路「整合性内存自我测试电路产生环境-BRAINS」提供多元化的Clock设计,方便使用者依其需求选择应用,加速开发的时程与提升产品可靠度。