由于能小缩减输出电容器和感应器尺寸从而节省板空间,具有更快转换频率的直流-直流(DC/DC)转换器正变得越来越受欢迎。而另一方面,由于处理器内核电压降至1V以下,任务周期缩短了,在更快频率下很难获得低电压,使得负载点电源的需求不断增加。

很多电源IC供应商都在积极地推销号称能节省空间的更快的DC/DC转换器。一个DC/DC转换器能够以1MH在甚至2MHz的频率转换,这听起来似乎很不错,但是在考虑电源系统的时候,不能光看到尺寸和效率。下面我们来看几个例子,这几个例子都显示了转换频率更高时的优点和缺点。

选择一个应用

我们设计并构建了三种不同电源来展示高速转换频率的利弊。这三种电源的输入电压都是5V,输出电压都是1.8V,输出电流3A。这是DSP、ASIC和FPGA等性能处理器的通用要求。为了限定滤波器设计和性能,允许的波纹电压设在20mV,大约是输出电压的1%;峰至峰感应器电流设为1A。

我们来对比一下这三种频率分别为的350, 700和1600 kHz的电源的利弊。三种方案都使用频率1.6 MHz、低电压、带MOSFET的TPS54317型3 A同步降压DC/DC转换器作为调压器。

TPS54317产自德州仪器,具有可编程频率和外置补偿,专门用于高密度处理器电源负载点应用。

选择感应器和电容器

感应器和电容器都是依照下面的简单公式来选择的:

Equation 1:

V = L x di/dt

Rearranging: L ≥ Vout x (1-D)/(ΔI x Fs)

where: ΔI = 1 A peak-to-peak; D = 1.8 V/5 V=0.36

等式1:

V = L x di/dt

Rearranging: L ≥ Vout x (1-D)/(ΔI x Fs)

此处 ΔI = 1 A峰至峰; D = 1.8 V/5 V=0.36

等式2:

I = C x dv/dt

Rearranging: C ≥ 2 x ΔI/(8 x Fs x ΔV)

此处 ΔV = 20 mV, I = 1 A 峰至峰

等式2中假定使用了一个有可忽略串联电阻的电容器-陶瓷电容器即是如此。由于它的低电阻和小尺寸,三种方案都选用了陶瓷电容器。上面等式2中2的乘数是随DC偏置出现的电容降,因为这一影响没有算在大多数陶瓷电容器的数据表内。

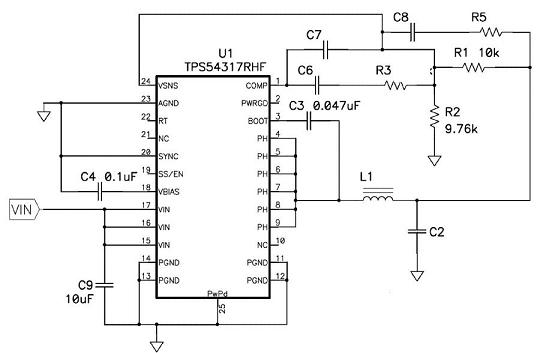

图1的电路用来评估测试台上每个方案的性能

图1:TPS54317参考示意图

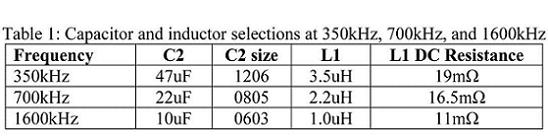

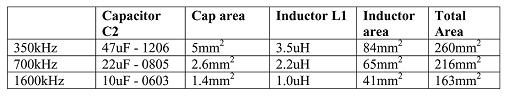

在示意图中没有数值的元件就是在各个方案中被更改的元件。输出滤波器由L1和C2组成。三种方案中所有这些元件的数值都在表格1中列出,并根据上面等式结果来选择。

表格1:频率分别为350kHz, 700kHz,和1600 kHz时的电容器和感应器选项

必须注意,随着频率的增加,每个感应器的DC电阻会减小。这是因为圈数越少所需的铜线长度就越小。误差放大器补偿元件则根据每个转换频率而单独设计。本文暂不讨论如何选择补偿数值。

最小启动时间

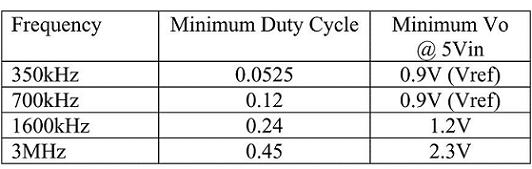

数字转换器-数字转换器集成电路(IC)在最小可控制启动时间上有限值,即脉宽调制(PWM)电路可获得的最窄脉宽。在降压转换器中,场效应晶体管(FET)在一个转换周期内处于开启状态的时间比成为任务周期,等于输出电压和输入电压之比。

上面例子中的TPS54317型转换器任务周期为0.36 (1.8V/5.0V),最小启动时间为数据表中所示的150ns(最大值)。可控制脉宽的限制产生了可获得的最小任务周期,根据等式3可以很容易算出来。一旦知道了最小任务周期,就可以计算出最低可获取输出电压,如等式4和表格2中所示。最低输出电压也受到转换器参考电压限制,TPS54317的最低输出电压为0.9V。

等式3:

最小任务周期=最小启动时间x 转换频率

等式4:

最低输出电压=输入电压x 最小任务周期(受TPS54317参考电压限制)

表格2:最小启动时间为150ns时的最低输出电压

此处可以在1.6MHz转换频率的情况下产生1.8V的输出电压。但是,即便频率是3MH在,最可能低的输出电压也会被限制在2.3V。还有个方法就是降低输入电压或者降低频率。在选择转换频率之前,最好检查一下DC/DC转换器数据表,以确保一个最小可控制启动时间。

脉冲跳跃

如果DC/DC转换器不能以足够快的速度消除栅极脉冲以保持所需的任务周期,就会产生脉冲跳跃。电源会试着调节输出电压,但是波纹电压会随着脉冲的进一步分离而增大。由于脉冲跳跃的原因,输出波纹会显示出分谐波成分,由此可能产生噪音。而由于IC可能不会对一个大的电流尖峰作出反应,也有可能电流限制电路不能继续正常工作。有时由于控制器没有正常工作,控制回路可能也会不稳定。最小可控制启动时间是一个很重要的因素,因此最好要核对DC/DC转换器数据表中的规格,以确认获得最好的频率和最小启动时间组合。[!--empirenews.page--]

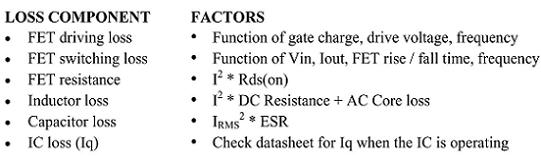

效率和功率消耗

在设计电源时,DC/DC 转换器的效率是需要考虑的最重要因素之一。如果效率太差,就会导致高功率消耗,需要在电路板上借助散热器或者PCB上更多的铜线才能处理好。功率消耗也会需要更多的电源上行。功率消耗有下面几个成分:

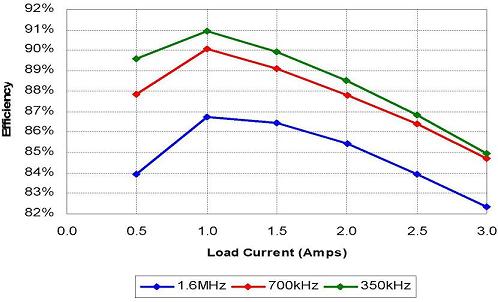

这里的三个方案的损耗来自FET驱动损耗、FET转换损耗和感应器损耗。FET电阻和IC损耗是一样的,因为三个方案使用同样的IC。由于每个方案都使用了陶瓷电容器,电容器损耗可以忽略不计,因为它们的等效串行电阻很低。为了显示高频率转换的效果,图2对每个方案的效率进行了测量和阐述。

图2:输入电压5V输出电压1.8V时不同频率的不同效率

上图清晰地显示出效率随着转换频率的增加而降低。为了能在任何频率情况下都改进效率,需要一个具有低Rds (on)、闸电压或全负载时静止电流规格的DC/DC转换器,或者等效电阻更低的电容器和感应器。

大小

表格3显示了感应器和电容器的数值,以及PCB所需板面面积

表格3:元件大小和总面积要求

电容器或感应器的推荐板面面积是比单个元件稍大一些,以上三个方案都要将板面面积大小计算在内。然后,总面积的大小就是将各个元件所占面积相加,包括IC和滤波器的板面面积,以及所有其它小的电阻器和电容器乘以2,以作为元件间隔。从350 kHz 到1600 kHz能节省的面积很大,滤波器大小可以减少50%,板空间减少35%,节省了将近100 mm2。

但由于电容值和电感值不能降为零,必定会符合回报消减规律。换句话说,提高频率不能无限制地降低总体面积,因为适当尺寸的批量生产的感应器和电容器是有限定范围的。

瞬间反应

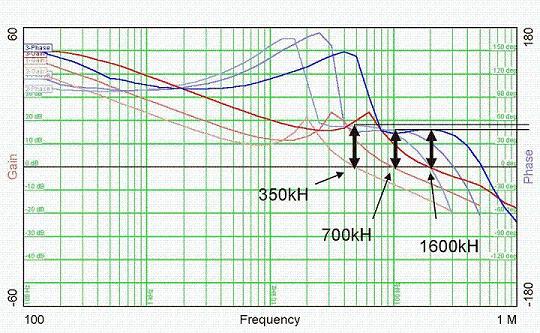

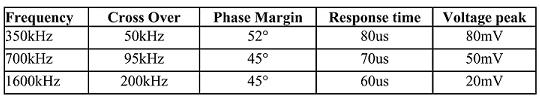

瞬间反应是衡量电源性能等级的一个很好的指标。我们利用每个电源的在更高转换频率下的波德图来进行对比。如图3所示,每个电源的相位补角都在45度到55度之间,这是一个抑制效果不错的瞬间反应。

图3:批量为350 kHz, 700 kHz和1600 kHz.时的波德图

交越频率大约是转换频率的1/8。当使用一个快速转换的DC/DC转换器时,要确保电源IC误差放大器有足够的带宽来支持一个高交越频率。TPS54317的误差放大器单位增益带宽一般是5MHz。表格4显示了实际瞬间反应次数和相关电压峰值过冲值。

表格4:瞬间反应

转换频率越高就带宽越大,过冲值就越低。低瞬间电压过冲对于一些新的性能处理器是必须的,因为它们的调节精度要求可能包括瞬时电压峰值是3%。

当需要更高的输出电流时,德州仪器的TPS40140型可堆叠、双通道并使用外部MOSFET的1 MHz DC/DC控制器可以满足要求。快速转换频率的优势可以通过交叉多个功率阶段并将之从相位中转换出去来实现。

例如,可以将四个频率分别为500kHz的输出堆在一起,就行成了2MHz的有效频率。这样作的好处是可以减少波纹,降低输入块电容,加快瞬间反应,并通过在电路板上扩散功率消耗来改进热量管理。最多可以将8个TPS40140通过数字总线连在一起并实现相位同步,最大有效频率高达16MHz。

总结

设计转换器时要进行利弊权衡。更小的面积、更快的瞬间反应和更小的电压过冲和下冲是本文谈到的“利”,而功率的降低和散热的增加则是“弊”。

如果突破了极限,可能会产生一些问题,比如脉冲跳跃和噪音。在为高频率应用选择DC/DC转换器时,要核查制造商的数据表,以确认一些重要的规格,例如最小启动时间、误差放大器的增益带宽、FET电阻和转换损耗等。在这些规格上有良好性能的集成电路可能成本会更高,但却物有所值,而且在遇到设计难题时更容易使用。