1000pF的芯片电容尺寸是多少?

Q:请问下有知道1000pF的芯片电容尺寸是多少?

A:1000*1000=1000000 um^2 ,GaAs工艺。

A:很多尺寸都可以做,如果是瓷介质的,50V常见尺寸可以做25milx25mil,35milx35mil以及更大尺寸的。

Q:谢谢。

如何理解EMX寄生参数提取与ADS仿真结果之间的差异?

Q:请教大家一个问题,我用EMX提取版图的参数和用ads出来的结果相差有点大,到底信哪一个?看结果应该是ADS提的寄生电容大一点。

A:我对比过几个工艺的ADS不太准EMX要比他准一点

A:EMX。

Q:OK 谢谢两位的解答,EMX设置有什么需要注意的吗?

A:EMX 在算法上是ADS momentum 的简化版。理论上 ADS 更准确。

A:不是这么说的。ADS的 substract是不支持厚金属穿透介质(软件采用合并介质层的处理方式)以及WEE和erosion table建立,ads不支持金属电导率关于线宽及间距的依赖了,而且我这边实测还对比过xr013,ADS准确比emx是稍差。

Q:EMX算出来的Q值好高,这个准确吗?

A:你的情况准不准没人能保证,我只能说根据自己实测的数据,校验。也有可能出现ADS比较准。但是软件之间差距太多就应该考虑是不是仿真设置出问题了。

Q:我觉得可能沉底给的有点问题?没有实测过不知道准不准。

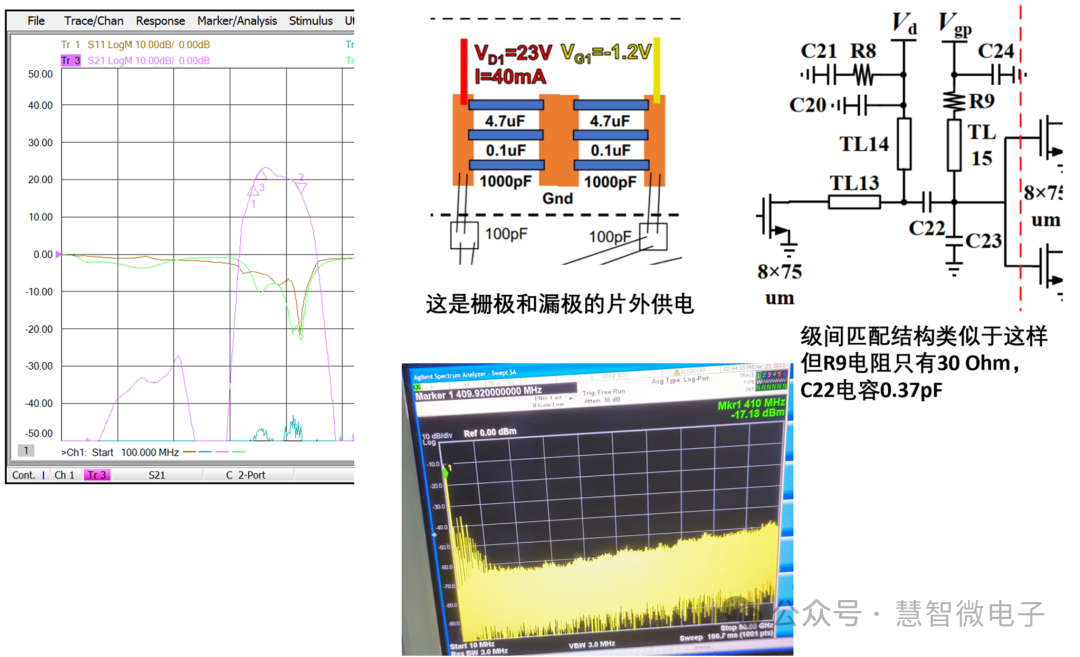

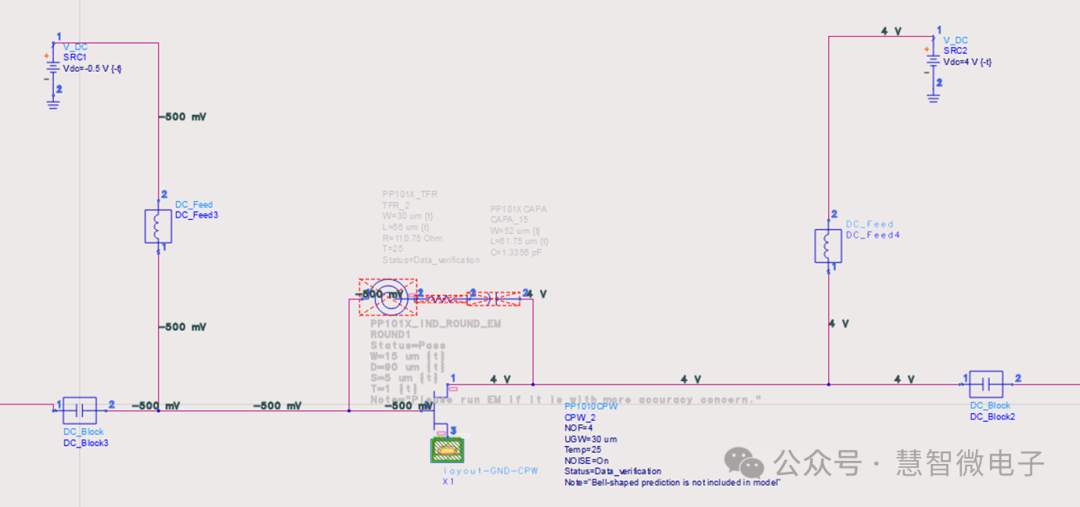

PA低频自激的解决

Q:早上好,想问下群里技术大佬,我自己设计的三级氮化镓PA,在前两级正常开启下,推第三级PA 8x75um 大管子的栅极,但在还没开启时,在-2V 末级漏极就出现了快速电流跳变,从几mA 提到100mA。

后来连接频谱仪,发现极低频有高功率输出信号,怀疑是电频耦合自激。所以想问下有啥好的方法补救没,改芯片外围供电吗,比如加电阻?

A:稳定性网络加了吗?

Q:图里是我的测试结果和外围电路,小信号增益有 ,但不高 ,供电金丝键合到片外电容,再键合到PCB上,接大电容。

您说的稳定性网络是RC吗?我在第二级的前面加了,仿真K 和mu都没问题。

A:栅极去耦电容用47uF试一下。

Q:大电容我再试试。

A:第三级没加吗,外部的电容加大点试试吧。

Q:没加,因为第二级和第三级是级间匹配的,很短。我在想栅极再加个大电阻呢。

A:稳妥一点的话应该每一级都加RC。

Q:哈哈想PAE高点,贪了。

A:PAE不高可以写DE,

A:Gate的rf block 坐在片内的吗?

Q:栅极是四分之一波长线加电容,还有个小电阻,应该算是吧。

A:这时候在gate加电阻效果就没那么明显了,还有就是Gate 和Drain的uf 电容位置大小。另外检查下探针在自激频点有没有异常谐振。还是不行,就搞下输出匹配,把自激频点的阻抗往圆图内拉,看会不会有变化。如果这些自激都没有变化那大概率不是控阻抗降增益的问题,那就要在检查下Layout。另外,带内频率是多少?

Q:26GHz,我发的图里带宽是23到28GHz 。

A:先检查下探针吧,频率那么宽,探针校准不一定也能把低频cover的那么好。

Q:探针应该也没问题,有的芯片测试正常。

A:你自激信号不是在400mhz附近吗?

Q:是的,工作频段就是那个n258,自激信号是在400mHz。

A:我觉得吧,前两级功率够大,是能够把第三级在夹断的情况下推开的,比如C类放大的情况,还有就是末级-2相当于给前两级输出做了个阻抗拉偏,自激也正常吧?本身就不是正常工作条件,不正常才是正常的吧,我觉得没必要琢磨这个问题。

Q:Ads里有扫描输入阻抗对线性的影响套件吗,不是小信号的。

A:imd3 source pull,two tone里面应该有。

Q:

滤波器中的Ant脚的作用

Q:家人们,滤波器里面的Ant 是干啥用的?

A:天线?

Q:是啊,是干啥用的?

A:公共端,接TXM开关的,只是一个标识吧。

Q:什么操作?

A:你是说双工器吧,有Ant端,TX端,RX端

Q:滤波器呢?我只看到有个TX RX Ant,不知道是滤波器还是双工器

A:双工就是滤波器的一种啊。

Q:那其他滤波器也会有Ant吗?

A:有只有输入输出的滤波器。

A:只能代表某一端要接天线吧。

A:TDD的话就只有TX或者RX,就是两端,FDD用双工。

A:Duplexer 双工器;Diplexer 合路器。本质都是两个滤波器,共用一个公共端,标ANT;用过的有SAW BAW FBAR的双工器,合路器还有LTCC的。看需求陡不陡,LTCC最不陡。

Q:谢谢各位大神。

有关LNA尺寸和直流偏置的选择

Q:请问各位大佬,做LNA的时候如何通过扫参来确定管子尺寸和直流偏置,在ADS中要如何操作呢,也是用Gmid吗

A:Gmid主要在运放设计里?LNA看nfmin Gain和IP 1dB折衷吧。

A:LNA是小信号设计,和PA不同,他是从前往后设计,第一级一般重点看噪声系数,依据规格书,看噪声系数满足设计要求的管子做直流仿真,原定偏置点后,再仿真稳定性和最小噪声系数和最大资用增益,看噪声系数是否满足要求,来回迭代栅宽和静态偏置点,后级看着稳定性和增益定静态偏置点。不过建议先选定芯片架构后做这部分工作。

Q:非常感谢。

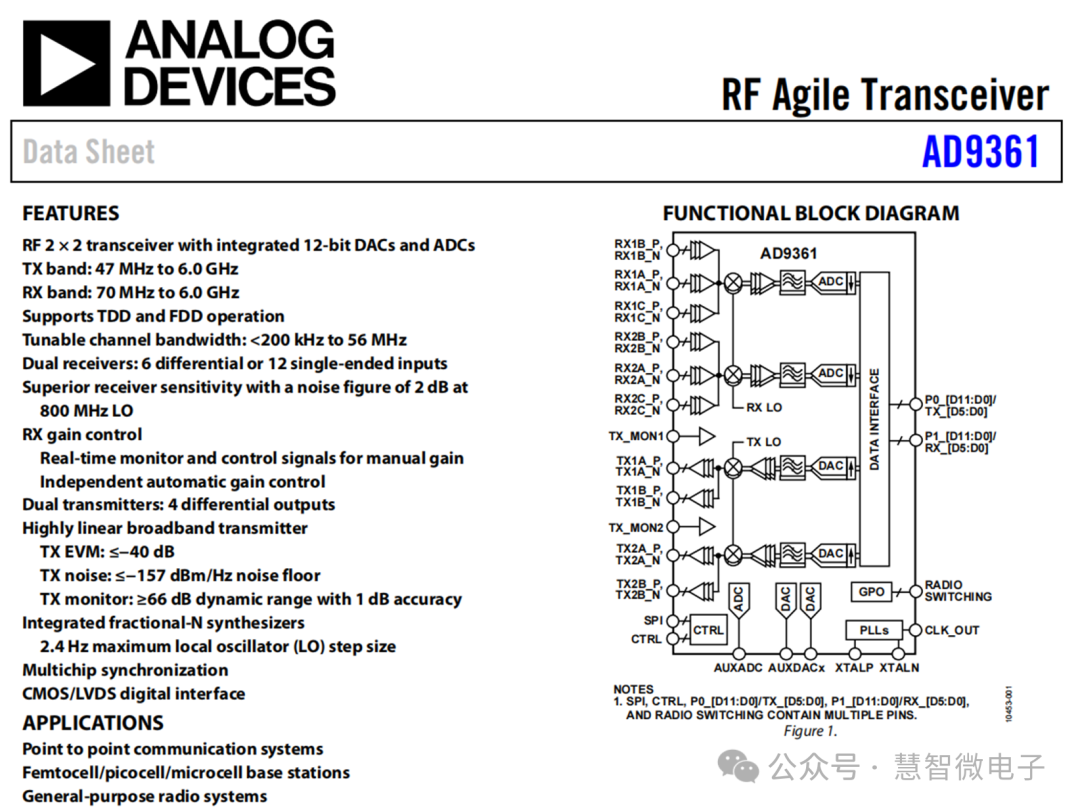

PA前的滤波器有必要吗?

Q:PA前的滤波器有必要吗?

A:芯片还是板级,如果板级出现多发串扰的场景有必要,避免输出PA出现交调,影响输出端的p-1,如果单发就没必要。另外看前端混频器的本振隔离,如果隔离度不够也需要加滤波器。

Q:PA前是ad9361。

A:增益够吗,9361直接推PA。

Q:够的,之前的历史电路中都是PA前加了个滤波器但是PA后没加感觉这里加的位置有些奇怪所以问问看。

A:正常来看滤波器一般放在PA后面,保证带外发射满足要求。

Q:是的我也是这么理解的。

A:放Transceiver后面一般是lpf吧,防止混频的高频产物被发射吧?

Q:但是放的是BPF。

A:低频一起抑制,可能DAC直接出,低频也有问题?TRX接触不多。

A:有可能9361里面的混频器对于中频抑制度不够,需要防止中频过混频器后和射频信号发生交调,影响输出。

Q:好的那还是按原来的情况预留着感谢分享。

有关SAW滤波器结论的讨论

Q:有没有大拿给我讲一下SAW的结构啊?叉指是啥子材料?

A:目前只知道,他是脱离耦合理论的另一种滤波器设计方法,只要知道过度带窄,Q值高,选择性好微波工程里面没有,想了解看看硕士论文前三章就可以了。

A:电磁波转成了声波在压电材料里传播,然后在变成电磁波,叉指就是用来激励和接受,材料就是金属。

A:叉指换能,指的就是电磁换成声波再转成电磁,插指还是叉指,忘了;就是两把梳子。

Q:主要不知道是铝还是铜,一个叉指是一个谐振器,还是很多个叉指是一个谐振器。

一个叉指是一个谐振器,还是很多个叉指是一个谐振器,迷茫我太迷茫了😕

A:我仅了解皮毛,因为不做滤波器,只用。

【讨论未完结,欢迎加入慧智微问答群,参与更多讨论】

阻抗靠近Smith圆图边缘,如何做宽带匹配?

Q:想问一下大佬大功率的放大管的输出阻抗靠近Smith圆图边缘有什么办法可以做宽带匹配呢?

A:你这个边缘是指哪里?

Q:小阻抗。

A:不会是开路点和短路点那个边缘吧?

Q:靠近右边,短路点附近。

A:有没有图

Q:等下

A:短路点在左边

Q:哦对对对,左边

A:把管子阻抗当RC,R是Loadline算出来的,C是管子的Cds和封装引入的寄生电容,当然你要是知道封装的寄生电容电感就更好了。

Q:芯片上的呢?

A:我不是很懂器件,输出阻抗在短路点附近的PA能用吗?

A:芯片直接就RC就好了。Ropt和CDS

Q:它只是输出阻抗小匹配到50欧姆比较困难,我的问题是这种情况下如何实现宽带匹配,可以用的啊。

A:用网络综合工具或者说自动优化试试,或者你用一些宽带匹配结构。

Q:em...好吧。

A:切比雪夫低通或者BPF也有人做,跨谐波吗?

Q:不跨,BPF是啥?

A:“我的问题是这种情况下如何实现宽带匹配”方案一多级LC,不足点会增加面积,最大线性输出功率会低一点,一般等Q值匹配,方案二加负反馈结构,第三种输出用变压器巴伦结构,可以做宽带匹配,其余的翻翻硕士毕设论文吧

Q:哦哦好的我去看看,谢谢老哥。

A:不同芯片架构做的带宽和需求也不同,看具体需求再定架构,毕业后没怎么看论文了。

Q:嗯嗯。

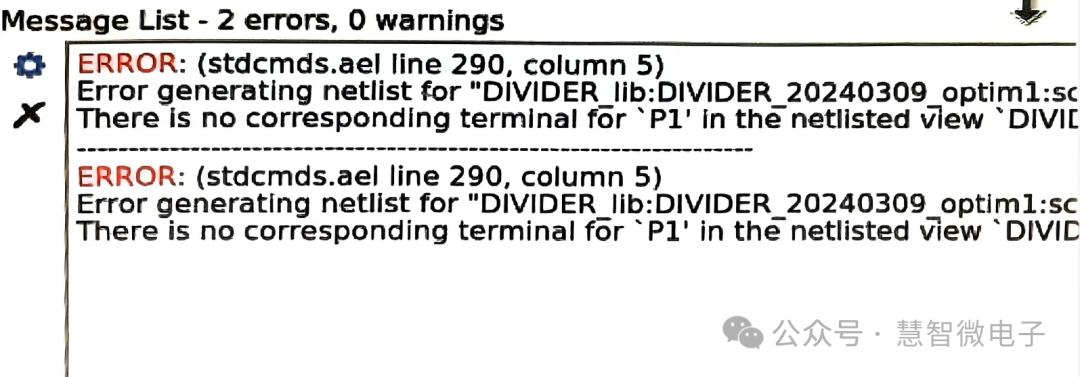

ADS仿真报错的debug

Q:兄弟们,这是啥毛病啊,我加了port点P1了。

A:仿真Em model 点上。

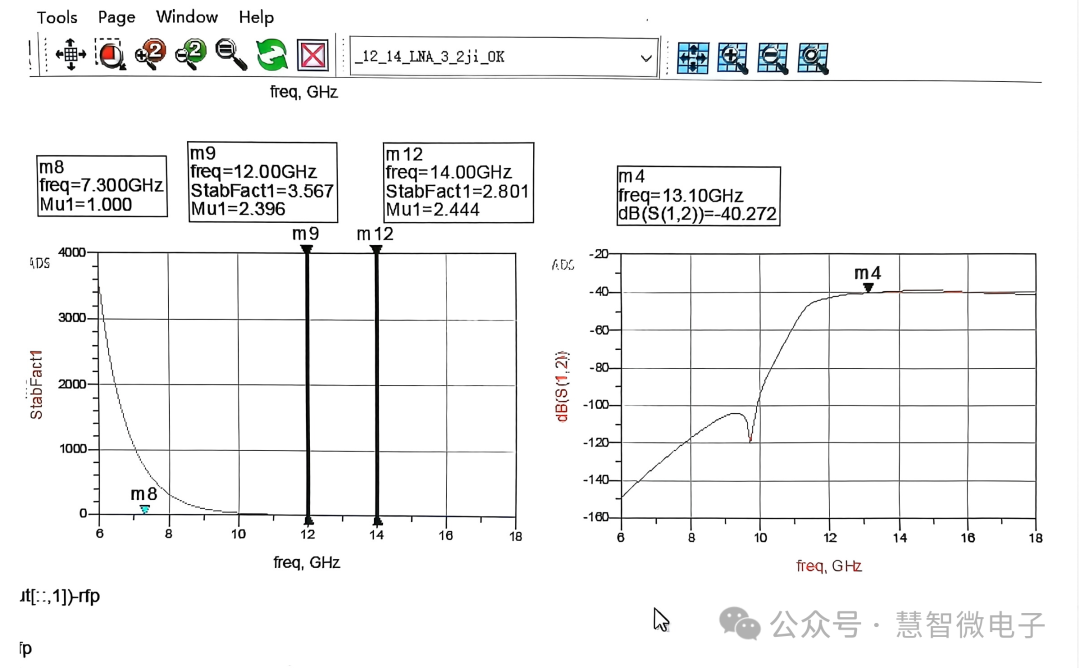

稳定性仿真mu值刚好是1,有问题吗?

Q:兄弟们,这个看mu值的话工作频带外刚好是1,这种对稳定性有影响吗?

A:看stabfact会好一点

Q:好的,谢谢。

A:两种稳定性系数都只能说明小信号稳定性风险,即使小于1也不一定自激在这个频率。时域仿真,输出无杂波一般就不会小信号自激。

Q:好的好的。

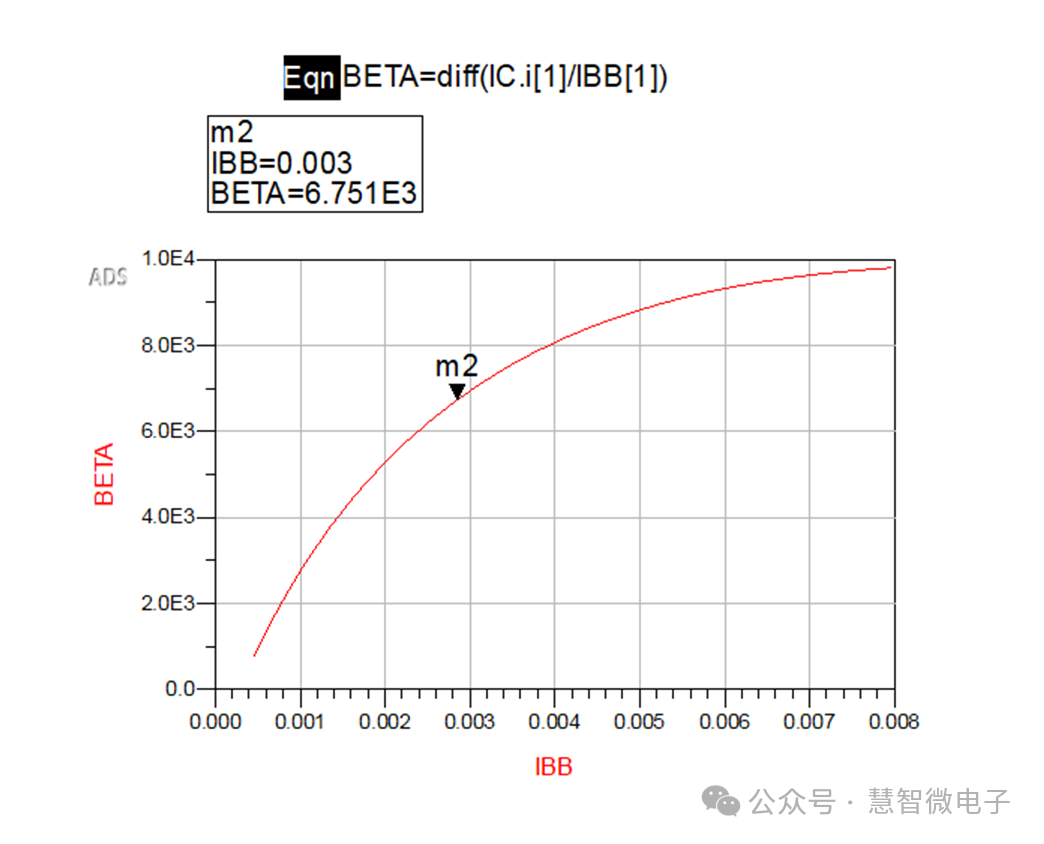

ADS如何仿真跨导?

Q:请问ADS如何仿真跨导呢?

A:仿个直流ids对vgs曲线,然后求偏导?

A:

看看上图公式,直流仿真后,用上面公式就好了。

Q:diff是求偏导的意思嘛?

A:按照规则写就行,就是beta了

Q:gm呢?diff(ids/vgs)这样嘛?

A:跨导应该是的,我这个是BJT你那里是FET

Q:哦哦好嘞,我试一下。

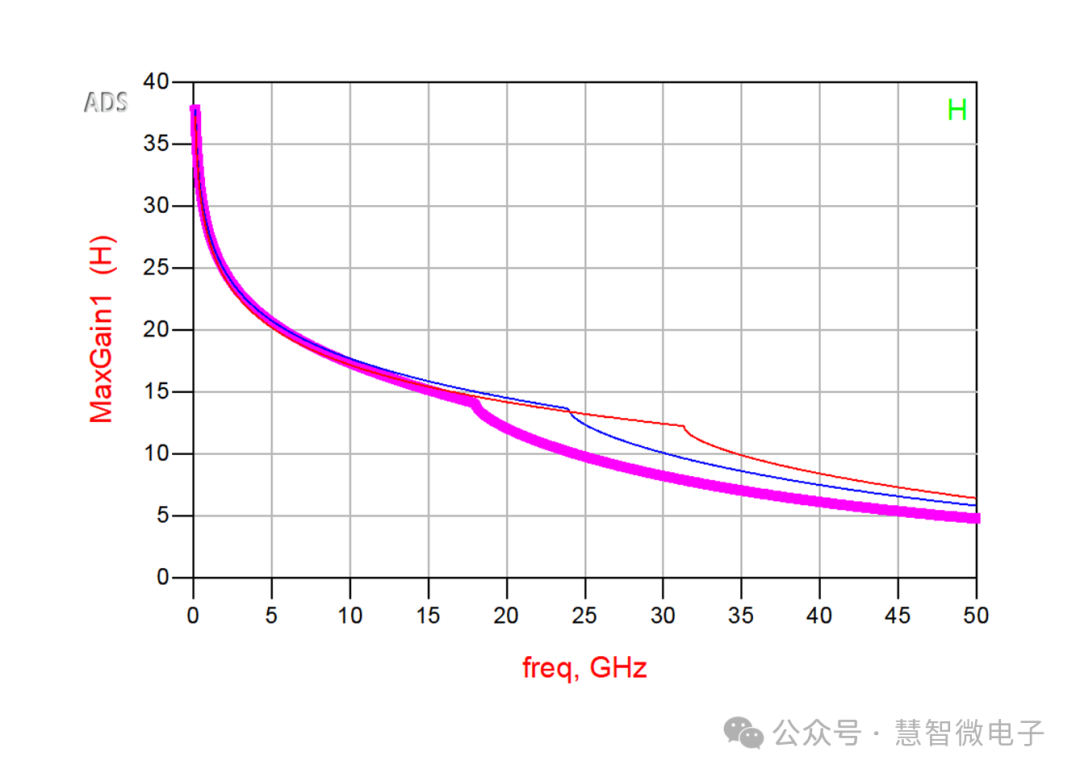

为什么GaAs的晶体管尺寸越大,增益越小;晶体管尺寸越大Cgd,Cgs越大?

Q:为什么晶体管尺寸越大,增益越小?请问我也遇到了这个问题,是什么原因呢?有没有同行也遇到过。GaAs的晶体管尺寸越大,增益越小。

A:晶体管尺寸越大Cgd,Cgs越大。

Q:是泄露掉了嘛?

A:请问GaN晶体管符合这个规矩吗?

A:符合啊。

A:仿maxgain应该所有管子都一样吧。你仿电压增益,管子越大越大增益越大。晶体管尺寸越大Cgd,Cgs越大。这个应该只影响高频特性。

A:“GaAs的晶体管尺寸越大,增益越小 ” 看你怎么仿真了。

Q:红色蓝色粉色分别是4*304*50和8*50的效果

A:你用在哪?SUB6

Q:毫米波,到35G。

A:原理图发出来看一下。

Q:原理图只有管子

A:你尺寸变大,偏置变了吗。

Q:没变。

A:你的接地孔变了吗?

Q:没变,

A:所以偏小就很正常。

Q:请问偏置和接地孔需要变嘛?

A:你可以不直接变管子。把一个管子变成俩个管子,你按这么仿真,增益也是变小的。

Q:“你可以不直接变管子。把一个管子变成俩个管子”请问是什么意思呢?

A:修改管子个数。

Q:这个不能修改吧?

A:理论上,想同配置下,相同尺寸管子叠加,增益不改变。这句你能明白吗?你增益减小,要明白为啥呀。电流密度要保持一样。

Q:Cds电容并联增大?导致泄露更多?

A:接地电感是反馈,你尺寸变大,也要变大,这俩个才是主要原因。

Q:哦哦,原来是这样啊,我试试看看。

A:要不然我直接把管子倍数增大,Cds也增大,增益不变呢。

“ 接地电感是反馈,你尺寸变大,也要变大,这俩个才是主要原因。”要变小,说糊涂了。

A:我的理解是,管子大小变了,管子结构改变,内部的损耗环路也会发生改变。比如MOS中一部分漏极信号会通过每个Finger的cdb进入Bulk,在Bulk的分布电阻中损耗一部分才到Bulk金属电极,管子的Finger和W改变都会影响信号一路走过去穿过的电阻阻值,进而影响了损耗。而通过改管子并联数,来等效放大管子,就没有影响管子结构,Gmax在前仿真阶段就不变了。

A:是的,但先得保证,你的电流密度,和电感要相应变化。

Q:感谢大家解惑

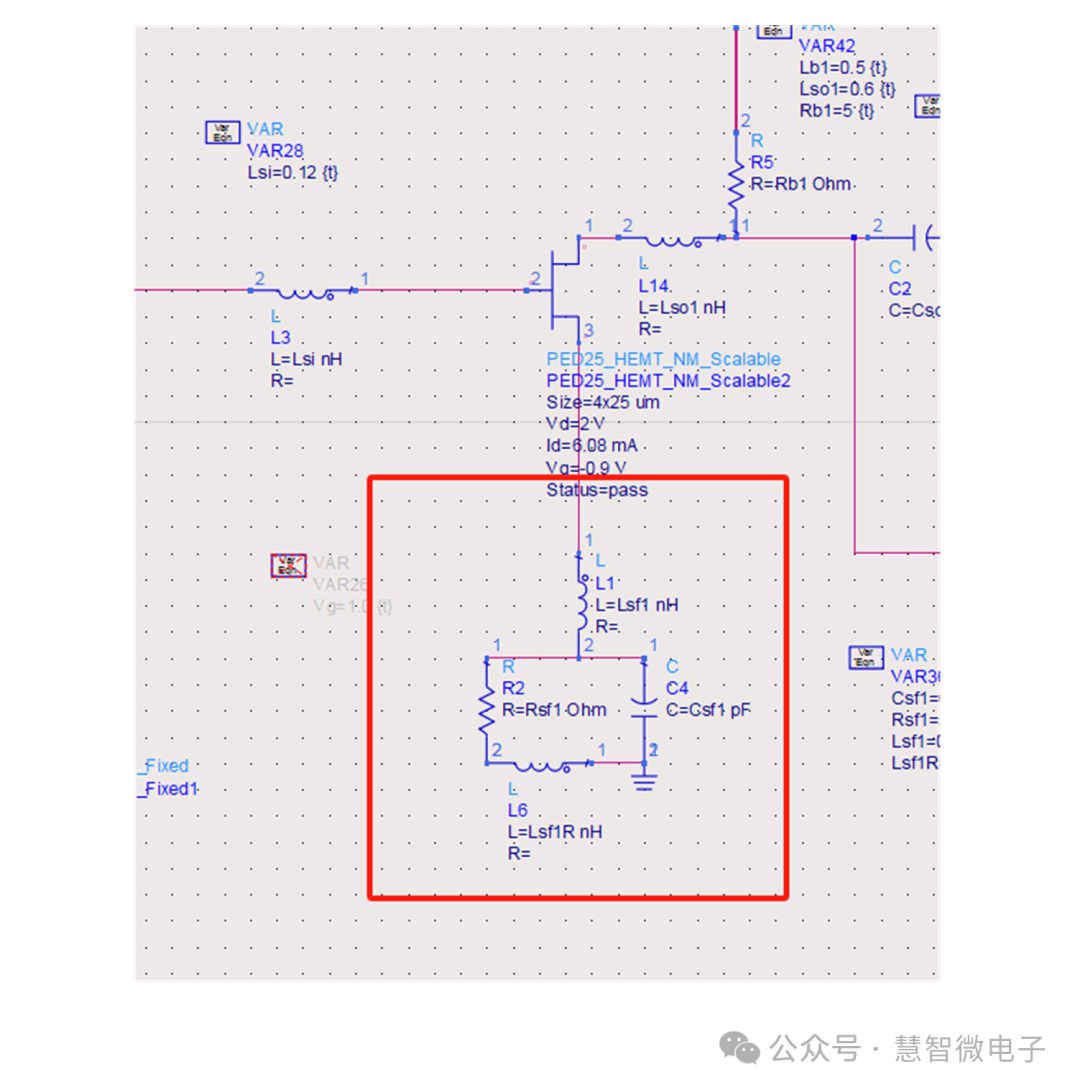

源极RLC网络的作用是什么?

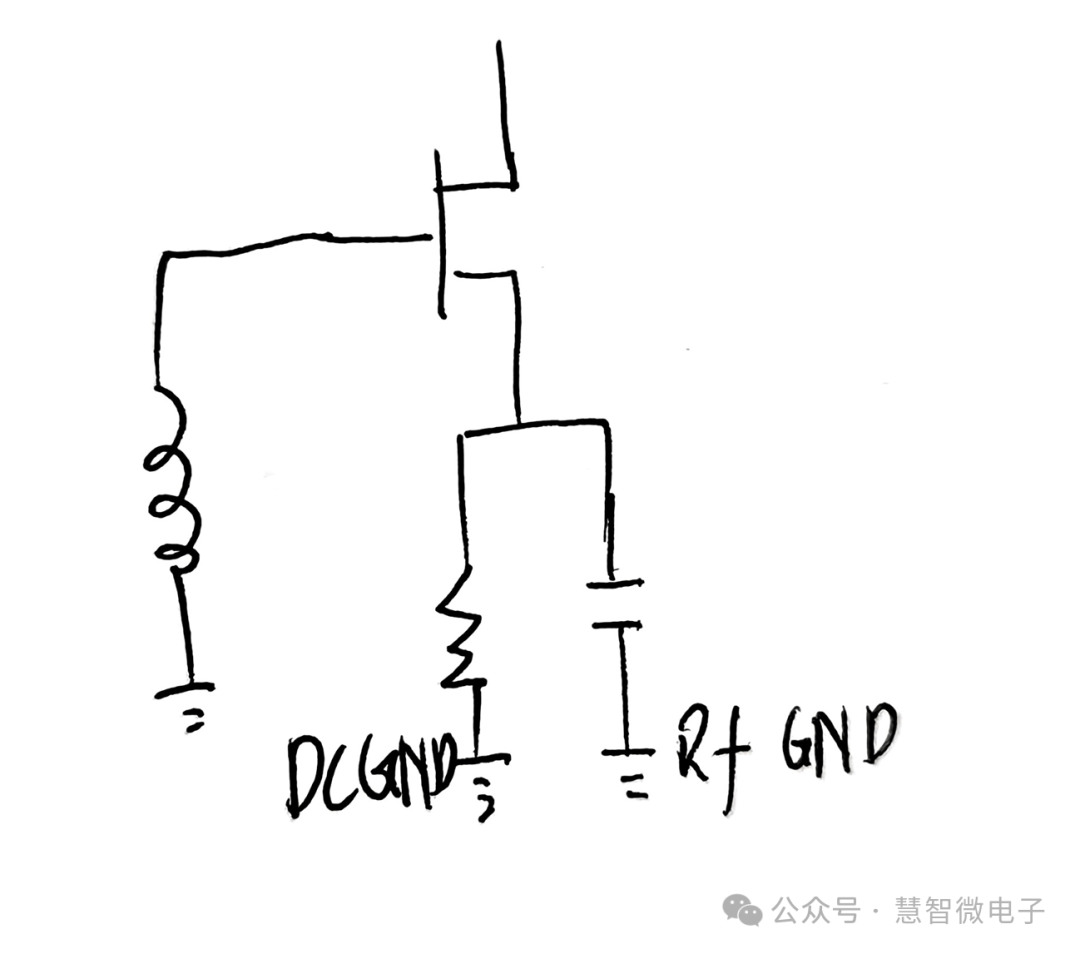

Q:请教一下大家,BJT发射极加负反馈电感我能理解稳定性和增益考量,像这种还加RLC回路的作用是?

A:Source上一般都是稳定性。尤其有电感。

Q:我不理解他下面的电容和电阻,电感为了稳定性牺牲一部分增益这个理解。

A:要这个是负压吗?自偏置给负压吧,你的栅极是直接电感到底?

Q:不是,正压,我只是截了一部分图。

A:这个Vg=-0.9v啥意思呢?

Q:没仔细看,那应该是负压,这个与我的问题关系不大吧?

A:我就是好奇这个vg啥意思。没别的意思,没用过hemt。

Q:我是看到人家的设计图,有点不太理解所以请教一下。

A:可能是为了让高频和低频引入的反馈量不同吧。看着像是让低频引入的负反馈更深一些。

A:这是负压管子。通过栅极chock接地让栅压等于0,然后电阻垫在源极产生压差,让源极电压等于-Vgs,电容提供射频接地,这样相当于源极没反馈,这种管子的Vgs一般是-0.几V。

Q:就是提供负压偏置对吧?

A:是。

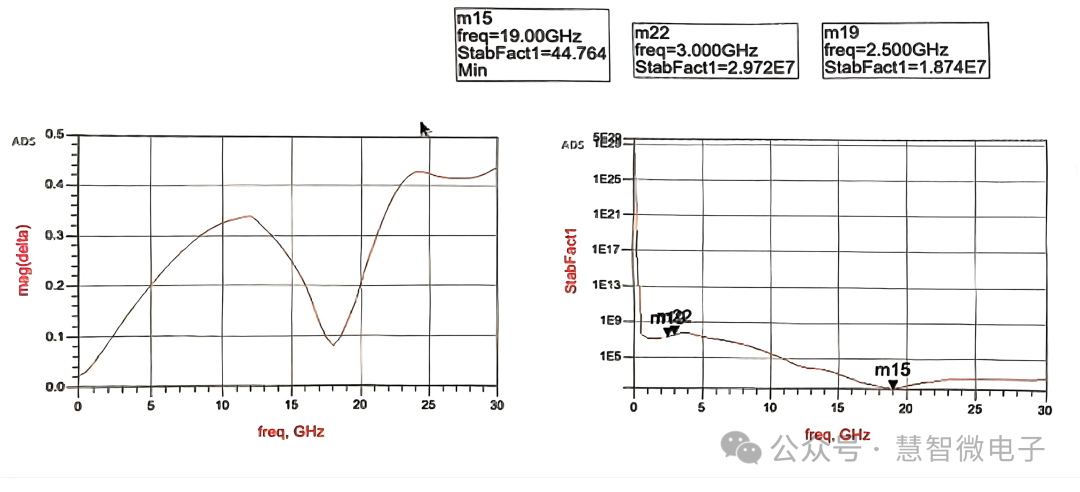

K、delta满足稳定性要求,也可能会自激吗?

Q:家人们,关于自激的问题,即使是K、delta满足绝对稳定的要求,也可能会自激嘛?

A:不会,不然为什么叫绝对稳定。

Q:我没太明白 ,现在我遇到一个问题,仿真结果稳定性都满足绝对稳定的要求,但是还是自激。

A:你是怎么个自激情况?

Q:我人都傻了。

A:在哪里自激呢?

Q:K最小值在44,低频2.8G自激。

A:你怎么知道自激,看着图应该不会自激呀。

A:你的自激是咋自激,实测还是仿真?

Q:因为我测试自激,这个仿真

A:测试那就是另一码事了。。

Q:啥意思?

A:测试有太多不确定因素了,你看看测试的 参数和仿真的对得上吗?

Q:增益低了10dB,单独测试自激的。

A:仿真仿不出来所有情况,而且加工和设计会有偏差,有的地方如果敏感,差一点可能就没了。

Q:不加激励,2.8G有频谱分量最高。

A:哦哦,专门测试自激的吗?

Q:就是不加激励,看频谱嘛,我猜测可能是工艺角的问题,这也太难受了,这个稳定性仿真把控不住嘛。

A:搞射频不就是永远在排查问题嘛。

Q:经验之谈啊

A:给我的感觉是kf并不是一个比较好的稳定性参数。

kf越大并不表明电路越稳定Cadence里面有个b1f大于0就是稳定的这个是越大越稳定可以看一下它在你自激的频率是不是很接近0

Q:好的,我试一试。

A:这个连小信号都差这么远。还是检查实际的装片吧。

Q:可能就是因为自激才出现对不上吧。

A:因为装片或者打线,把阻抗拉偏了,导致稳定性下降吧。

A:你要说自激影响,你仿真又看不出问题。

Q:有这种可能。

A:那这个问题不就无解了。

A:有加稳定性网络吗?

Q:我稳定性仿真远远满足要求,就没必要加了嘛,通过仿真k、delta在设计前期,不能把控这个自激问题嘛?

A:至少不会接个直流就自激。

A:你的模型和实测对得上就没问题。

A:大家都很关心稳定性问题啊。

Q:一自激,就真的寄了。

A:它这个如果只是前仿真自激的,在后仿或者电磁场仿真的阶段的话,考虑上寄生电阻效应,是不是自激的问题可能就不存在了?

Q:整体版图仿真结果 。

A:工艺角偏差确实会影响,或者整版提取的一些简化造成了sp不准。比如有些栅极和漏极vdd的一些退耦电容是可能引入不好的反馈回路,造成自激,如果抽版图简化了关键退耦,可能就仿不出来了。另外,理论上讲,稳定性系数没问题,你搭建的电路的小信号应该是稳定的,(如果差分端口的话,差模共模稳定性都得看)。然后,中间级自激,也会在输出产生杂波并且吃增益,这种情况不知道sp的稳定性系数能不能看出来。

Q:非常感谢大佬的指导。差模与共模的稳定性怎么仿真呢?仿真相位裕度嘛?

A:这个没啥特别的,就是现在很多电路都是差分的,仿真的时候习惯用理想巴伦转单端接port看sp,这种仿出来就只有差模性能了,稳定性也只能体现差模的。就需要中心抽头加port额外仿一下共模稳定性。不过纯单端电路就不涉及这种区分仿真。

Q:好的,明白了非常感谢

LNA S11大于0是什么原因导致的?

Q:请问做LNA的时候 S11大于0引起的自激是什么原因导致的?

A:诸多原因,和你用啥结构也有关系,但归根到底个人认为还是cgd的影响。

Q:那有什么办法可以改善稳定性呢?

A:在Source接传输线。不过你确定你测量校准没问题吗?你测量的k和u都是多少呢?或者电感也可以,不过低频快速测试的话找段传输线更好找。我碰到的S11>0都是校准有问题。

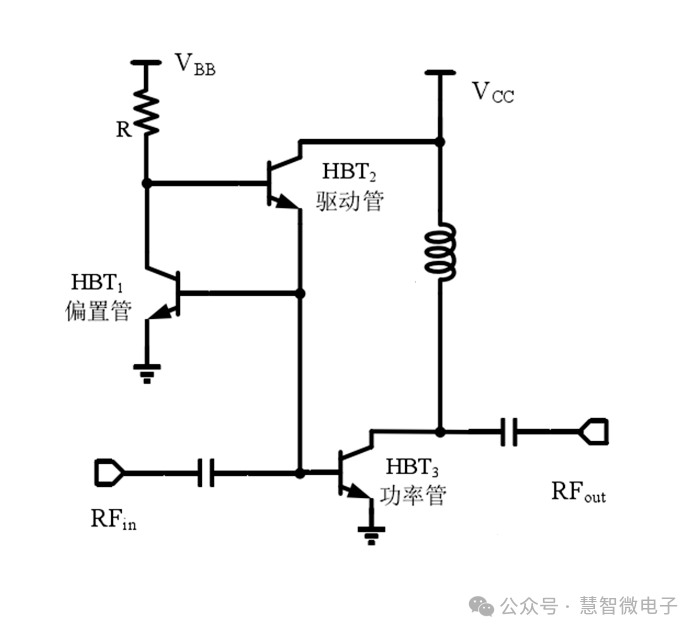

HBT PA偏置电路的理解

Q:能问一下这HBT1和HBT2的作用怎么理解吗?

A:这个管1和管3对管设计,管子3的基射电压不变,所以将管子1的基射电压钳住,无论常温还是高温,基射电压不变,管子2和管子3的当做二极管看,电流通过调节R实现。

PA高温时基射电压会变,偏置点会漂移,导致大功率下的增益和线性度会变差,这样钳住可以减缓。

Q:这个管2和管3当成二极管看,有点没太理解

A:就是13管子的vbe想同,所以3管子的电流取决于1,1管子的电流又取决于2管子的基级电压与vb的差。2管子的基级电压可以认为是确定的就是2倍的vbe,一般功放不这么用。这是个电流镜,电流镜偏置在大功率下缺点很明显。

Q:谢谢解惑

Loadpull的去嵌入应该如何来做?

Q:求助大佬们有没有做过Load pull的去嵌入?Texture该怎么处理呀?

A:夹具去嵌?

Q:算是吧,想去掉Pad。

A:TRL

Q:好滴,我去试试。

如何仿真差模稳定性?

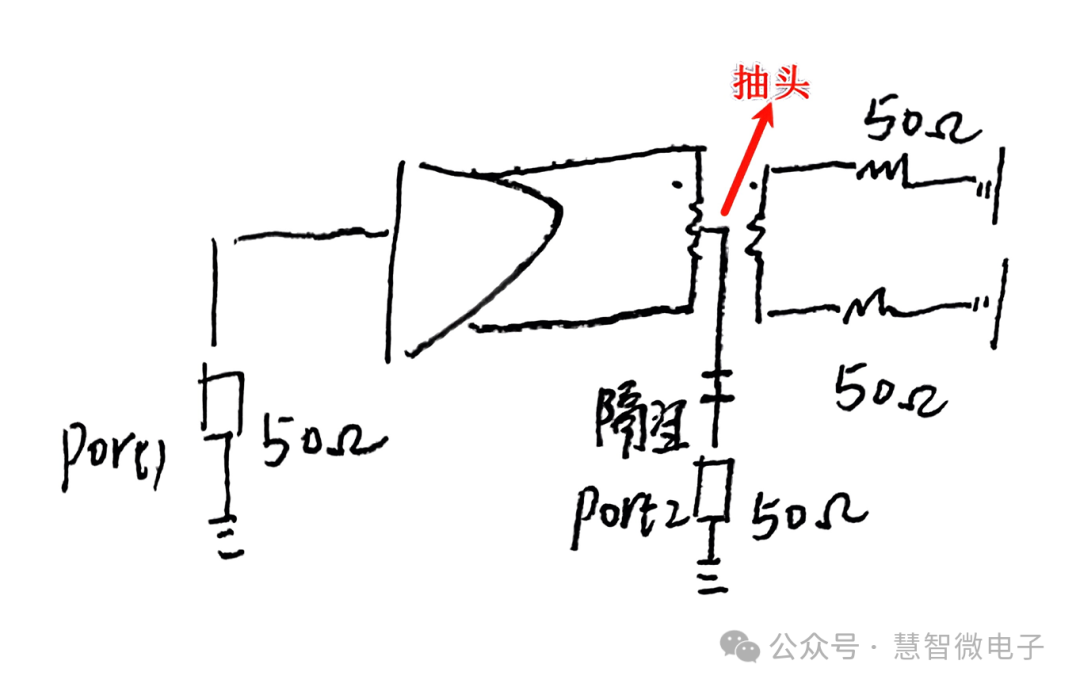

Q:您好,请问一下,差模稳定性,这样仿真可以嘛?输入单端,输出是差分,变压器是匹配电路,在抽头处加了隔直电容,设置Port2,50Ohm.

A:输出加个理想巴伦,用一个port看👀

Q:加理想balun,看的不就是差模嘛?你说的是ADS四端口Balun嘛?

A:对,加在你的输出变压器后面。

Q:哦哦好的,多谢老哥。

||扫描上面二维码,即可加入射频学堂VIP,获取1000+学习资料 ||广告,商务合作,会议推广等,请 + VX:RF_Centered 版权声明:射频学堂原创或者转载的内容,其版权皆归原作者所有,其观点仅代表作者个人,射频学堂仅用于知识分享。如需转载或者引用,请与原作者联系。射频学堂转述网络文章,皆著名来源和作者,不可溯源文章除外,如有异议,请与我们联系。