资讯 Verilog语法: 必须掌握的User-defined primitives (UDPs)

Verilog语法: 必须掌握的User-defined primitives (UDPs)

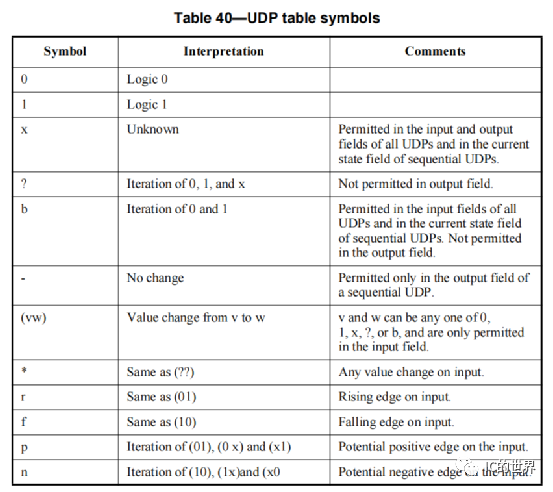

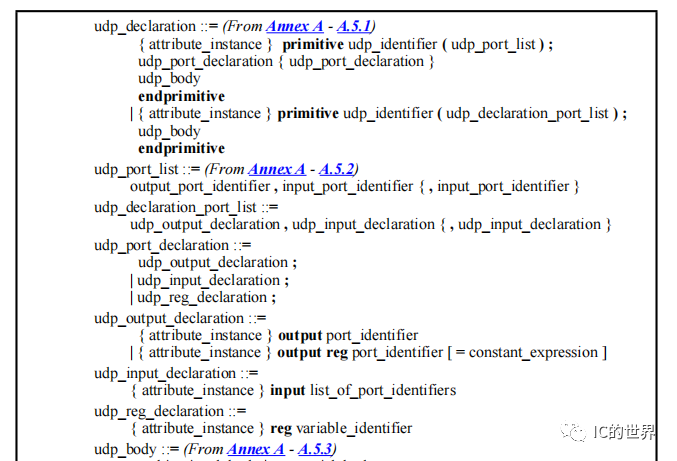

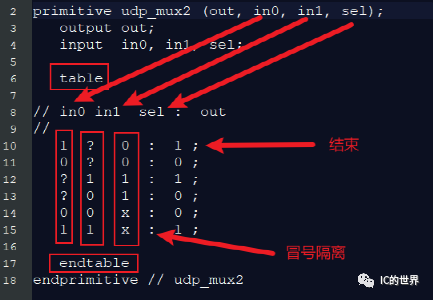

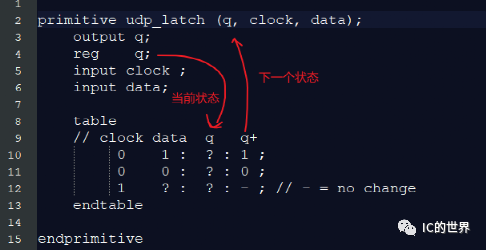

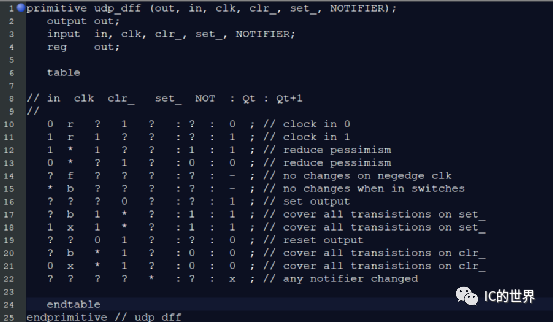

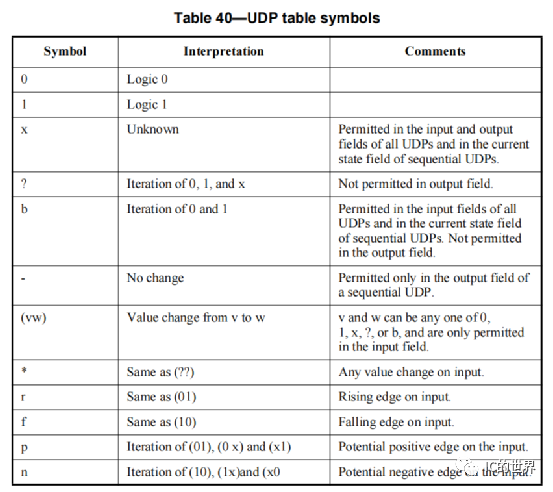

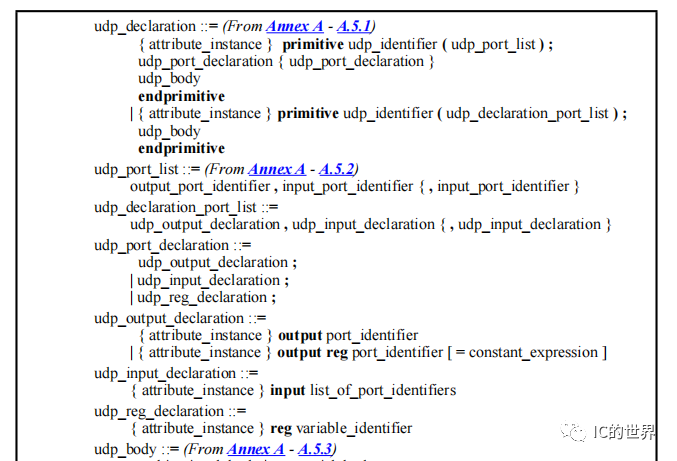

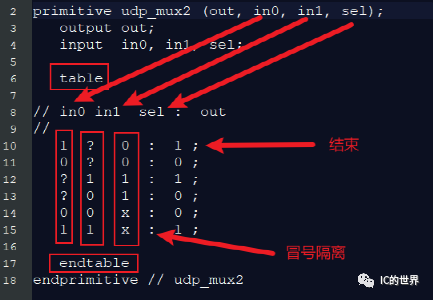

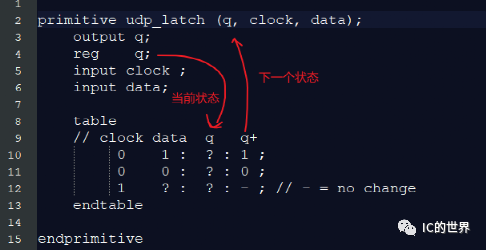

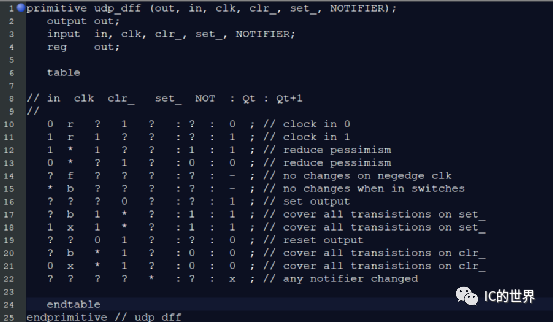

User-defined primitives (UDPs) 翻译过来就是用户自定义原语,常常用于构建组合逻辑模型和时序逻辑模型。 我们编写Verilo代码时,定义寄存器使用的是reg 和always@(*clk*),运行VCS RTL仿真时,VCS能够识别此类信号是寄存器,能够模拟其行为模型。 然而在使用VCS进行网表仿真时,此时网表中寄存器名称是这样的SDFF*_XXXX,其中SDFF_XXXX是每个寄存器类型对应的标准Cell的名称。 SDFF_XXXX是每个Fab厂家独有的名称,且在Verilog规范中并没有相关术语,那么VCS等EDA仿真工具是如何识别并且模拟其器件行为的呢 ? 实际上进行网表仿真时,EDA工具会读取对应SDFF_XXXX的UDPs模型,从而进行SDFF_XXXX的行为模拟。 UDPs的分为combinational UDP(组合逻辑)和 sequential UDP (时序逻辑)。 combinational UDP用于构建组合逻辑模型,常见有mux模块. sequential UDP 用于构建寄存器和Latch模型, sequential UDP 可以是边沿触发,也可以是电平触发。 UDP建模使用primitive表示建模开始,类似module,endprimitive表示建模结束,类似endmodule。 UDP模型在描述层级上与module/endmodule属于同一等级,因此primitive/endprimitive不能出现在module/endmodule内部,就像不能在一个模块里出现module~module~endmodule~endmodule. //语法错误 modulexxx(); primitive endprimitive endmodule 每个UDP有且只有一个输出,并且输出只有三种状态, 0 , 1 , or x ,不支持Z状态。 每个UDP可以由多个输入信号,如果输入信号为z,则当做X对待。时序UDP至少允许9个输入信号,组合UDP至少允许10个输入信号。 时序UDP可以使用initial语句定制仿真开始前output信号的初始值 状态表中使用的各类变量见表40。例如r表示上升沿,f表示下降沿。*表示数值改变。 状态表本质上就是一个输入信号/输出信号组合的列表。 组合UDP状态表中有 一个 冒号“:”,用于隔离输入和输出信号。 时序UDP状态表中有当前状态,还有下一个状态,因此有 2个 冒号“:”,用于隔离输入、输出(当前状态)和下一个状态。 组合UDP模型中,如果输入信号状态组合在状态表中没有指定,则输出会是X。 如下案例为2选1的mux,sel为1时,out为in1;sel为0时,out为in0。 请注意:信号列表中,输出信号out在第一个。状态表中,out处于最后一列。 使用reg申明了一个内部变量,表示当前状态q,即当前udp的输出状态。 table中的q+代表的是下一个有效周期的输出状态。 其中NOTIFIER信号用于建立时间和保持时间检查,通过建立时间和保持时间检查,则NOTIFIER不变,时序检测不通过则NOTIFIER翻转,udp_dff输出为x态。 将primitive类比成module,将endprimitive类比成endmodule,将table 类比成case,将endtable类比成endcase,你就知道该怎么写UDP模型了。 虽然使用UDP能够构建网表时序逻辑和组合的逻辑的行为模型,但是仿真终究是仿真,无法做到与实际芯片行为完全一致,特别是在部分信号为X态时。因此网表仿真中如果X态的出现导致仿真出现问题,此时不代表电路真的存在问题,需要仔细分析原因,其中需要重点分析UDP模型是怎么写的。

[ 新闻来源:eetop,更多精彩资讯请下载icspec App。如对本稿件有异议,请联系微信客服specltkj]

0