Chiplets/CoWoS,ADR时代的王者!冯明宪博士受邀参加“2023 SiP系统级封装现状及发展趋势大会”深圳站

文:王世权 编辑:田果

2023年6月9日,由广东省电子学会SMT专委会、深圳市终端电子制造产业协会主办,深圳市华友终端电子展览有限公司承办的“2023半导体封装制造国际论坛深圳站-SiP系统级封装现状及发展趋势大会”在深圳市沙井浩悦格兰云天国际酒店成功举办,亚太芯谷科技研究院院长,北京水木梧桐创业投资管理有限公司资深管理合伙人、深圳市芯榜信息科技有限公司执行董事冯明宪博士受邀参加并作“Chiplets:技术架构,产业发展与投资展望”主题报告。

下面就冯明宪博士的部分观点与大家分享:

近期,市场上有两颗重量级芯片问世,分别是英伟达的DGX GH200超级计算机芯片和苹果的M2 Ultra芯片,代表当前全球半导体业最先进性能的两颗芯片均采用了Chiplets 技术,而两家厂商英伟达与苹果公司的市值也在近期创了历史新高,英伟达更是成为了第一家市值破万亿美元的半导体公司,这进一步加强了我们对Chiplets 技术及产业、投资研究的信心,本报告就亚太芯谷科技研究院团队近期的研究结论与大家分享,也诚恳的希望业内先进能进一步的沟通交流。

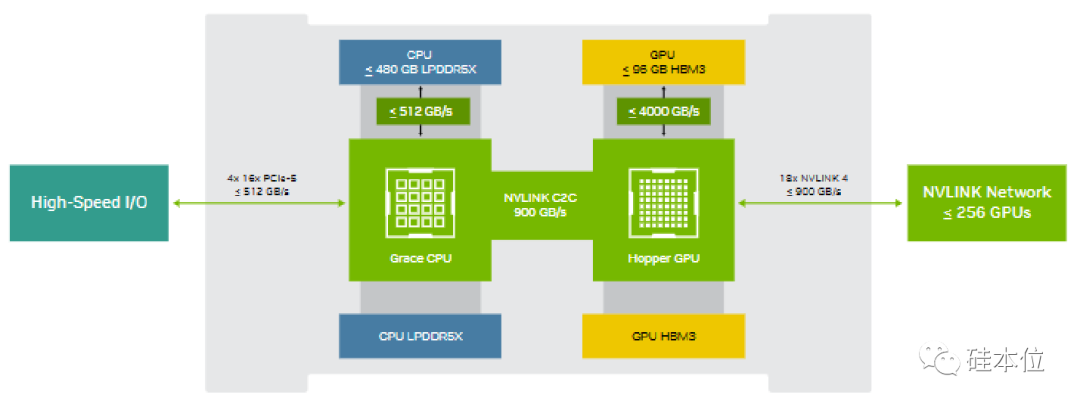

根据Nvidia的官方资料,该DGX GH200超级计算机将基于其Grace Hopper superchip,在DGX GH200中,可包含多达256个Grace Hopper 超级芯片,能提供高达1 EFLOPS的AI算力,另外每个DGX GH200中,都能提供高达144TB的内存,GPU和CPU之间的带宽则达到了900 GB/s。

DGX GH200 结构示意图

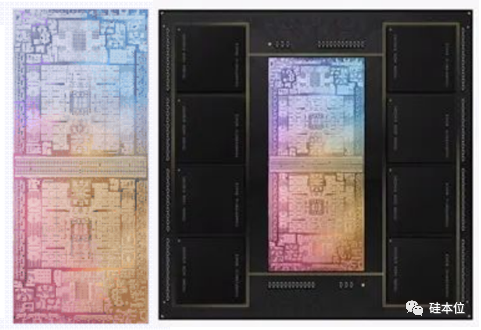

M2 Ultra芯片通过采用突破性的UltraFusion架构,将两块M2 Max芯片拼接到一起,拥有1340亿个晶体管,被苹果称为“芯片怪兽”(a monster of a chip)。比上一代M1 Ultra多出200亿个。与 M1 Ultra 相比,M2 Ultra 的 CPU 性能提升了 20%,GPU 性能提升了 30%。不过,神经引擎核心保持在32个。

M2 Ultra芯片结构图

1、脱颖而出的CoWoS技术

长久以来,台积电一直是英伟达 GPU 芯片的主要供应商,其先进制造工艺是推动英伟达在AI市场所向披靡的最重要因素,助力英伟达不断挑战芯片性能极限。而业内也将注意力集中在了英伟达新产品的结构、性能以及台积电的先进制程方面,后段封装技术的价值被严重的低估。

亚太芯谷科技研究院团队自去年起聚焦于Chiplets技术,并坚定的认为Chiplets 技术是未来半导体产业发展的主要推动力量之一,同时也是中国大陆突破欧美日半导体产业技术封锁的主要途径之一。

在对Chiplets技术进行深入研究的过程中,我们一直试图确定其技术发展路线,并提出了一些设想,直至近期业内爆出台积电CoWoS产能不足,终于确认了我们团队对于先进封装与Chiplets技术路线的一些判断。

据中国台湾经济日报报道,英伟达等HPC客户订单旺盛,客户要求台积电扩充CoWoS产能,导致台积电先进封装CoWoS产能吃紧,缺口高达一至二成。报道称英伟达向台积电追加 CoWoS(晶圆级芯片)封装订单,在 2023 年预定量基础上,再追加 1 万片,以满足需求。台积电的 CoWoS 月度封装产能在 8000 至 9000 片晶圆之间,多余订单则选择委外给全球最大封测厂日月光承接。

即CoWoS已经成为采用Chiplet技术的HPC产品封装的主要技术手段及不可或缺的关键。

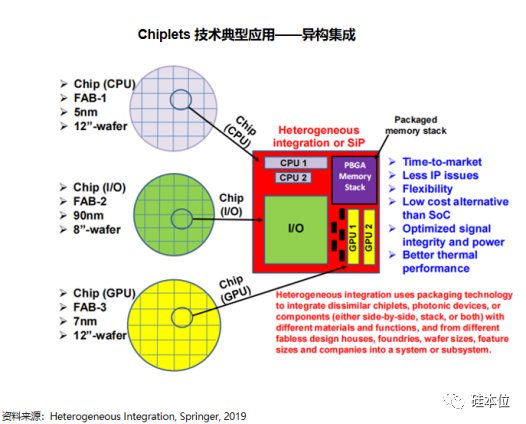

2、ADR时代Chiplet 与 CoWoS

2015年,Marvell创始人周秀文博士在ISSCC 2015上提出Modular Chip(模块化芯片)概念,被行业视为Chiplets 的雏形。Chiplets本质上是将不同的Die(裸片)整合到一起,只要每个Die之间的接口兼容,那就可以完成整合。因此除了接口以外对于每个Die其实不会有太多的要求。Chiplets不光可以使用不同厂商的Die,还可以使用不同工艺甚至不同材质的Die。这样可以使企业在成本和定制化需求方面有更好的选择。例如部分不需要先进工艺的电路可以使用成熟制程制造,这样可以节约成本。

Chiplets技术是对传统片上系统集成模式的革新,并因其可以大幅减小芯片的面积和功耗、提高芯片性能和能效比特点,被广泛应用于服务器芯片。

Chiplets技术的实现需要有先进封装技术为基础,支持Chiplets的主流封装技术主要有MCM、CoWoS 、EMIB。其中CoWoS技术得到了高端处理器和 GPU 等高性能芯片厂商的一致认可,被包括英伟达、AMD、苹果、高通、海思等芯片制造商及谷歌、亚马逊、微软等其他科技厂商采用。

CoWoS 技术出现在 2000 年代初期,当时主要是用于高端显卡和处理器的制造。该技术采用高速电线和芯片之间的接触点作为数据传输的接口,可以实现高速、高精度的数据传输。

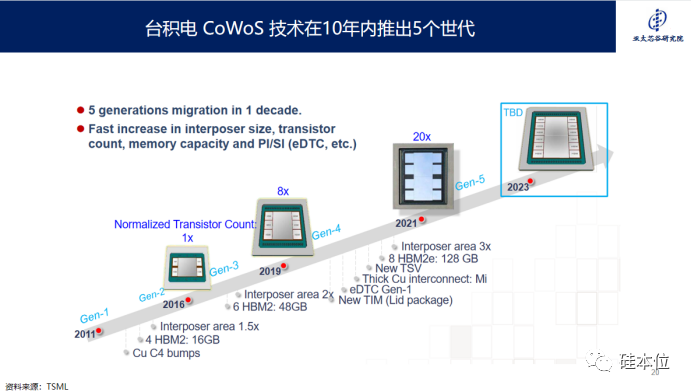

在 2010 年代,台积电推出了改进的 CoWoS 技术,称为 CoWoS 2.0。该技术通过增加电线的数量和改进电线的形状,可以提高芯片的传输速度和传输距离,从而提高芯片的性能。同时,台积电还采用了新的焊接技术和材料,以提高芯片的稳定性和可靠性。之后, CoWoS 技术历经了五次迭代,成为了众多国际厂商的首选,并预计在今年将推出第六代。

随着CoWoS 被众多国际高端处理器和 GPU 等高性能芯片厂商的一致采用, 其与Chiplets技术组合必将成为ADR时代推动半导体产业发展的最重要推手之一。

3、Chiplets/CoWoS产业发展与投资机遇

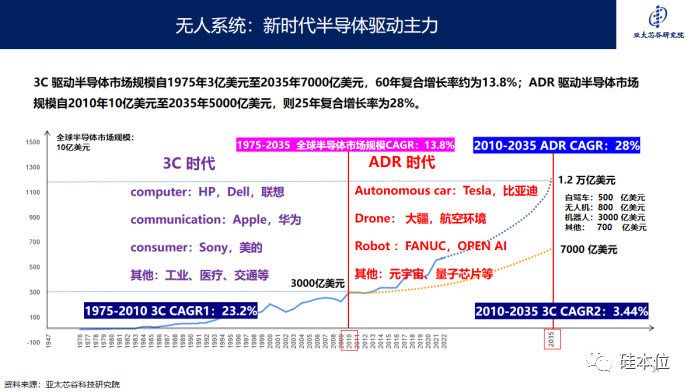

在6月2日举办的2023 第七届世界无人机大会暨第八届深圳国际无人机展览会”分论坛“无人系统智能芯片技术论坛”中,冯明宪博士提出了“ADR”的概念,即自动驾驶汽车、无人机、机器人,并认为ADR已经取代过去的3C成为了半导体发展的驱动主力。

我们现在从投资的角度来看,在3C时代,全球半导体市场规模在1975年到2010年期间的年复合增长率为23.2%,是非常具备投资价值的;然而,在2010年到2035年的年复合增长率将大幅下降至3.44%,与此同时ADR推动的全球半导体市场规模年复合增长率则将达到28%。由上述数据可以推断,没能跟随进入ADR时代的相关产业投资价值已大幅降低。

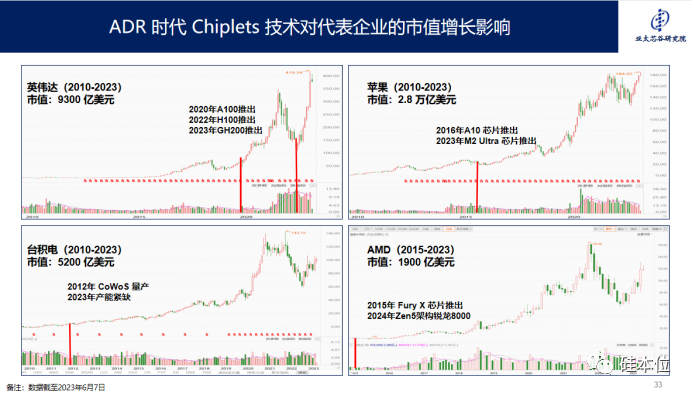

反应到资本市场,英伟达、苹果(跨越3C与ADR时代)市值已创历史新高,台积电、AMD也紧随其后。而尚未完成跨越到ADR时代的英特尔则表现平平,未能实现跨越的3C时代代表性企业联想则相对表现最差。

因此,在新时代的半导体产业发展及投资应更多的关注ADR相关的企业,参考亚太芯谷科技研究院的投资逻辑,在企业发展的5-15%阶段入场,在陪伴企业发展的过程中获取最大的投资收益。

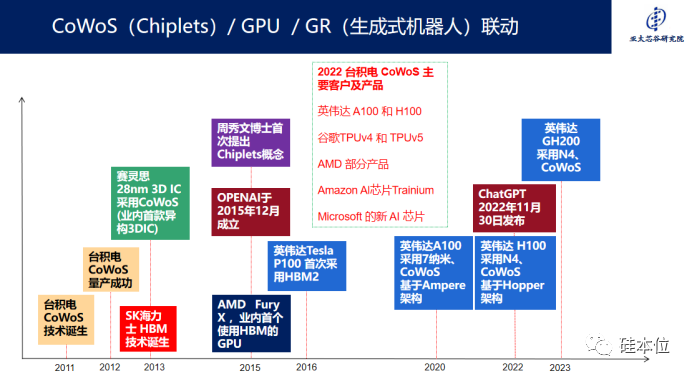

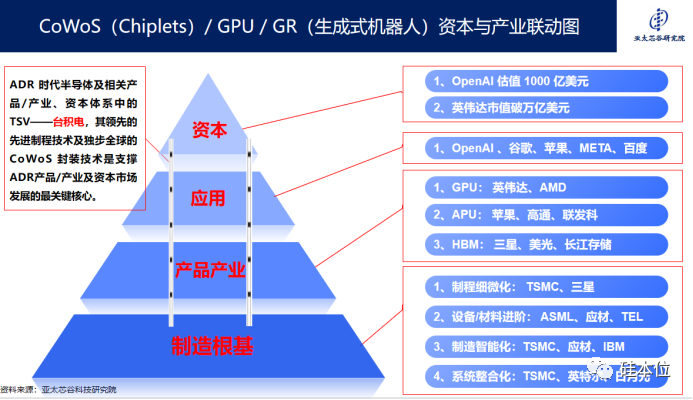

在ADR时代的三个主要科技产业中,冯明宪博士认为GR(生成式机器人)将是一个重要组成部分,并对CoWoS(Chiplets)、GPU 、 GR(生成式机器人)的资本与产业联动关系做了形象的说明,如下图所示:

可见制造根基撑起了相关产品/产业的发展,及后期的市场应用与资本市场,其中具备先进制程制造与先进封测能力的台积电成为了这个体系中的“TSV”,贯穿了整个体系,起到了支撑、连接的关键作用。

最后冯明宪博士特别强调,以上数据及结论均为亚太芯谷科技研究院团队的一家之见,可供大家参考,但不够成投资依据,也希望能与业内人士共同探讨、优化。

4、ADR时代冉冉升起的半导体行业新星

在报告的最后,冯明宪博士介绍了几家研究院重点关注及协作发展的相关企业。

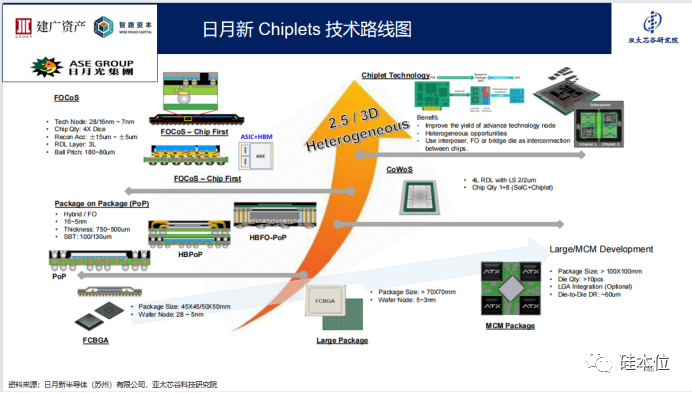

(1)日月新半导体(苏州)有限公司

日月新集团主要从事半导体元器件的封装测试业务。作为全球半导体封测知名企业,日月新集团为全球客户提供封装设计、前段工程测试、晶圆探测、后段半导体封装、成品测试的专业一元化服务,并且拥有集技术研发为一体的检测中心,以世界级先进设备和丰富的半导体封装测试经验,为客户提供完善的电子制造服务的整体解决方案。

日月新集团坚持以人为本,透过严谨的工程、纪律的生产, 使命达成第一的品质,以赢得客户的满意、成就永续的经营。

日月新苏州厂成立于2001年, 2007年日月光集团与NXP合资设立苏州日月新,2018 年日月光集团取得苏州日月新100%股权,拓展并服务全球半导体封装及测试市场。2021年12月, 智路资本与日月光集团完成股权转让, 更名为日月新半导体(苏州)有限公司, 且作为日月新集团总部。公司不断创新的思维,投注于半导体先进制程技术的研发,高素质的研发团队持续发展先进的技术与制程,满足客户对于强化产品功能与降低成本的需求,也获得多项技术专利。公司自成立以来,营收、获利、人员都保持快速增长,现有员工已超4000名。

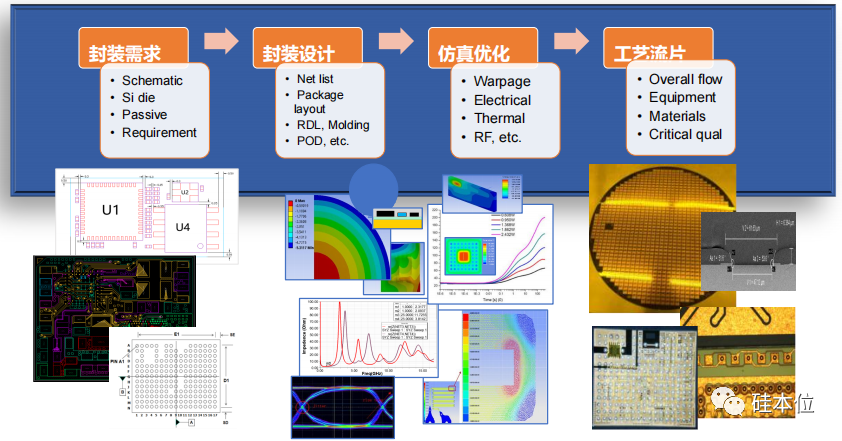

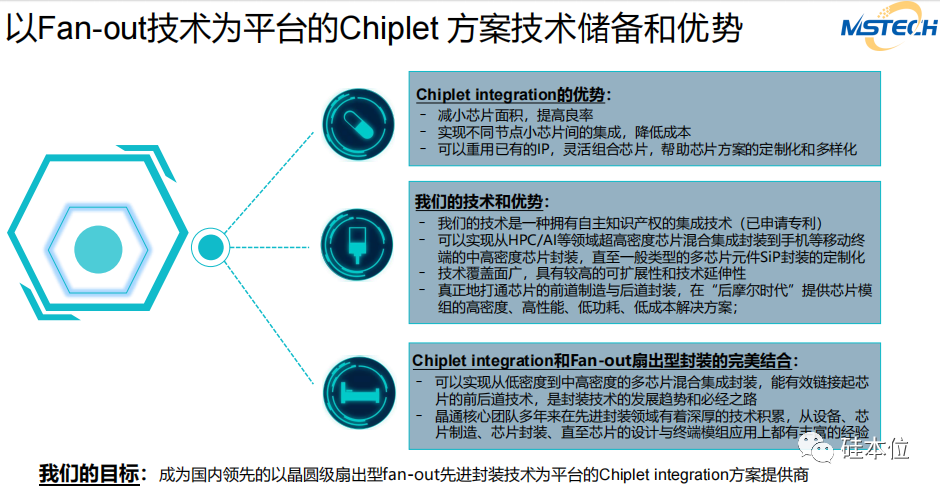

(2)杭州晶通科技有限公司

杭州晶通科技有限公司是国内领先的以晶圆级扇出型Fan-Out先进封装技术为平台的Chiplet integration方案提供商,成立于2018年7月。公司主要从事Chiplet Integration小芯片系统集成与FOSiP集成电路晶圆级扇出型Fan-out先进封装相关的系统集成、设计仿真、技术开发、产品认证、晶圆中测、晶圆级中道封装测试、系统级封装测试、芯片成品测试,为客户提供一站式解决方案

公司通过高集成度的晶圆级封装(WLP)、Fan-out、Fan-out PoP堆叠封装、多芯片Fan-out混合封装、Chiplet Integration小芯片集成技术DPR,高性能倒装芯片封装和先进的引线键合技术,涵盖了主流集成电路系统应用,包括网络通讯、移动终端、高性能计算、车载电子、大数据存储、人工智能与物联网、工业智造等领域。

公司在杭州、上海、江苏等地拥有研发中心、销售中心及生产基地,可与全球客户进行紧密的技术合作并提供高效的产业链支持,一期产线总建筑面积11000㎡,其中千级洁净区2300㎡,百级洁净区1200㎡,于2022年9月正式投产。

2023年2月16日,公司晶圆级fan-out先进封装产线在扬州高邮正式通线,并进入实质性的生产测试阶段。目前已签约订单超过亿元,未来将重点服务智能穿戴、射频芯片、物联网模块、手机等应用领域。公司的fan-out晶圆级扇出型先进封装,拥有多项自主产权,能进行多芯片3D整合封装即FOSiP封装,并能进行chiplet芯粒集成。公司的FOSiP方案针对不同应用场景和封装需求,可以定制化的采用face up、face down等不同fan out封装方式,能满足不同的封装精度要求,并实现多层3D的堆叠封装,提供性能与价格的最优方案,在国外完成研发中试,通过了国内外众多案例产品量产的过程验证。

3、沐曦集成电路(上海)有限公司

沐曦致力于为异构计算提供全栈GPU芯片及解决方案,可广泛应用于人工智能、智慧城市、数据中心、云计算、自动驾驶、数字孪生、元宇宙等前沿领域,为数字经济发展提供强大的算力支撑。

公司于2020年9月成立于上海,并在北京、南京、成都、杭州、深圳和武汉等地建立了全资子公司暨研发中心。沐曦拥有技术完备、设计和产业化经验丰富的团队,核心成员平均拥有近20年高性能GPU产品端到端研发经验,曾主导过十多款世界主流高性能GPU产品研发,包括GPU架构定义、GPU IP设计、GPU SoC设计及GPU系统解决方案的量产交付全流程。

沐曦打造全栈GPU芯片产品,推出MXN系列GPU(曦思)用于AI推理,MXC系列GPU(曦云)用于AI训练及通用计算,以及MXG系列GPU(曦彩)用于图形渲染,满足数据中心对“高能效”和“高通用性”的算力需求。沐曦产品均采用完全自主研发的GPU IP,拥有完全自主知识产权的指令集和架构,配以兼容主流GPU生态的完整软件栈(MACAMACA),具备高能效和高通用性的天然优势,能够为客户构建软硬件一体的全面生态解决方案,是“双碳”背景下推动数据中心建设和产业数字化、智能化转型升级的算力基石。

沐曦自成立之日起即保持着高速的成长性,展示出强大的人才号召力、产业资源聚集力、产品研发执行力和产业生态上下游布局能力。目前,沐曦已与服务器OEM、大数据中心、互联网运营商等行业客户建立了紧密的合作关系,并与众多知名高校和研究机构密切开展产学研合作,快速推进产业上下游生态的建设。立足未来,沐曦将积极发挥在GPU领域的优势,结合业务辐射地区的产业生态开展深度合作,助力我国集成电路产业和数字经济的高速发展。

沐曦主要业务包括(1)产品与(2)解决方案,和(3)异构计算、构建软件生态能力的MACAMACA运算平台,和(4)相关的技术支持与服务,其中产品系列包括三类:N系列、C系列、G系列。