FinFET全称Fin Field-Effect Transistor,中文名叫鳍式场效应晶体管,是一种新的互补式金氧半导体晶体管。FinFET命名根据晶体管的形状与鱼鳍的相似性。

FinFET发展概况

FinFET 的发展概况随着集成电路制造工艺技术的特征尺寸按比例缩小到 22nm 时,短沟道效应愈发严重,仅仅依靠提高沟道的掺杂浓度、降低源漏结深和缩小栅氧化层厚度等技术来改善传统平面型晶体管结构的短沟道效应遇到了瓶颈,器件亚阈值电流成为妨碍工艺进一步发展的主要因素。尽管提高器件沟道掺杂浓度可以在一定程度上抑制短沟道效应,然而高掺杂的沟道会增大库伦散射,使载流子迁移率下降,导致器件的速度进一步降低,这个结果是与工艺发展的目标相背离的。

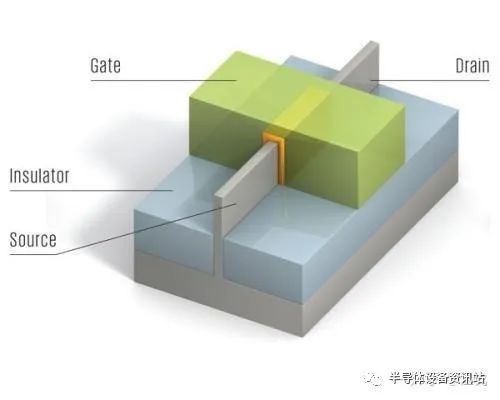

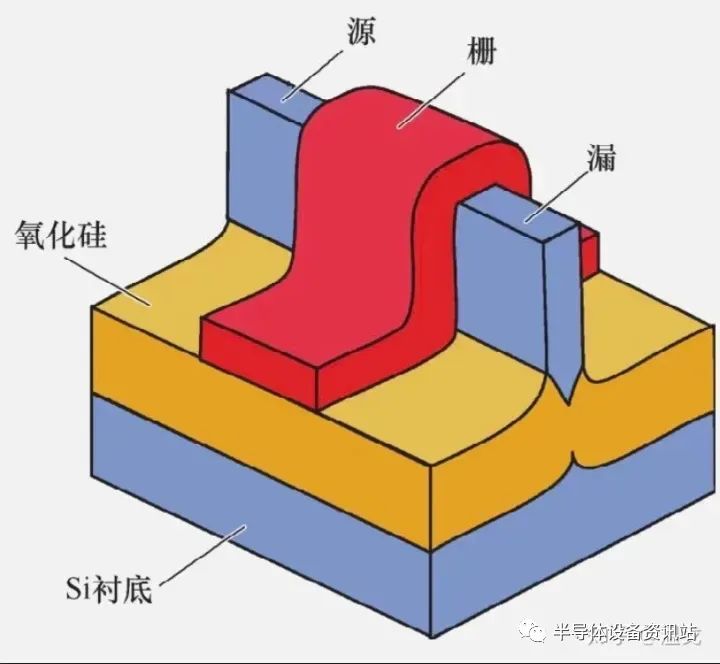

1989 年,Hitachi 公司的工程师 Hisamoto 对传统的平面型晶体管的结构作出改变,在设计 3 维结构 MOS 晶体管的过程中 ,提出了一种全耗尽的侧向沟道晶体管,称为 DELTA 晶体管(Depleted Lean-Channel Transistor,如图1所示,这种 DELTA 的结构与三栅 FinFET(Fin Field Effect Transistor)的结构十分相似。同时,在平面 MOSFET 领域中,研究者提出了顶栅和底栅联合控制沟道的双栅 MOSFET 结构,以降低短沟道效应。经过计算验证,这种双栅结构可以比 FD-SOI 更有效地抑制短沟道效应,并且数值模拟也表明其在尺寸按比例缩小方面具有较大的潜力,更适合用于制造 22nm 以下的集成电路。但是由于双栅 MOSFET 制作过程过于复杂,很难与现有的硅平面工艺兼容,所以没有在实际工艺技术中普及应用。

1998 年,美国国防部高级研究项目局(DARPA)出资赞助胡正明教授在加州大学带领一个研究小组研究 CMOS 工艺技术如何拓展到25nm 领域。胡正明教授在 3 维结构的 MOS 晶体管与双栅 MOSFET 结构的基础上进一步提出了自对准的双栅 MOSFET 结构,因为该晶体管的形状类似鱼鳍,所以称为 FinFET 晶体管 。1998 年,胡正明教授及其团队成员成功制造出第一个 n 型 FinFET,它的栅长度只有 17nm,沟道宽度 20nm,鳍(Fin)的高度 50nm。

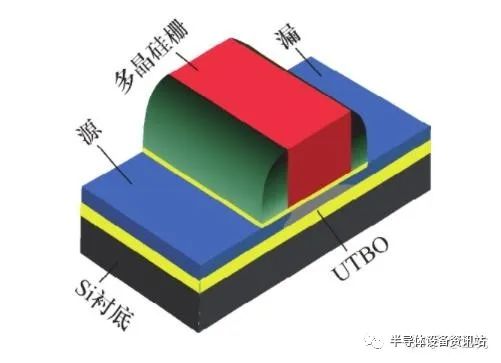

1999 年,胡正明教授及其团队成员成功制造出第一个 p 型 FinFET ,它的栅长度只有 18nm,沟道宽度 15nm,鳍的高度 50nm。胡正明教授除了提出 FinFET 晶体管,还在 PD-SOI的基础上提出了 UTB-SOI 晶体管。2000 年,胡正明教授及其团队发表了 FinFET 和 UTB-SOI 的技术文章,同年,胡正明教授凭借 FinFET 获得美国国防部高级研究项目局最杰出技术成就奖。

FinFET工艺技术

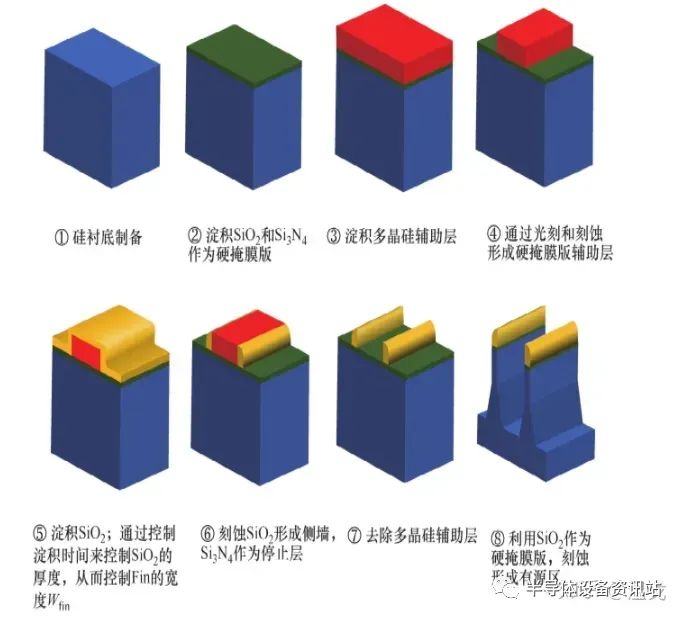

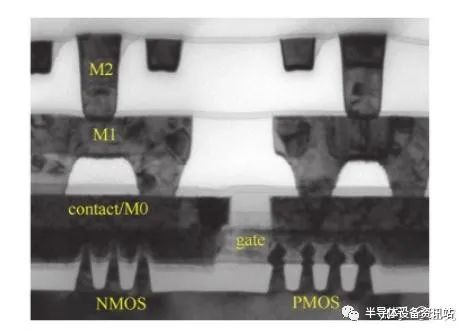

FinFET 的工艺技术与平面型 MOSFET 的工艺技术是不兼容的,FinFET 前段工艺制程采用了立体结构,同时包括 HKMG 技术和应变硅技术,后段依然是大马士革结构的铜制程。FinFET 工艺的难点是形成 Fin 的形状,Fin 的尺寸是最小栅长的 0.67 倍左右,对于 22nm 的工艺技术,Fin 的宽度是 14.67nm,它远小于最精密浸入式光刻机所能制造的最小尺寸。Fin 的有源区并不是通过光刻形成的,而是通过 SADP(Self-Aligned Double Patterning)工艺技术形成的,它只需要一次光刻步骤,然后通过类似栅极侧墙的辅助工艺制造出 Fin 的形状。

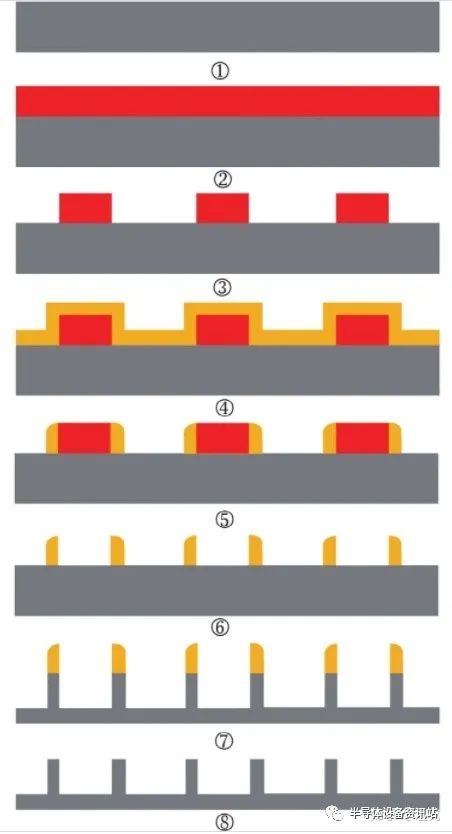

图 2 所示为 SADP 工艺流程图。首先淀积一层辅助层多晶硅或者 Si 3 N 4 ,然后通过一道光刻和刻蚀形成一个类似栅极的结构,通常称它为心轴(mandral),再淀积一层氧化硅作为硬掩膜版,通过控制氧化硅的厚度可以控制 Fin 的宽度 W fin ,利用干法刻蚀形成类似栅极侧墙的形状,去除辅助层,剩下的形状就是形成超薄的 Fin 的硬掩膜版,再利用干法刻蚀形成超薄的 Fin。

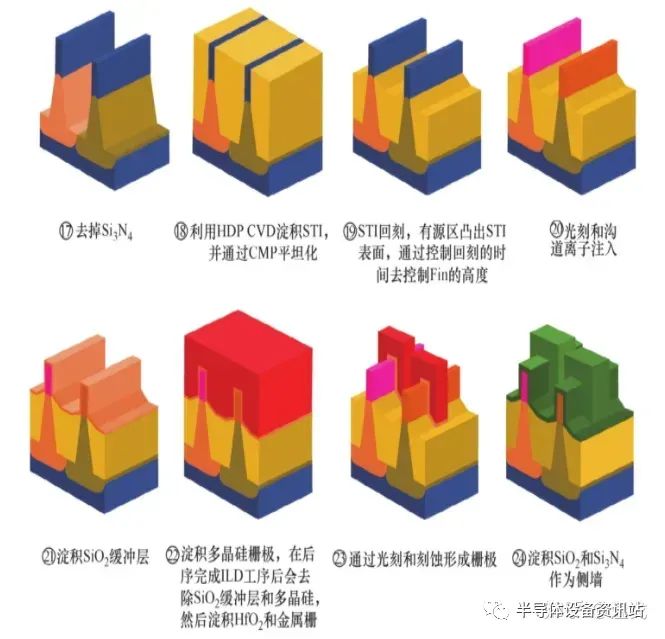

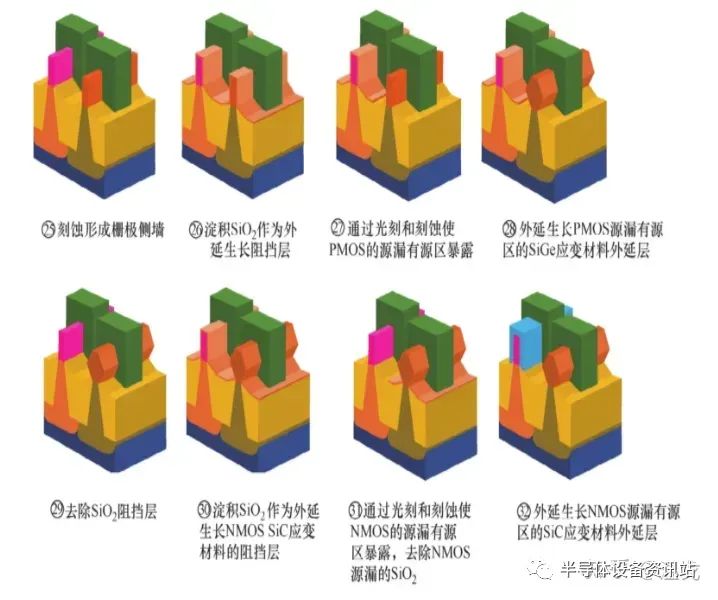

FinFET 工艺制程技术采用外延生长技术嵌入 SiGe 和 SiC 应变材料,并进行源和漏掺杂,同时使源和漏有源区凸起增加有源区的厚度和表面积,从而可以形成更厚的 Salicide,减小 22nm 工艺制程技术的源和漏的接触电阻,应变技术可以提高器件的速度,改善 FinFET 的性能。图 2-60 所示为 FinFET 沿栅方向的剖面图。左边是 NMOS,右边是 PMOS,它们都是通过多条很薄的指状的 Fin 有源区并联的方式增大器件的宽度,从而增大 FinFET 驱动能力。

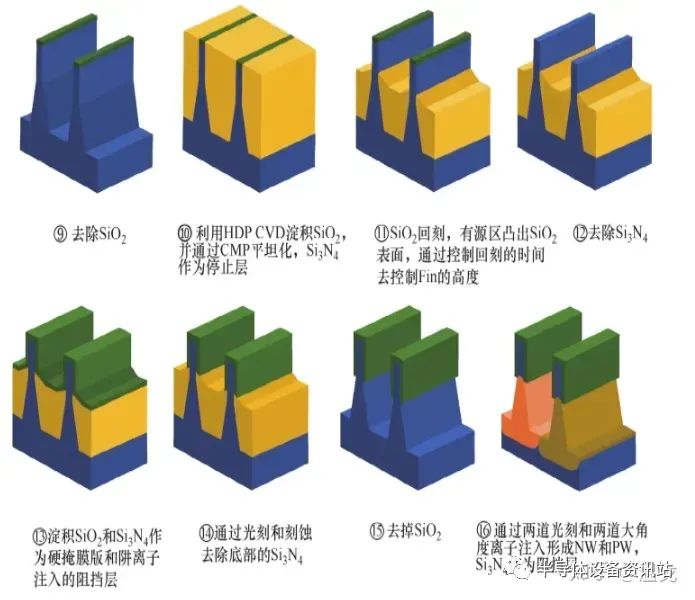

下图所示为 FinFET 工艺技术流程图,只是简单描述了前段工艺流程。[1]

FinFET沿栅方向的剖面图

参考

^《集成电路制造工艺与工程应用》 温德通