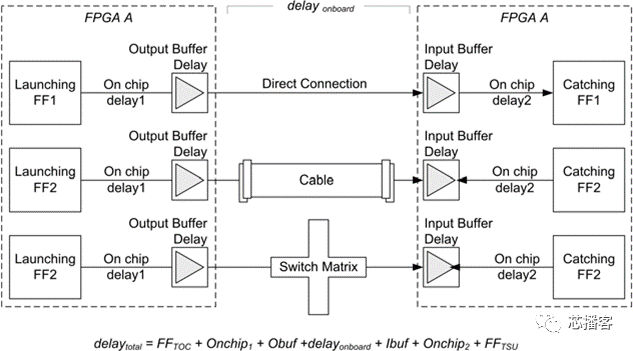

FPGA与FPGA之间互连对信号延迟的影响,两片FPGA的IO之间每一个额外的过渡,例如连接器、焊点甚至板内通孔,都会增加一些阻抗,从而降低信号质量,并增加信号之间串扰的概率。然而,经过仔细分析,发现这并不是一个想象中的大问题。主要矛盾是FPGA互连线的影响。比如,我们可以以如下图所示的三种连接模型方式表示:

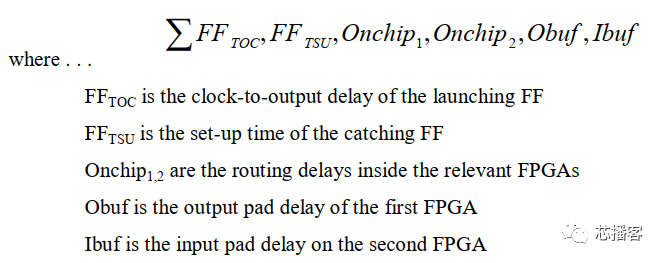

路径延迟由上图所示的表达式给出。每个互连方法的共同点是延迟分量,它是所有片内延迟和片内/片外延迟的总和,每个变量的意义如下表示为:

三种连接方式,除了Delay onborad这个时间不尽相同,其他时间是一样的,都是板间的各种连线以及器件的延迟之和,所以决定性因素还在于Delay onbaord时间,Direct Connection是最快的,Cable线互连和Switch连接方式的延迟会更长一些。当然,取决于FPGA原型验证供应商的PCB能力如何。因为Cable线的延迟大家基本都会选择专业的做线缆的公司提供的线缆。这么看来,站在不同的角度来看,这个速率的影响因素就各不相同了,如果你是FPGA供应商,那么提升自身PCB设计能力是基础,选择Cable是另一个方面。如果你是SoC供应商,那么,不同厂商的不同连接方式都需要考虑。

除了以上因素,还有其他RTL设计相关相关因素:

1. SoC设计中RTL的风格以及如何有效地将其映射到FPGA中

2. 设计中互连的复杂性,尤其是总线

3. 使用没有FPGA等效的IP块

4. 每个FPGA的资源利用率(50%左右是合理的)

5. FPGA之间互连的信号复用比(TDM比)

6. 将快速IO数据导入FPGA核心的速度

在典型的设计中,FPGA交换互连的IO之间信号的传播延迟时间不太容易预测,因为为了路由整个设计,一些信号必须通过多个转换元件。平均来说,有两次转换的遍历,但在非常大的设计的极端情况下,这可能高达八次,可能该设计被划分为多达20个FPGA设备。为了确保关键路径穿过尽可能少的转换电路,FPGA原型验证系统供应商必须开发并支持布线优化工具。此外,如果此布线任务可以在相关工程师的控制下进行,则工具的选项将变得非常广泛。这种并发分区和布线工具将在基于交换互连的系统上提供最佳结果,因此我们再次看到了为板提供复杂支持工具的好处。

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()