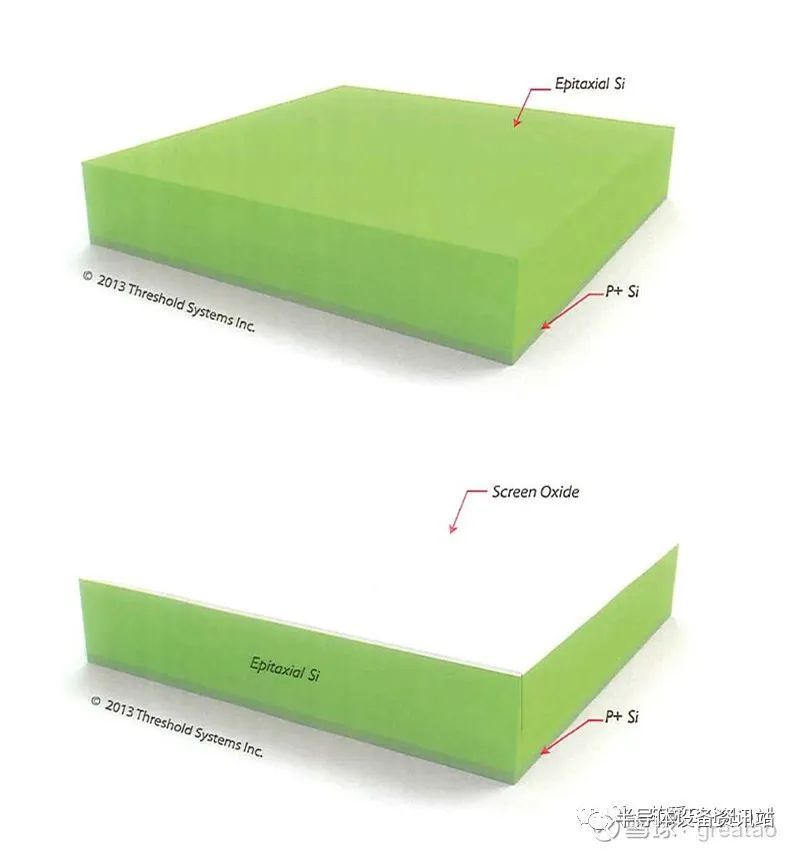

1. ScreenOxide Growth

首先是P型衬底上面有一层外延生长的Si

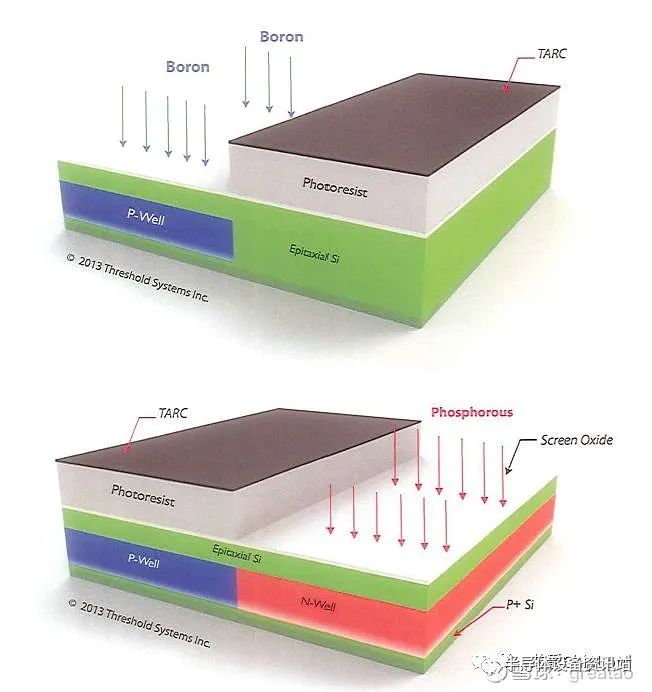

2. N-Well and P-Well Definiton

定义N-Well和P-Well

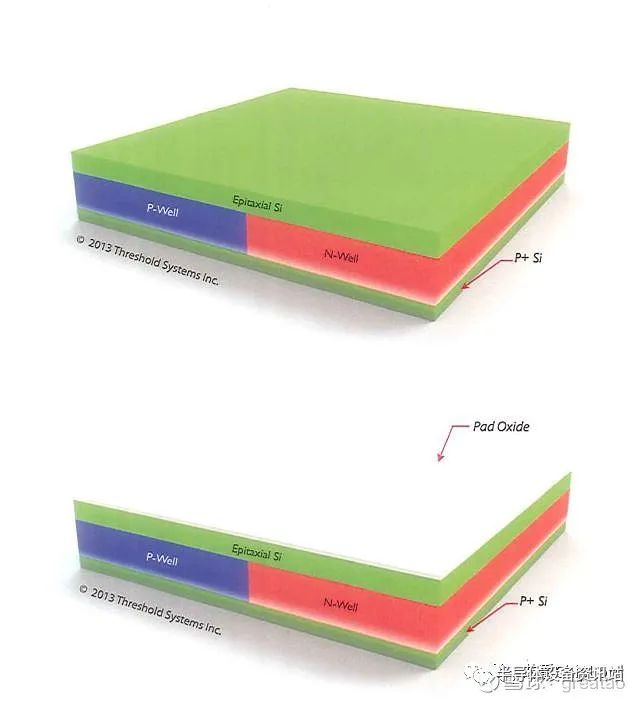

3. Photoresist Strip Pad Oxide Growth

然后去除光刻胶和Screen Oxide

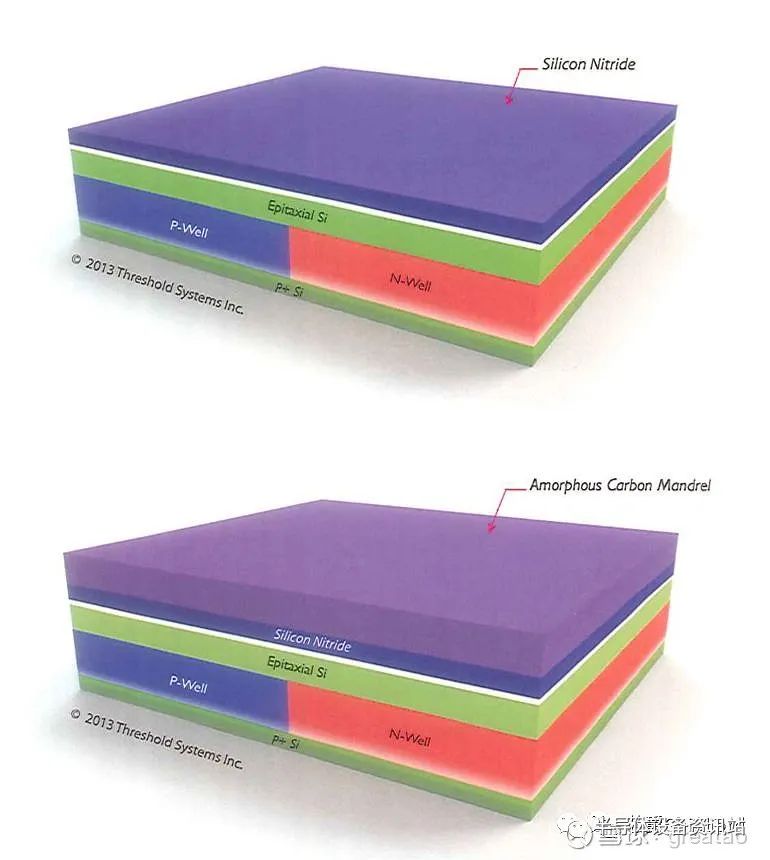

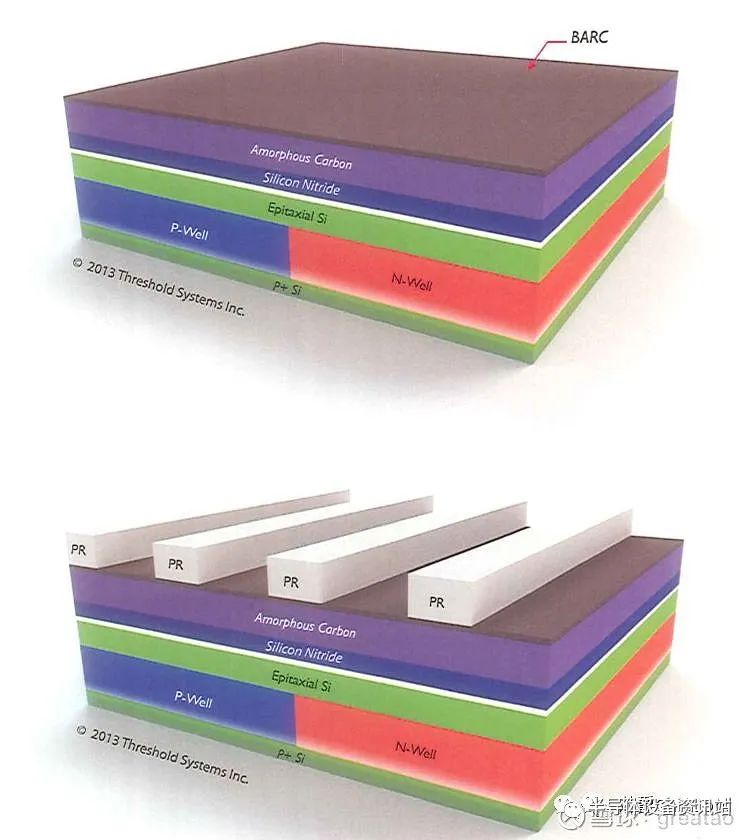

4. SiliconNitrideHardMaskDeposition

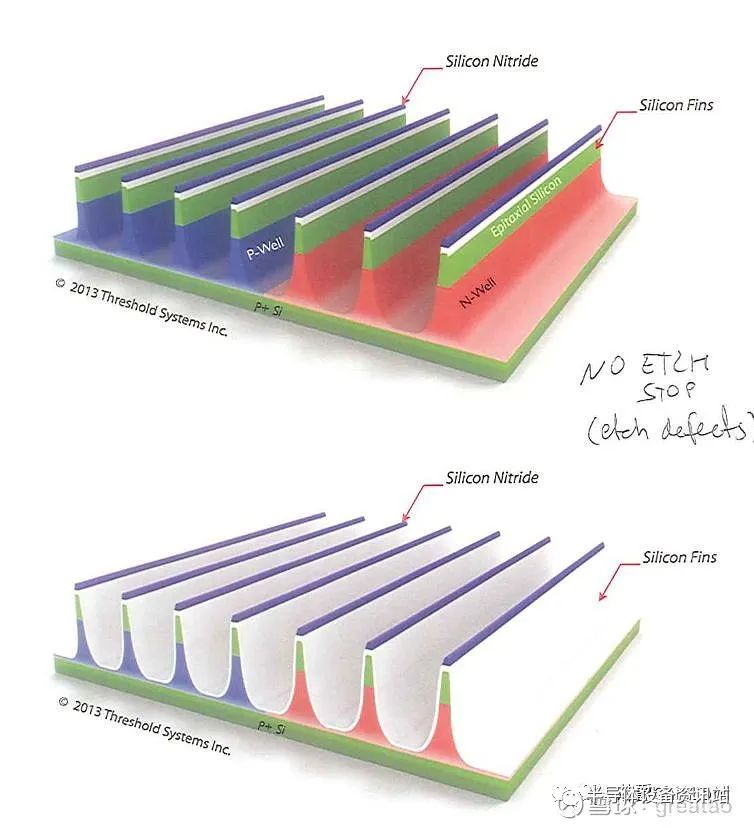

接下来的是Fin的形成

先是通过CVD工艺形成一层Silicon Ntride

5. Mandrel Patterning

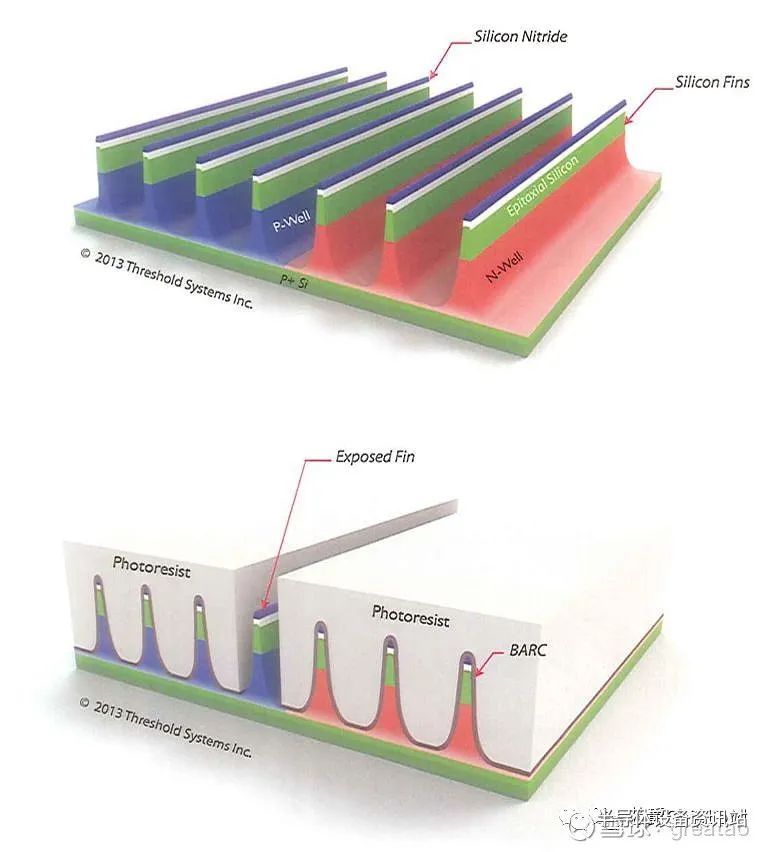

接着coating BARC和PR进行曝光

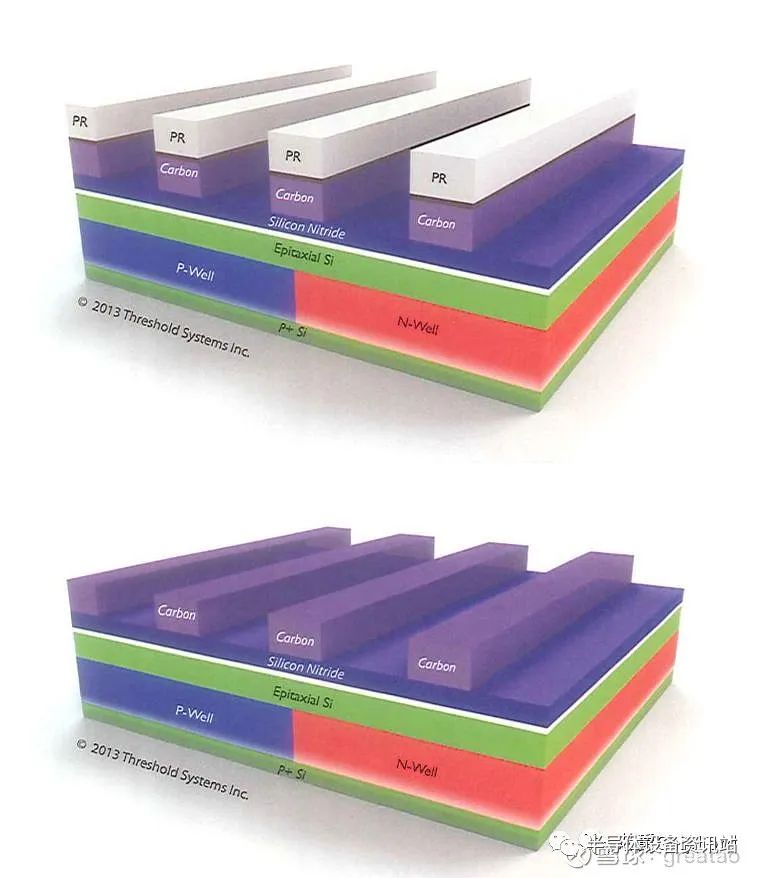

6. Mandrel Etch and PR Strip

etch向下吃到Silicon Nitride层停止

7. Oxide Space Formation

CVD工艺deposit一层Oxide Layer

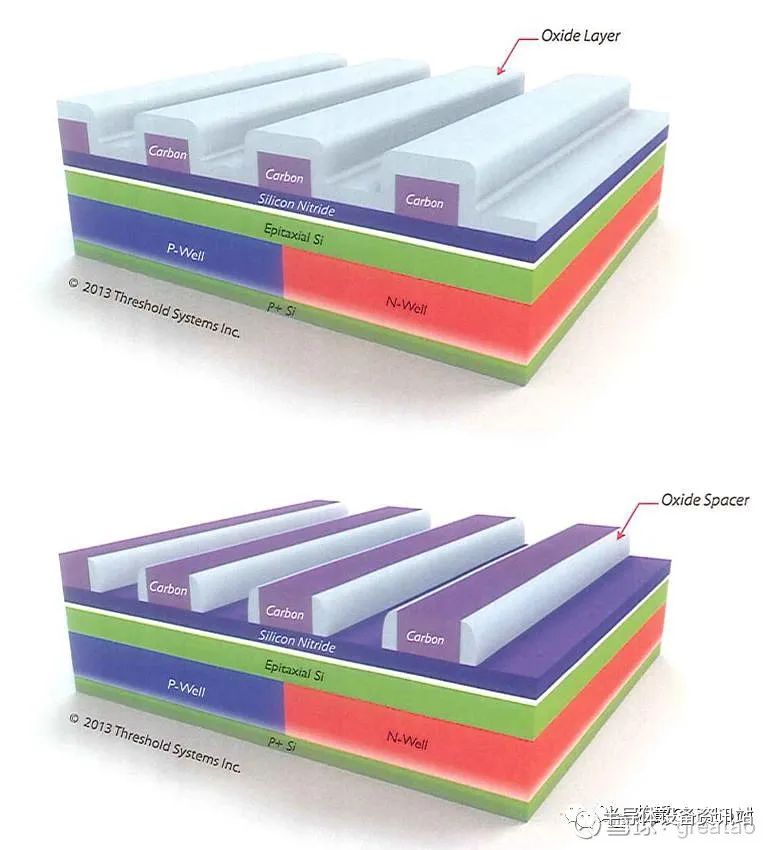

8. Mandrel Removal Nitride Etch

然后通过etch 吃掉 Amorphous Carbon Mandrel层

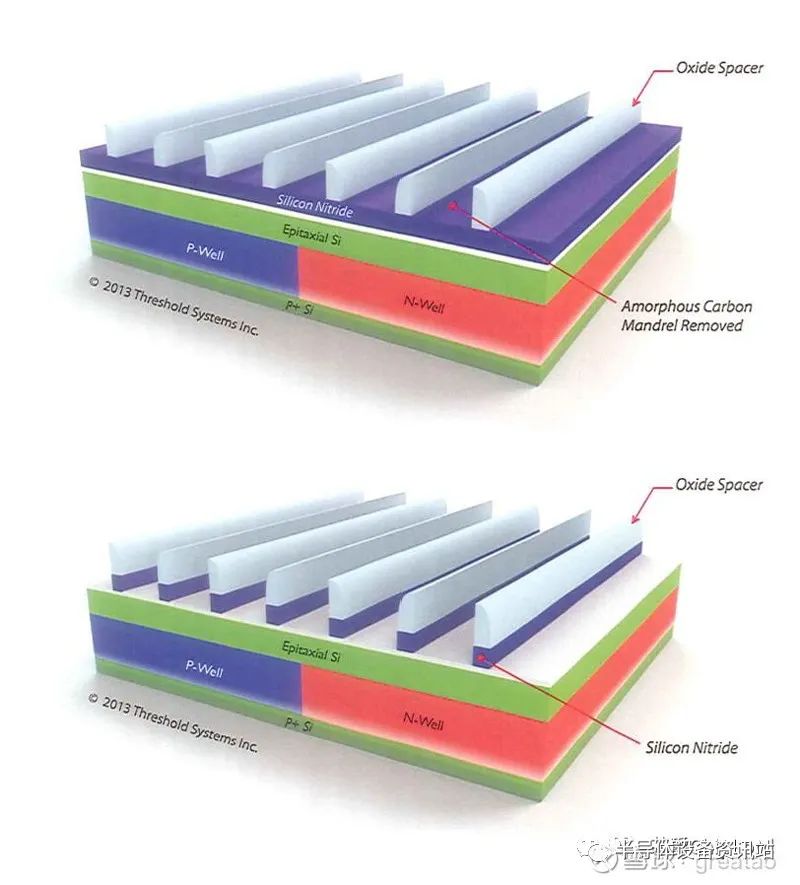

9. Fin Etch Trench Liner Growth

Oxide Spacer和Nitride作为Hard Mask继续向下etch

10. Trench Liner Removal Fin Removal Photo

然后通过etch去除oxide trench liner

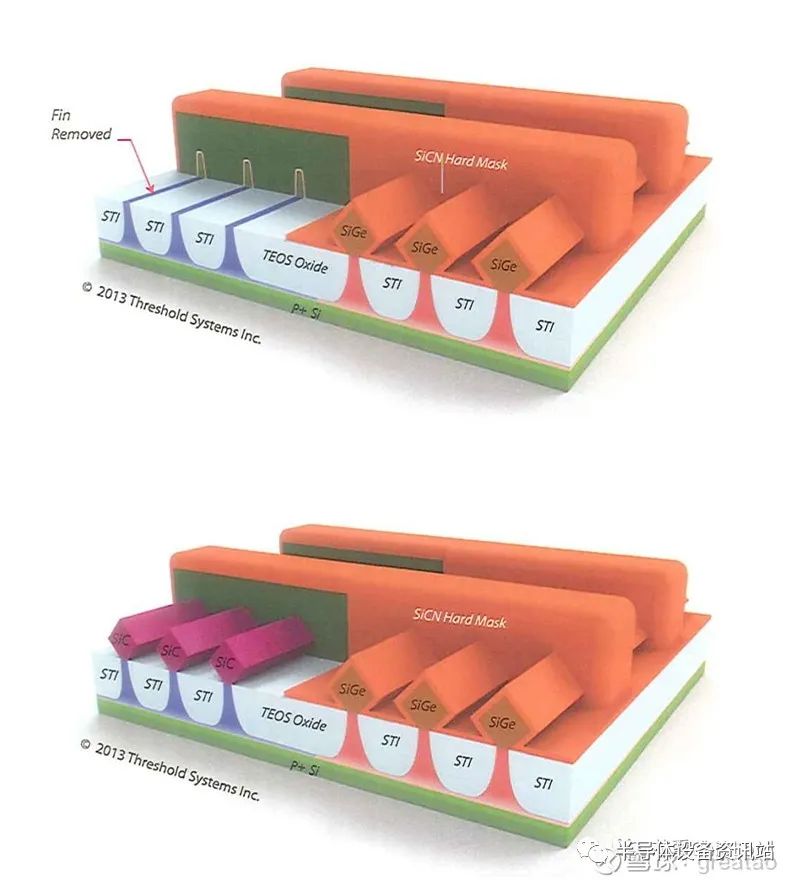

11. Fin Removal

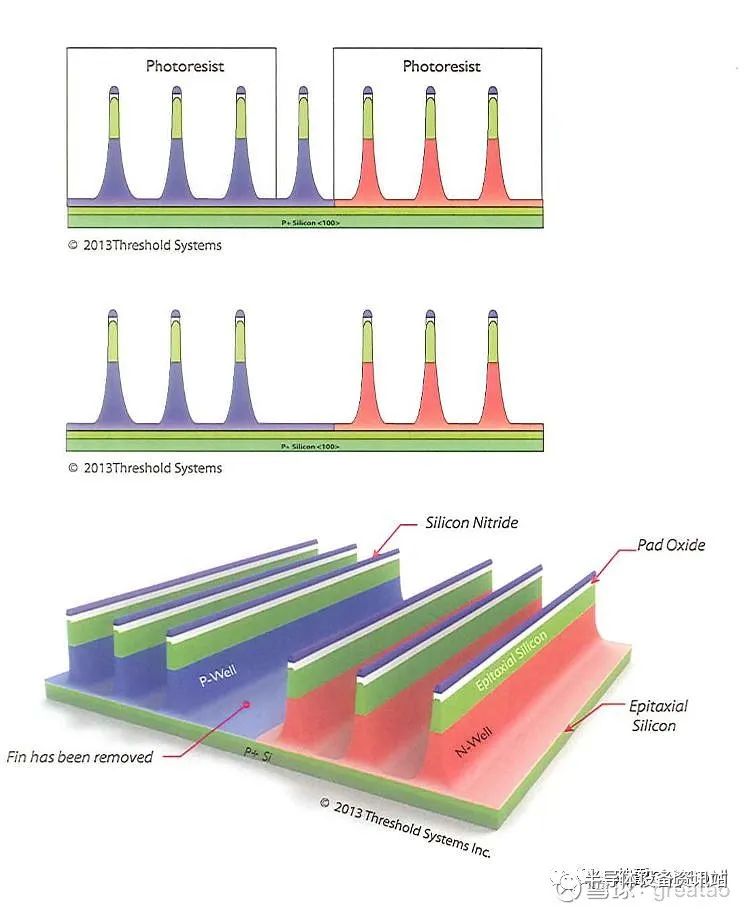

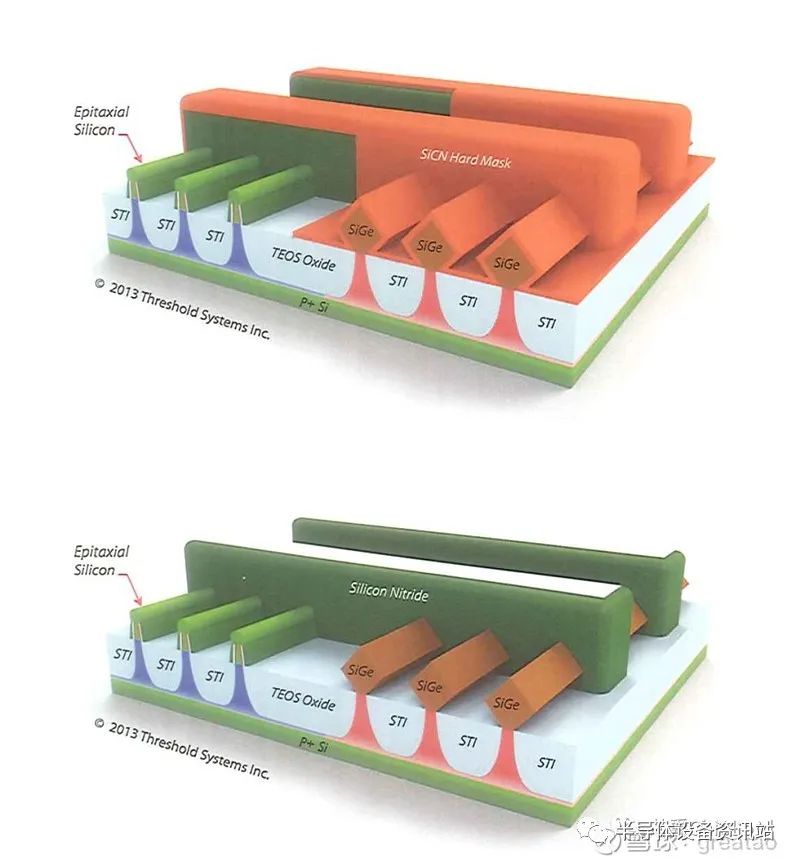

多余的Fin移除前后对比图如下

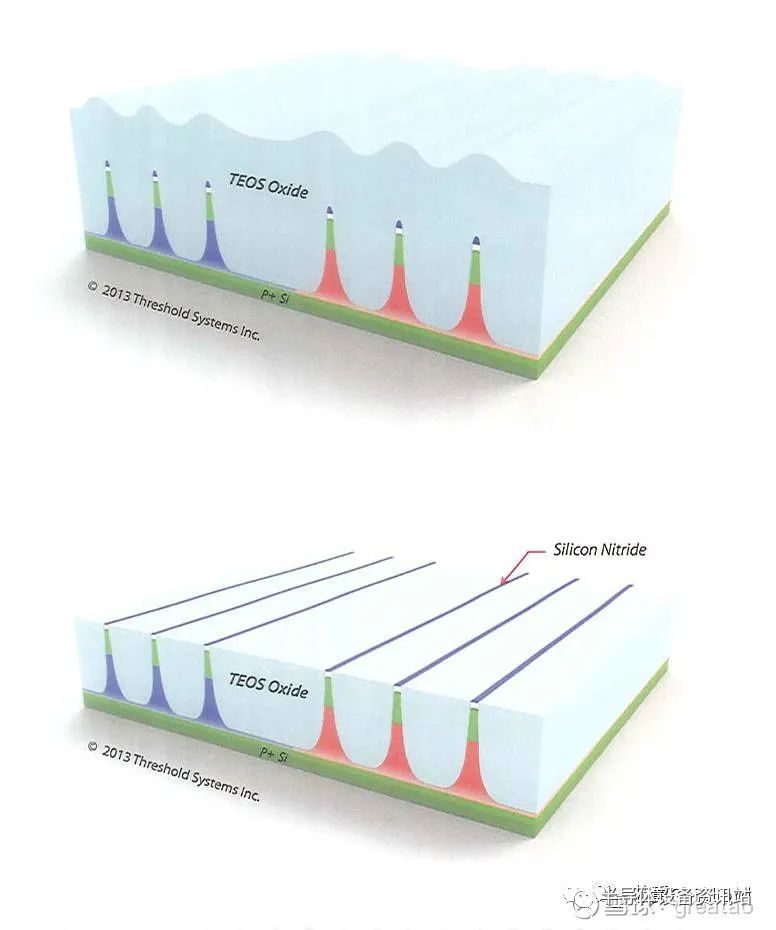

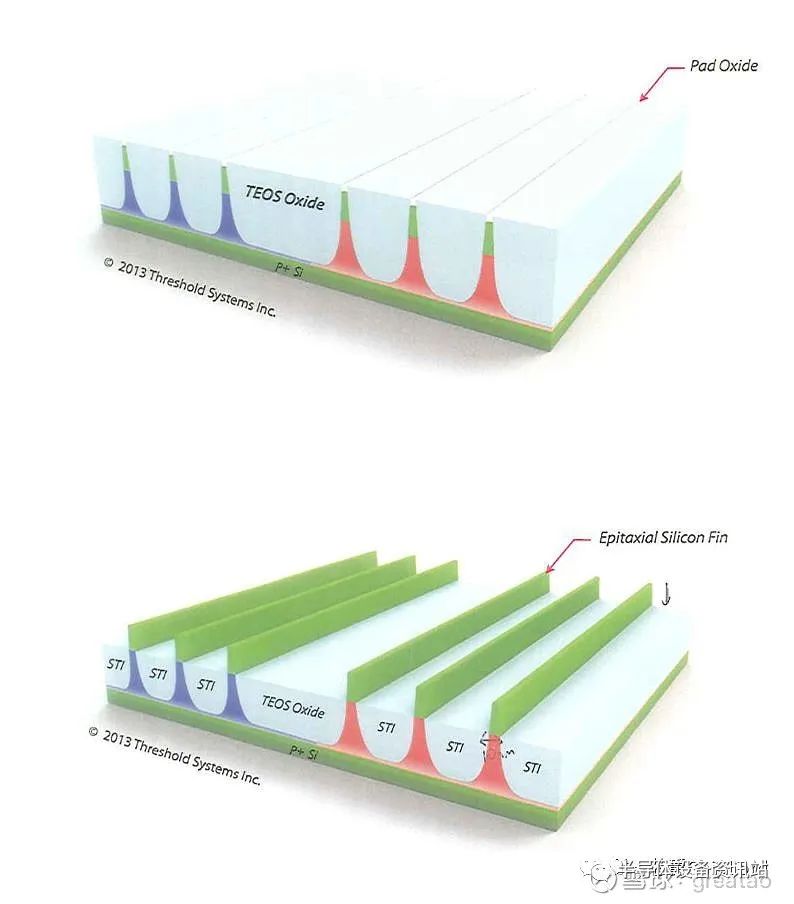

12. TEOS deposition

然后通过CVD填充一层厚厚的TEOS

13. Nitride Removal TEOS Etch-Back

通过热磷酸溶液去除多余的silicon nitride

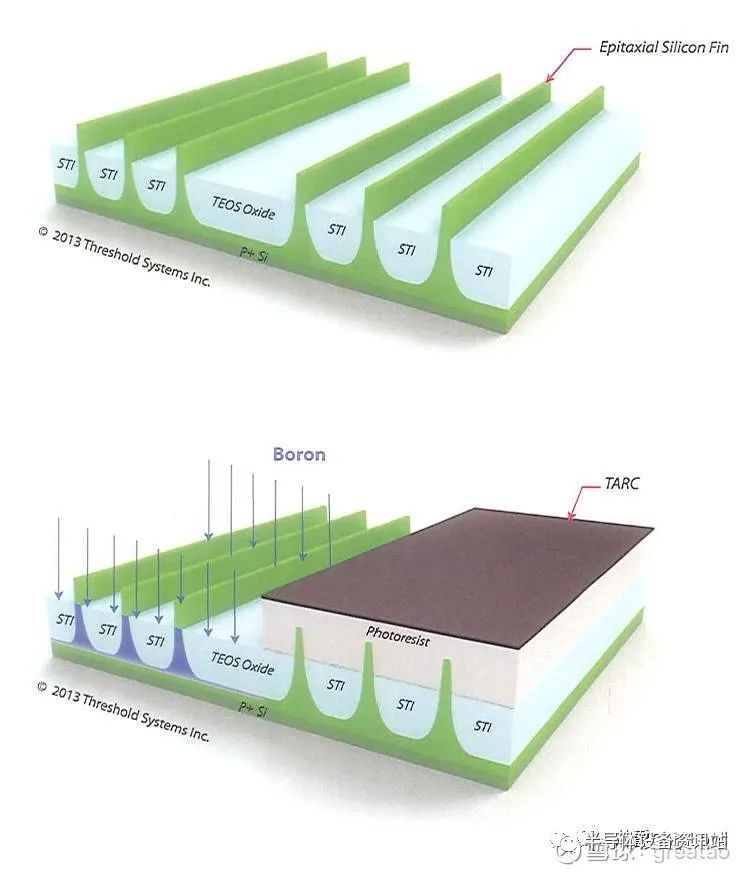

14. AlternateWell Implant Methodology

前面第2步已经通过离子注入定义了P/N-Well

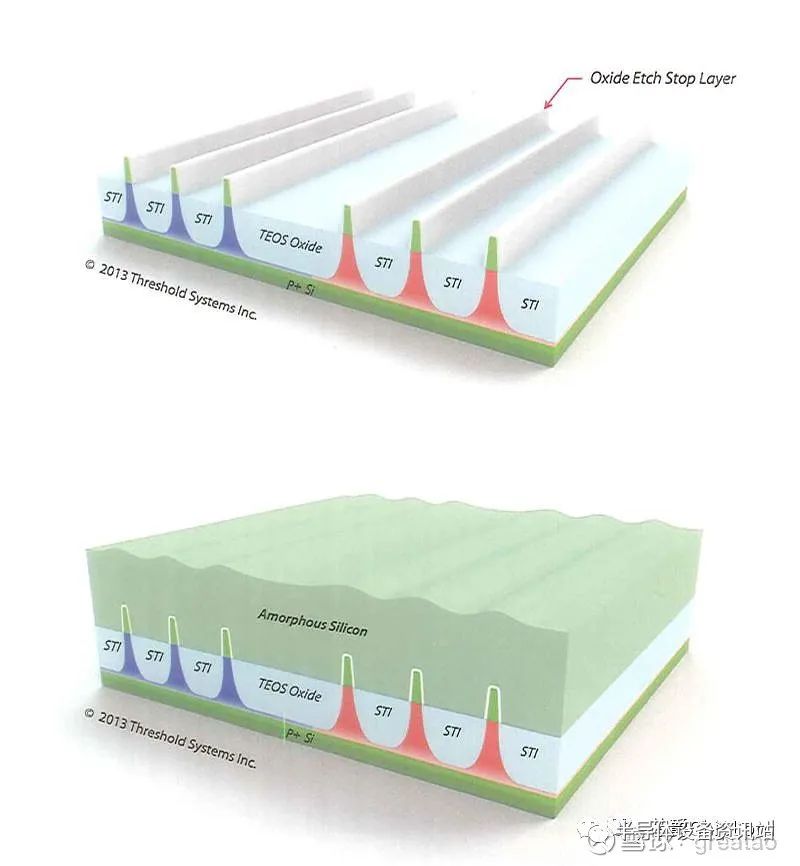

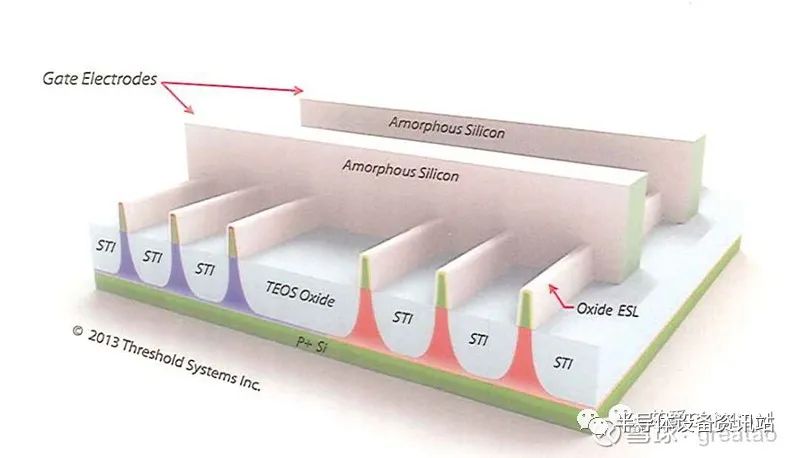

15. ESL Growth Amorphous Silicon Deposition

然后在Fin上通过热氧化生成一层oxide作为 etch stop layer(ESL)

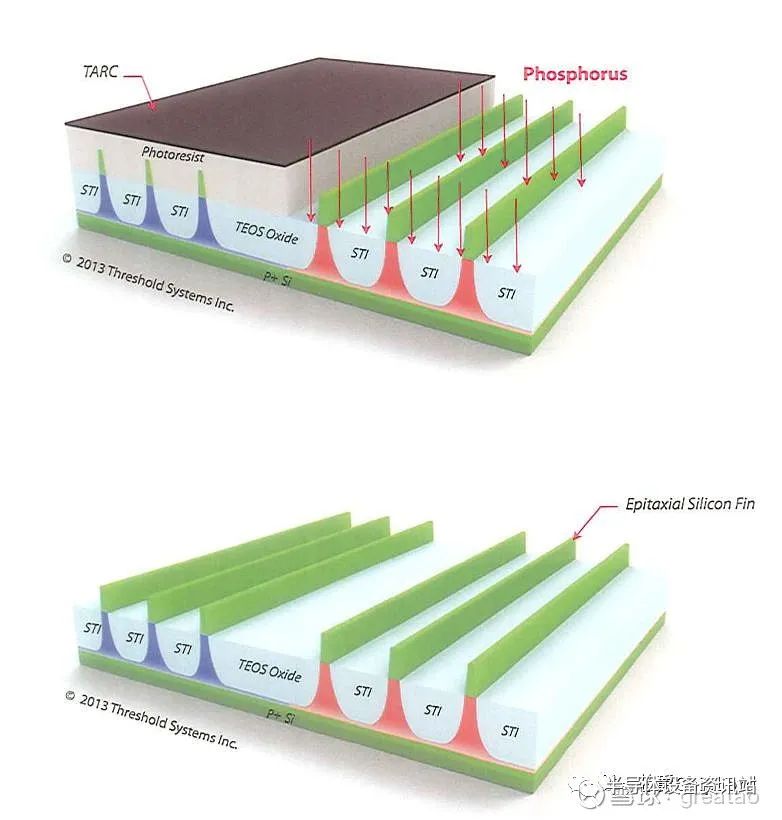

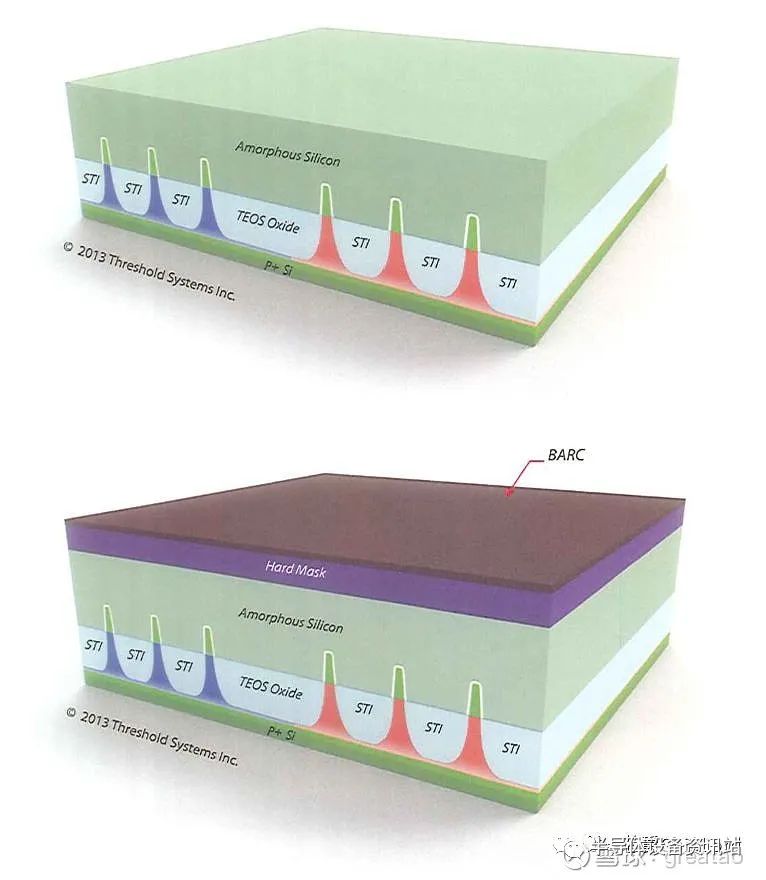

16. Amorphous Silicon Depositon Patterning

然后CMP磨平 Amorphous Silicon

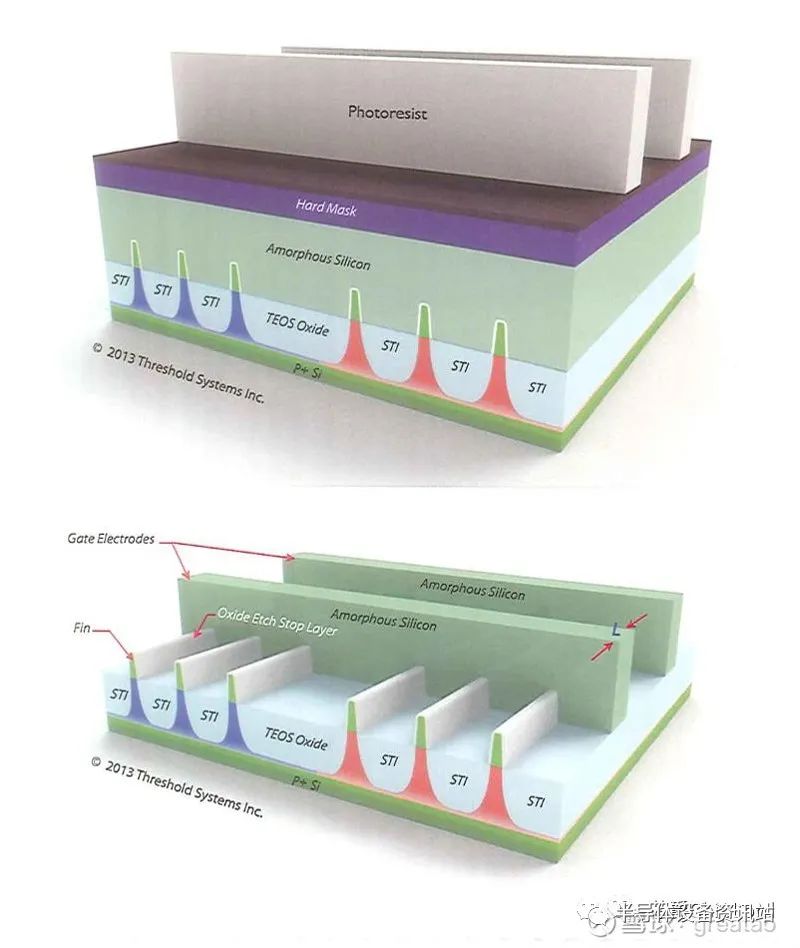

17. Hard Mask Patterning and Etch

曝光

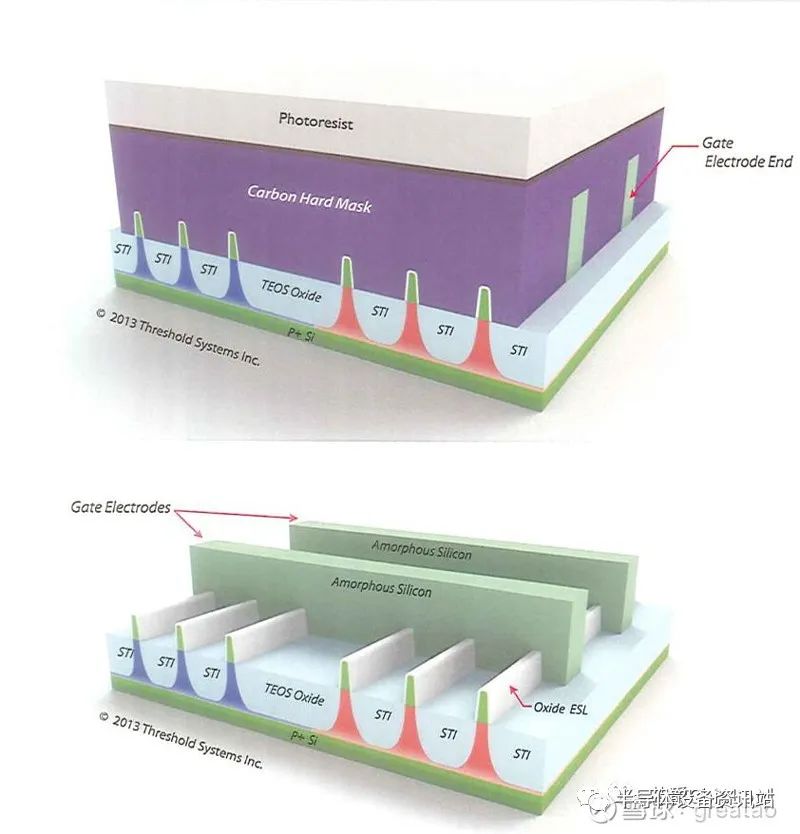

18. 2nd Gate Electrode Patterning

这一步主要是把右边多余的dummyGate去掉

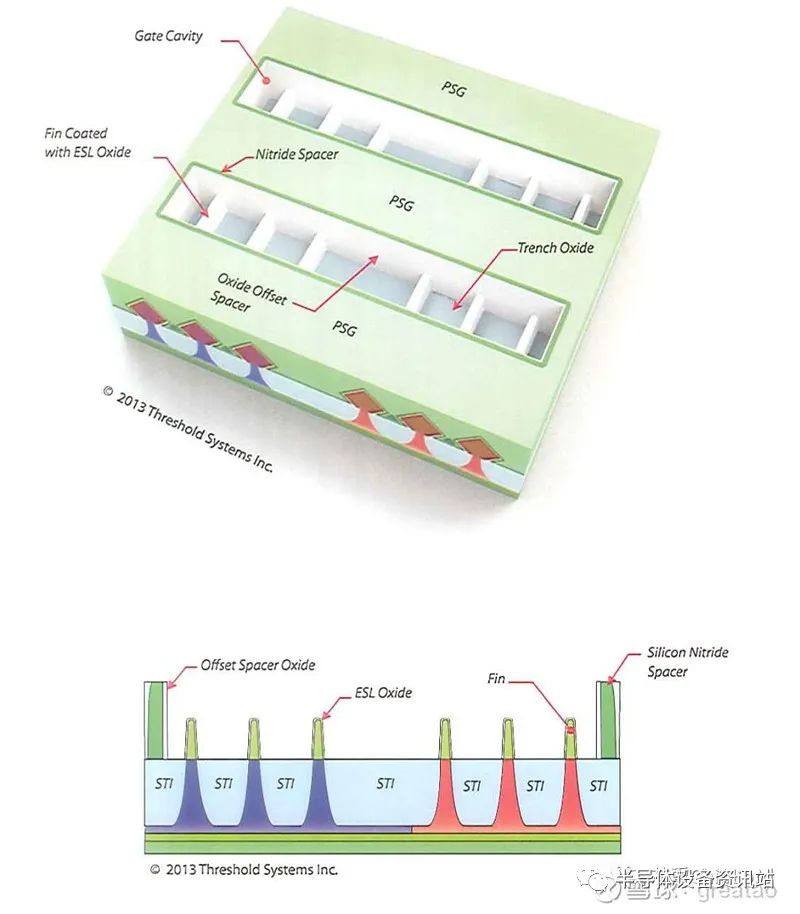

19. Offset Spacer Deposition

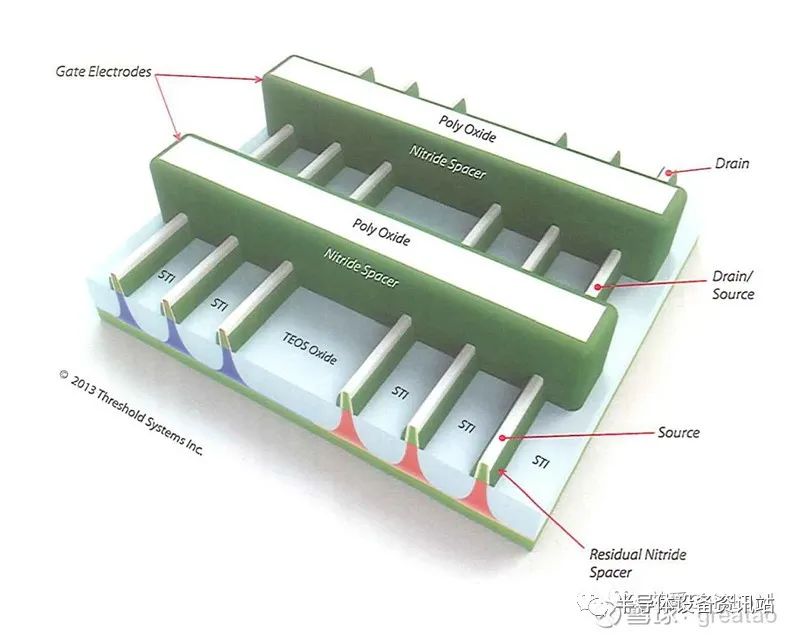

接下来先通过热氧化生成一层poly oxide

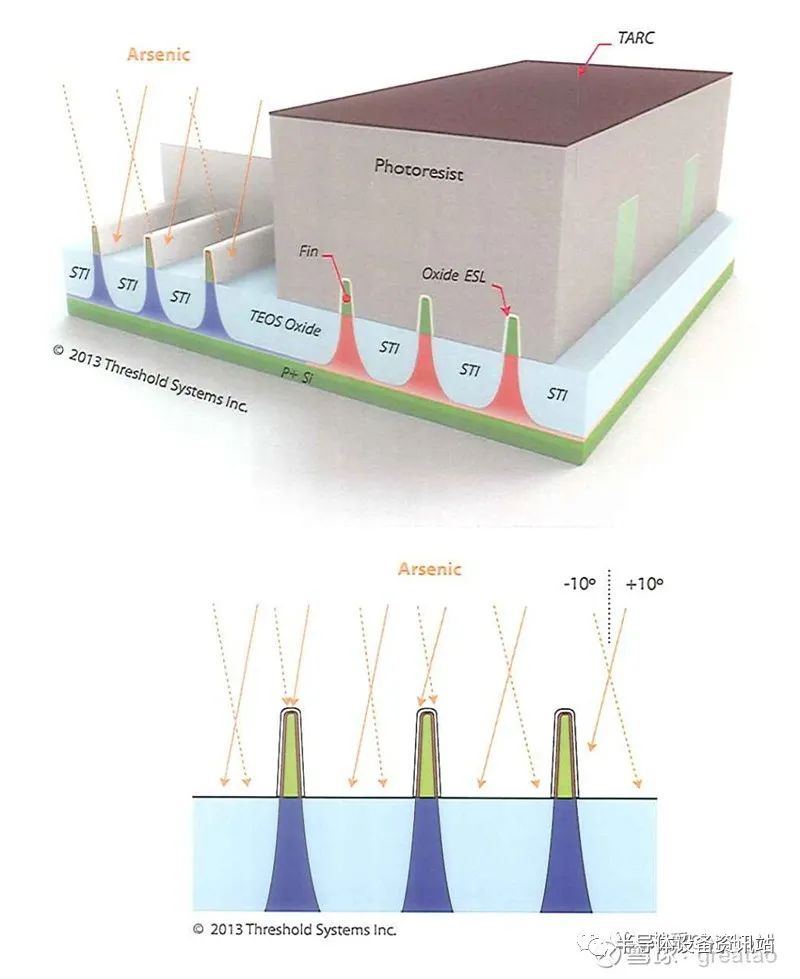

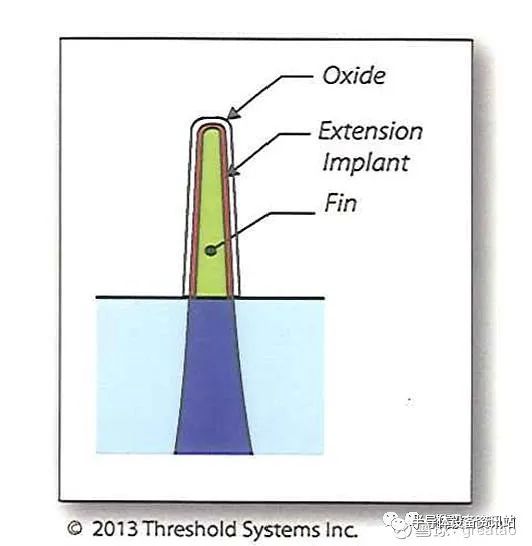

20.NMOSExtension Implant

铺上PR和BARC

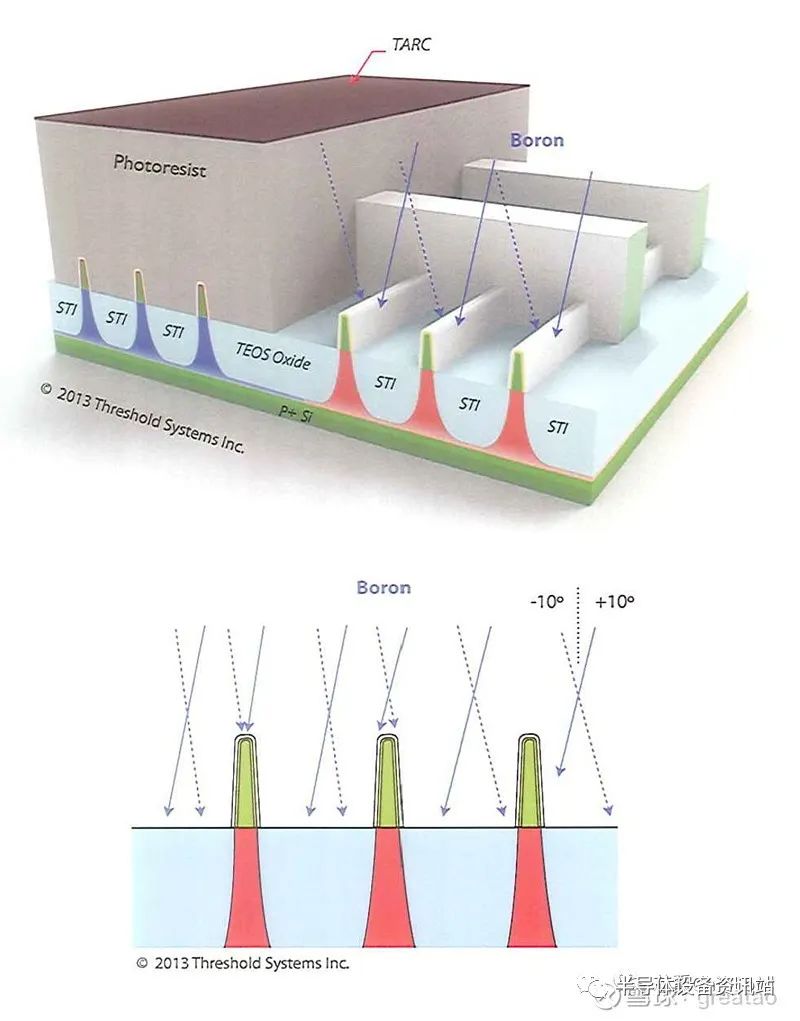

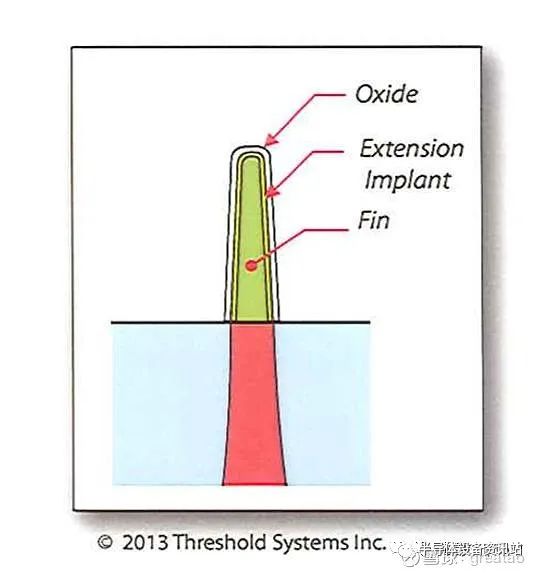

21. PMOS Extension Implant

同理在PMOS区域进行硼离子注入

22. Extension Anneal

由于离子注入后晶格有损失

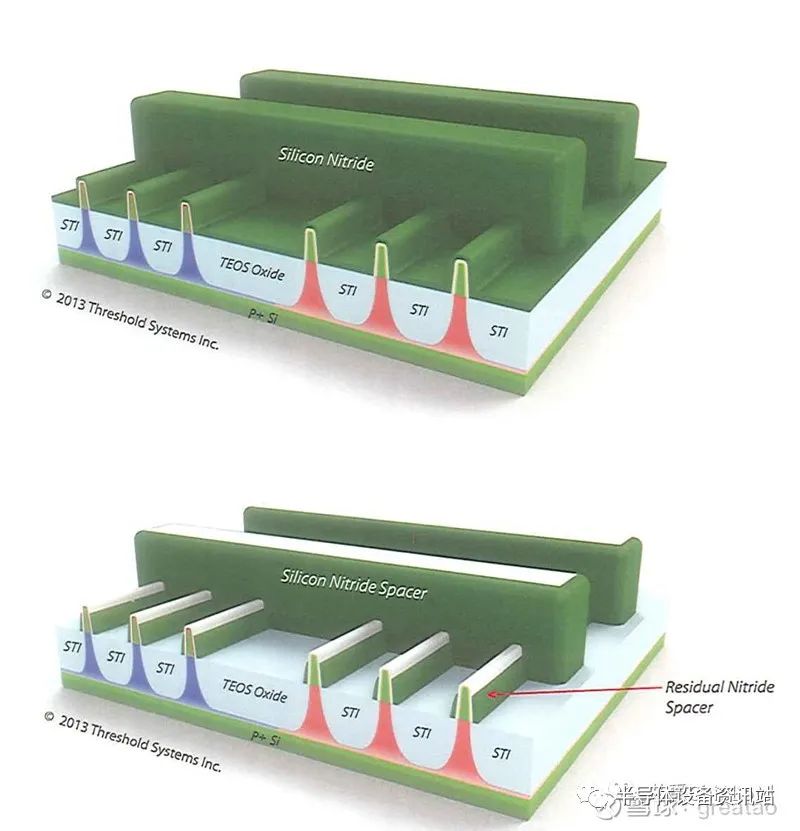

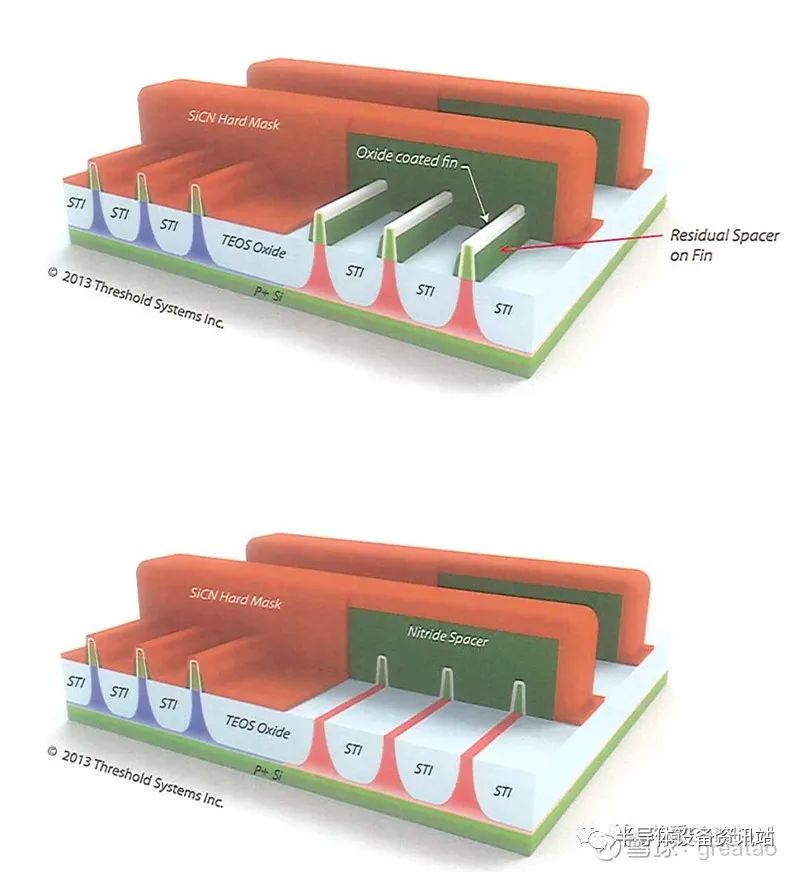

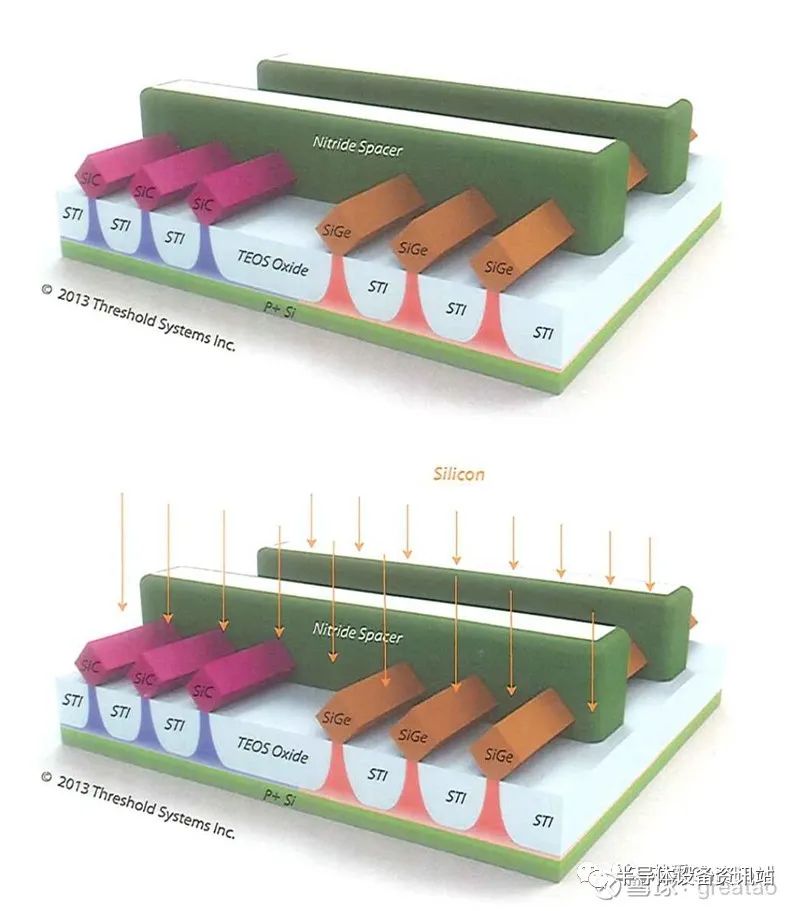

23. Nitride Spacer Deposition Etch

接下来deposit一层silicon Nitride

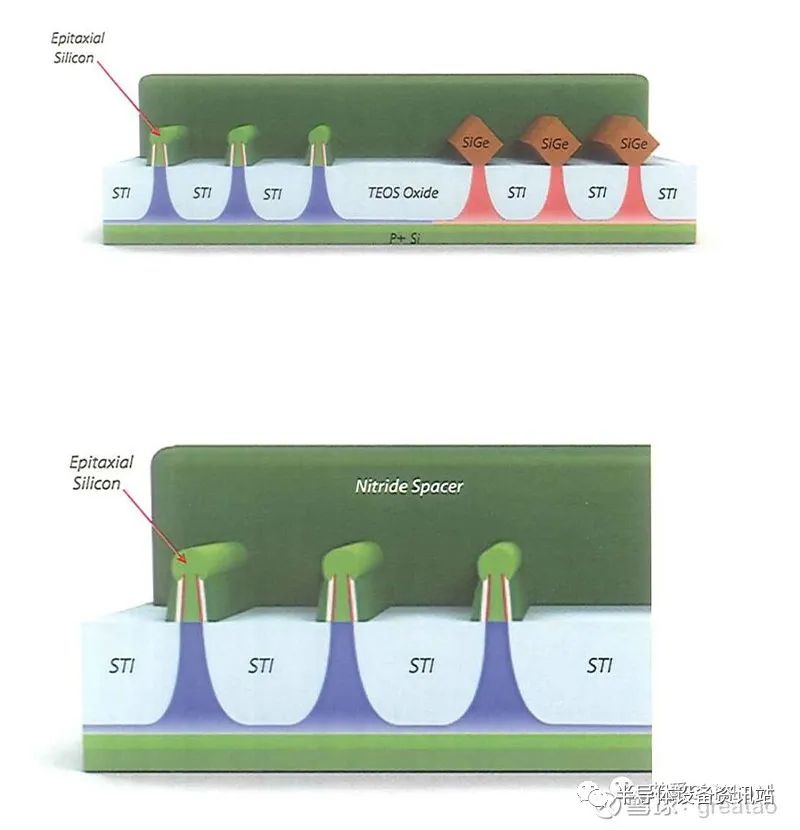

24.Nitride Spacer Morphology

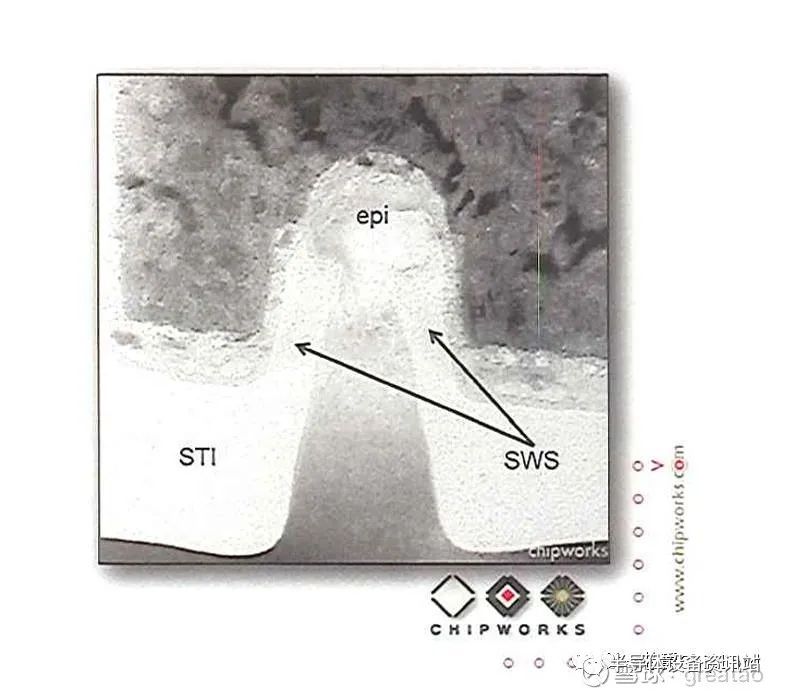

Nitride Spacer形成后

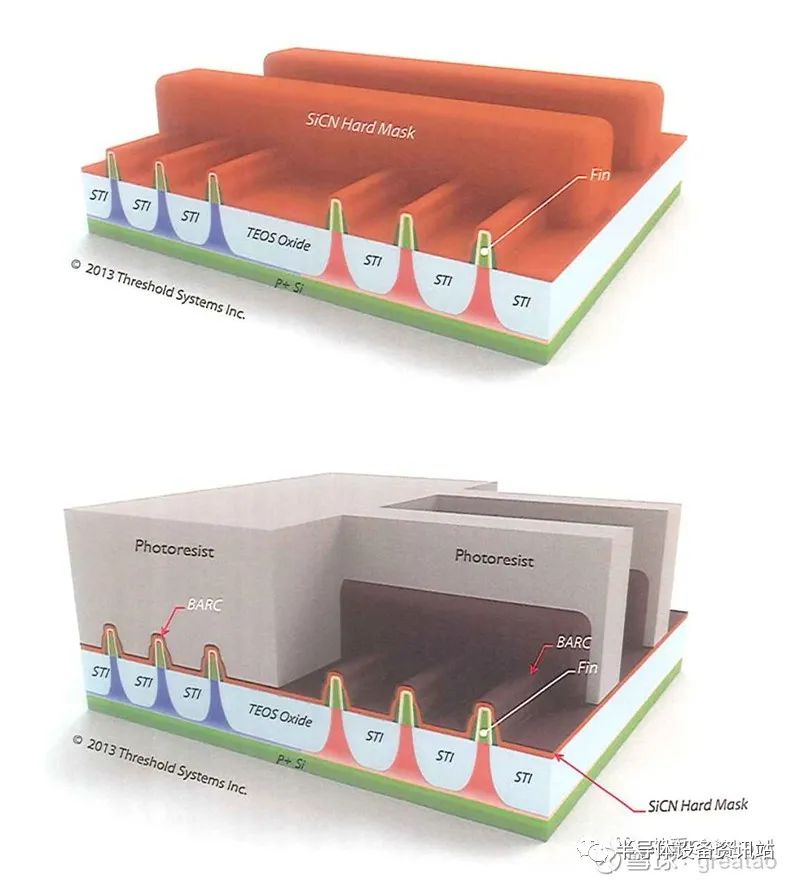

25. Hard MaskDepositionPatterning

然后deposit一层SiCN做为Hard Mask

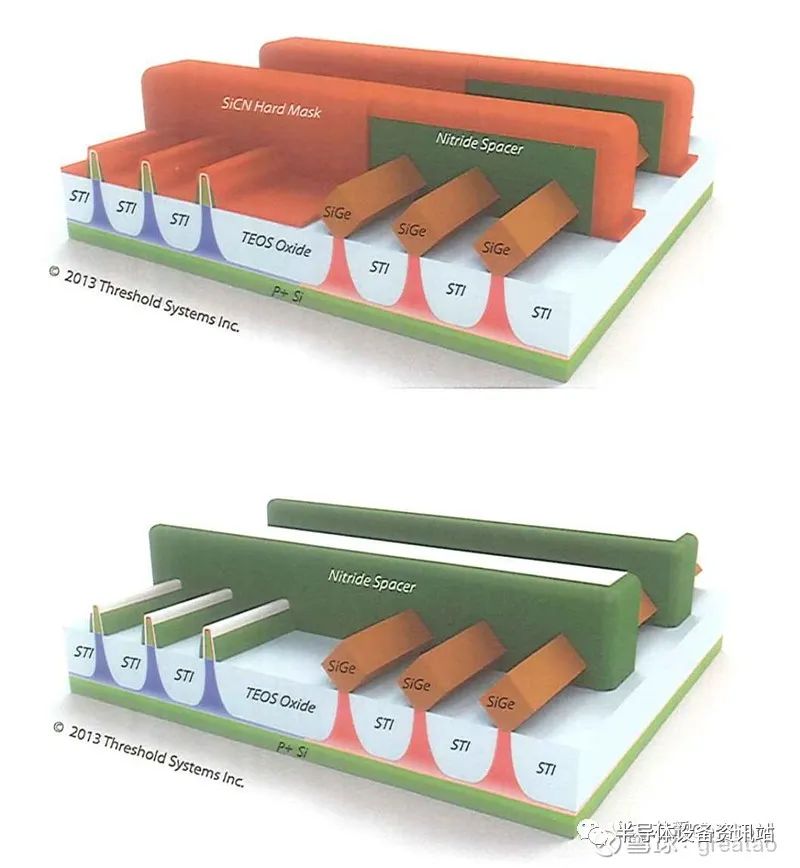

26. Hard MaskEtch PMOS Fin Removal

SiCN作为Hard Mask

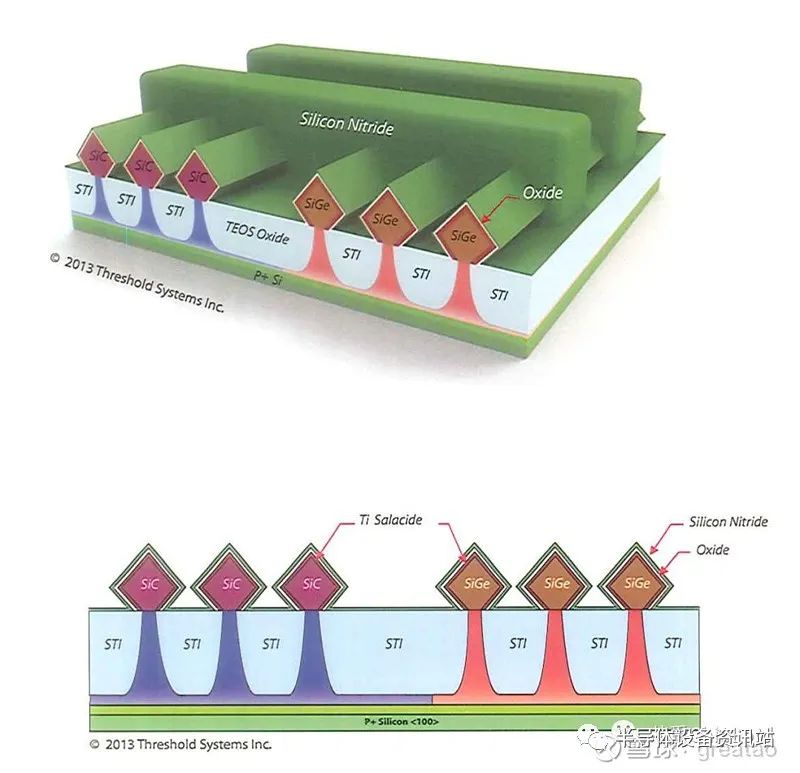

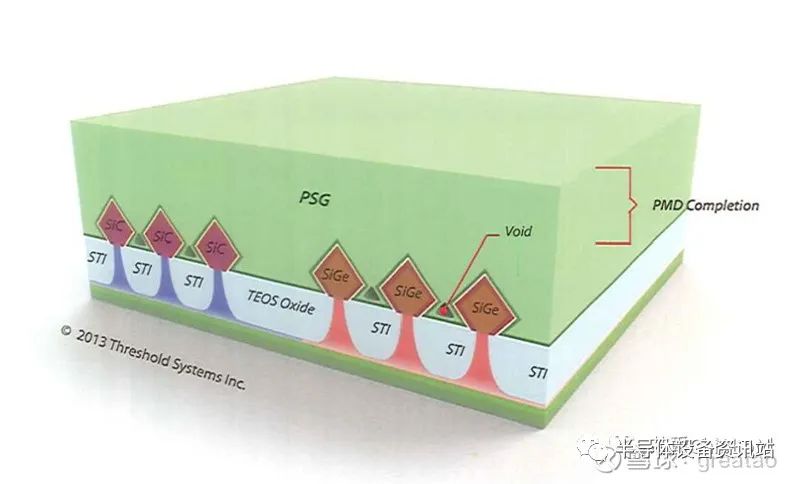

27. SiGe Deposition HardMask Removal

接着进行SiGe外延生长

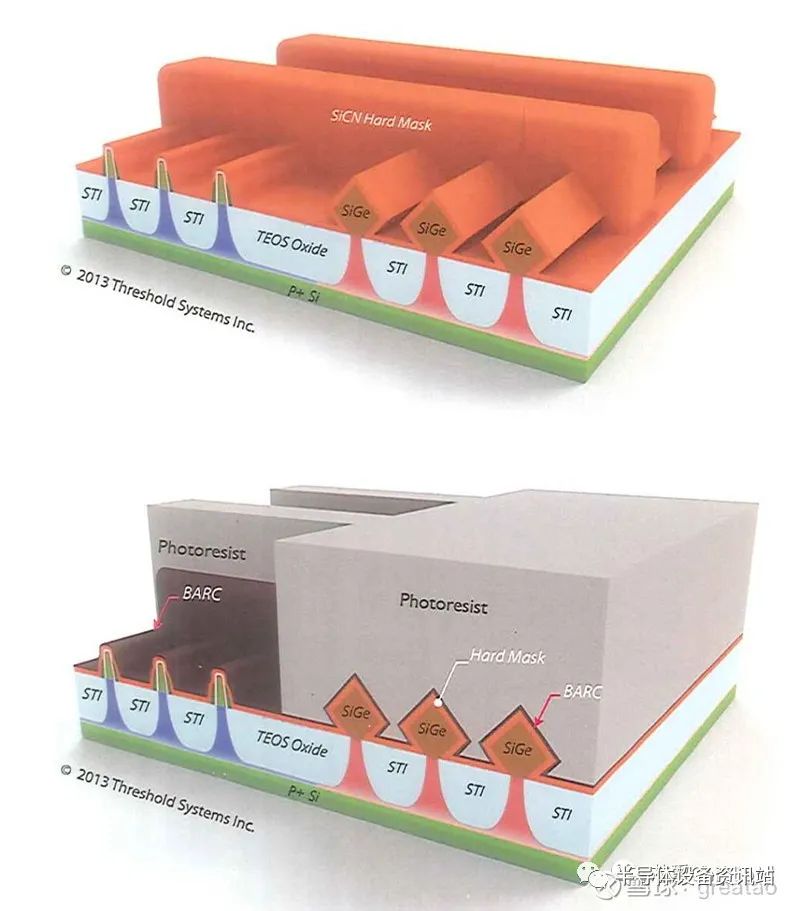

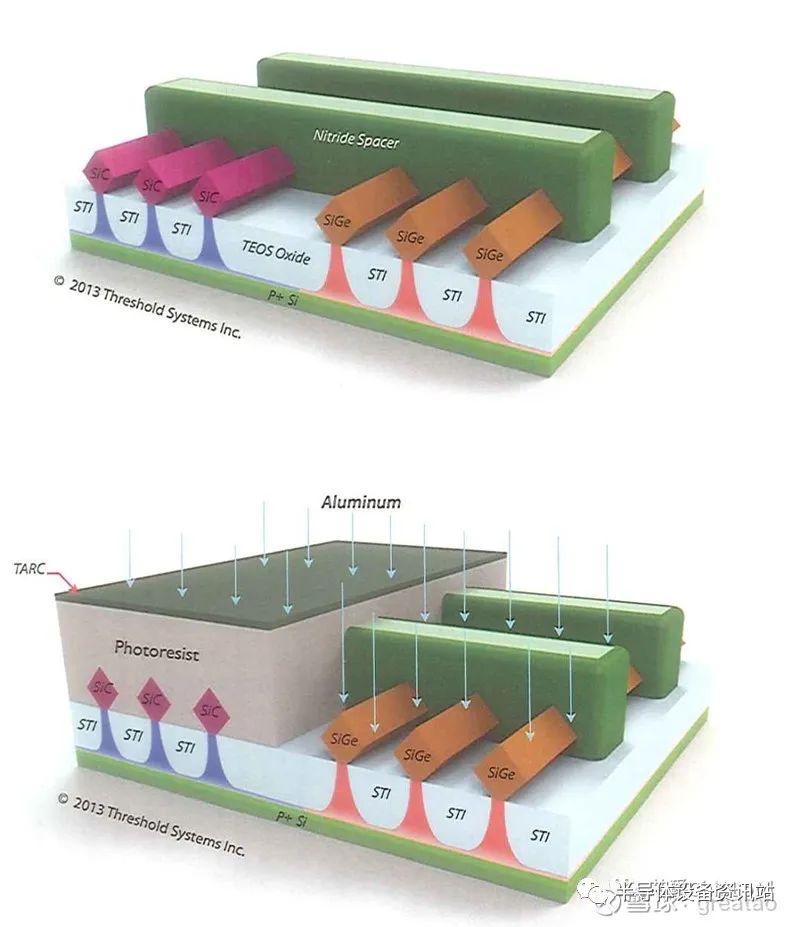

28. Hard Mask Deposition Patterning

同理

**NMOS区域有两种选择方案

29. Hard Mask Etch Oxide Strip

NMOS 区域进行Hard Mask etch

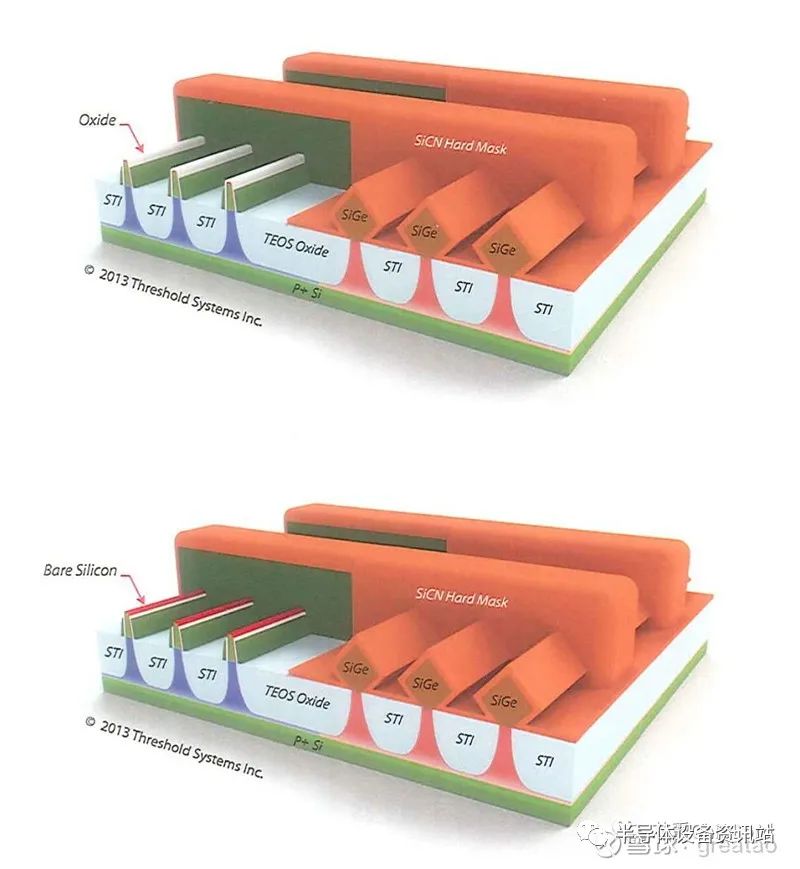

30.#1 Epitaxial Si Growth Hard Mask Strip

然后在Fin上外延生长一层Si

31. #2 NMOSFin Removal SiC Epitaxial Deposition

将NMOS Fin全部移除

32. SiCN Hard Mask Strip Silicon Implant

移除SiCN Hard Mask层

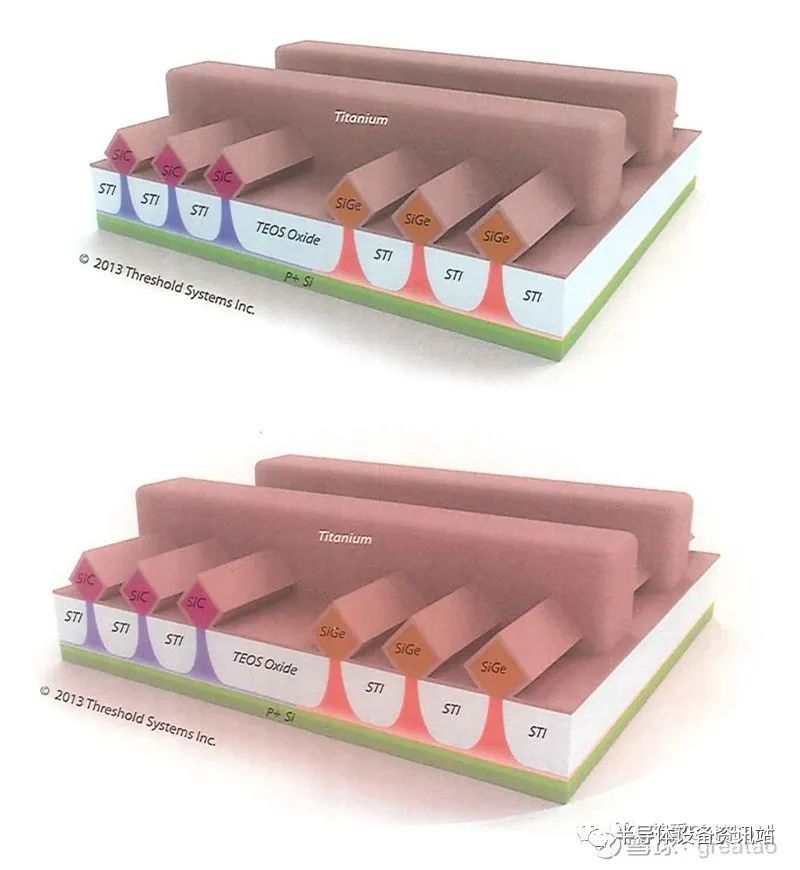

33. Oxide Strip Al Salicide Implant

用HF移除Gate, Source, Drain上面的oxide

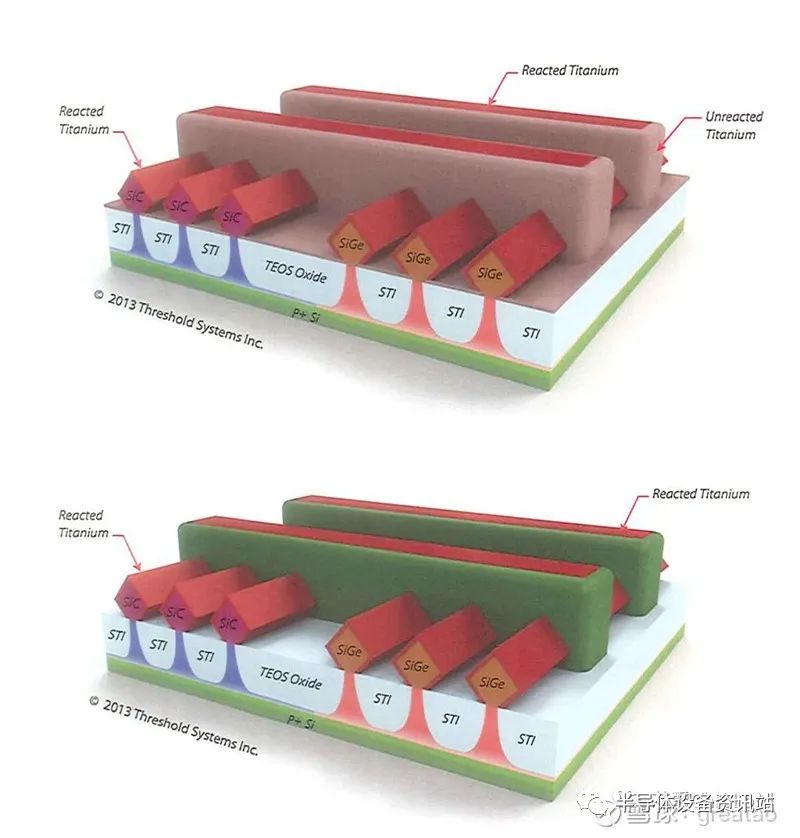

34.ColdTitanium Deposition Anneal

然后通过PVD的方式在表面形成一层Titanium

35. Unreacted Titanium Strip

没有反应的Titanium位于spacer sidewall and STI上面

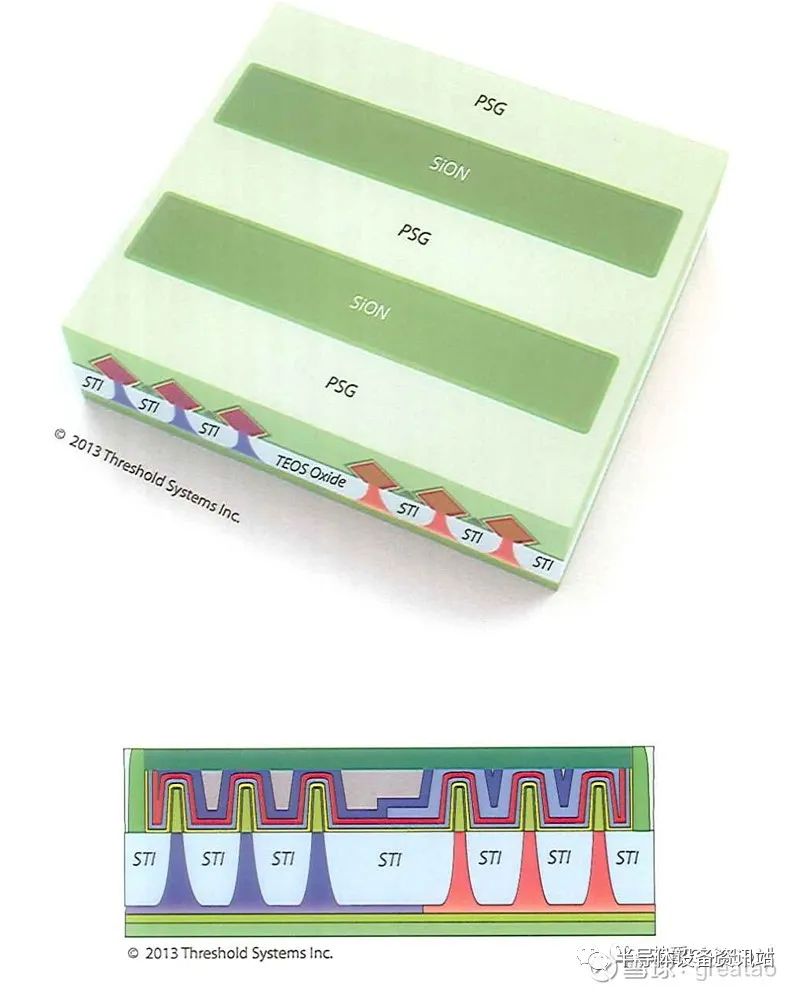

36. Oxide/Nitride Etch-Stop Laryer Deposition

wafer用P/SC1溶剂清洗

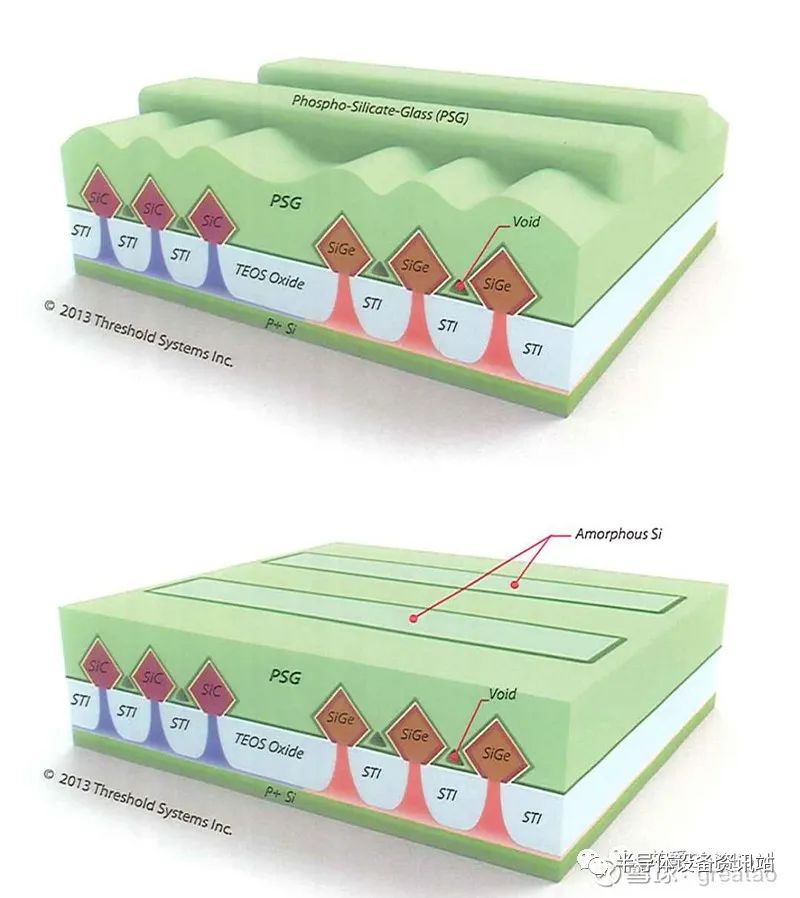

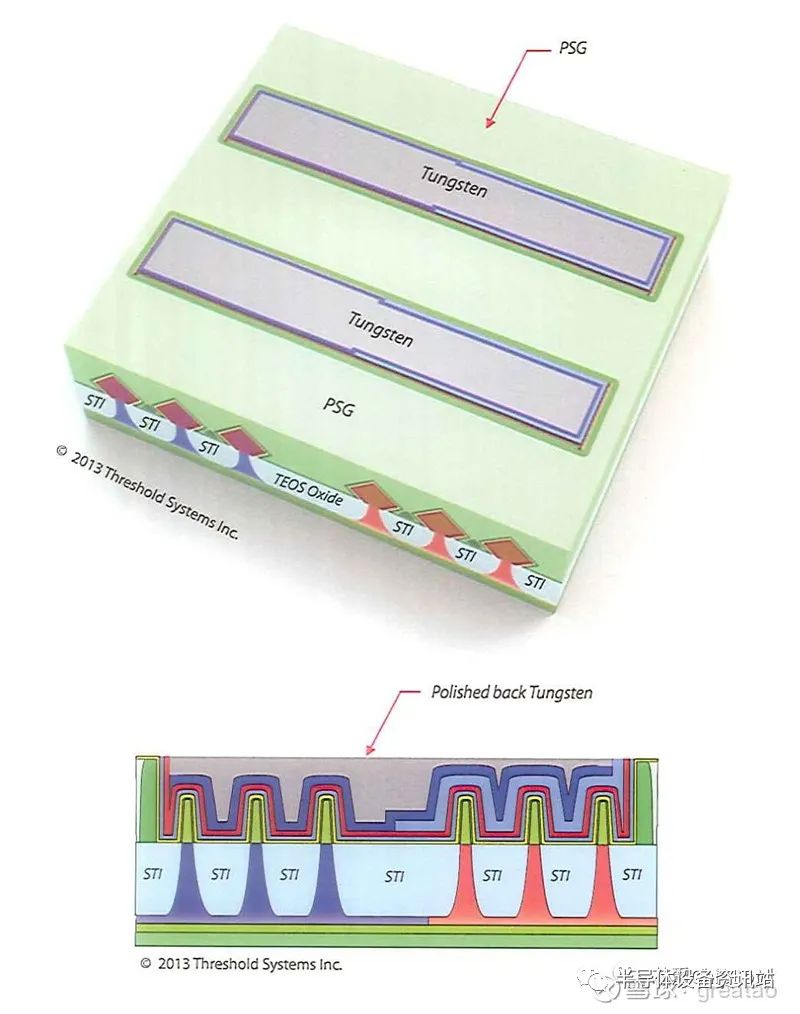

37. PMD Deposition and Polish-Back

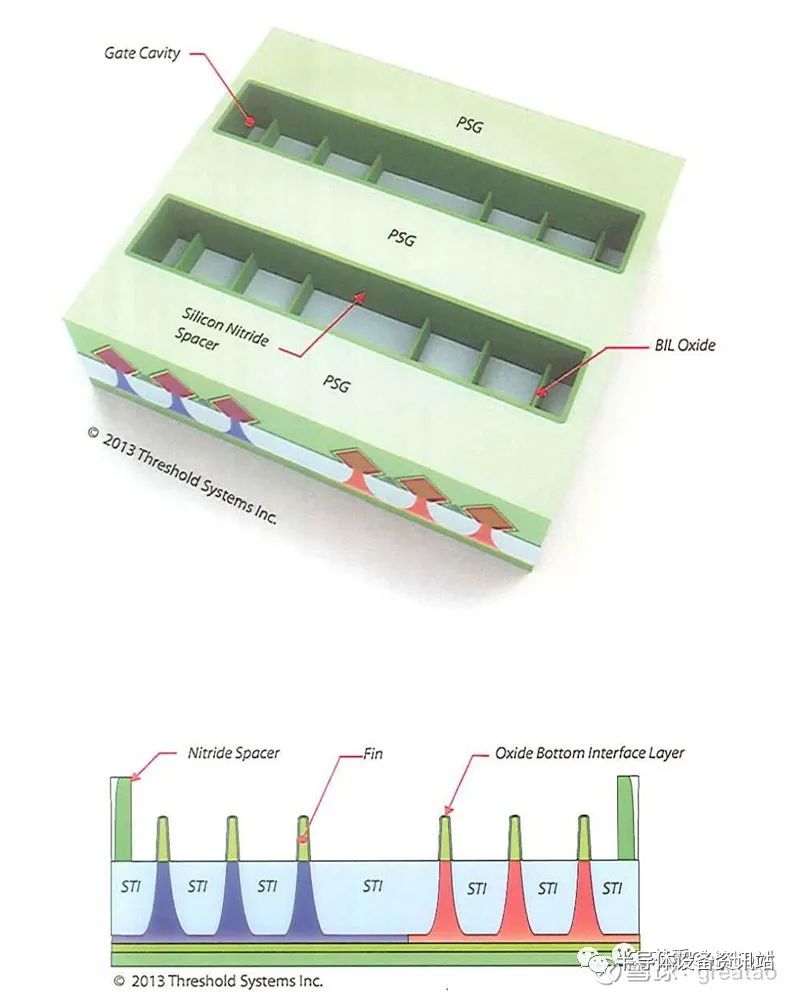

然后deposit一层厚厚的PSG(Phospho-Silicate Glass)

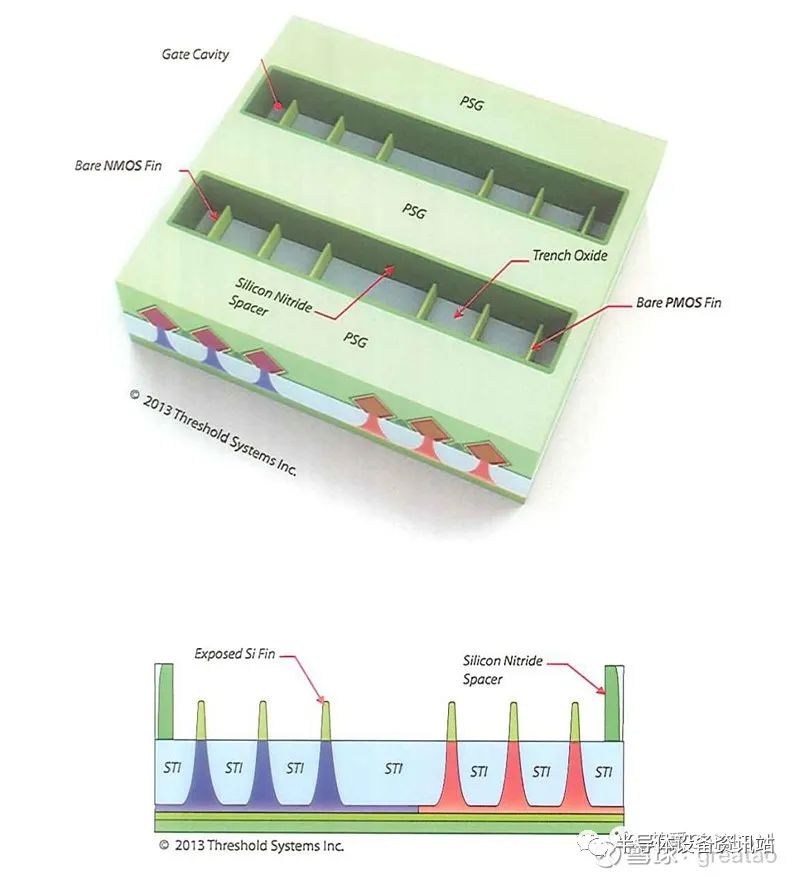

38. Polysiliocn Gate Removal

然后通过etch将dummy gate里的amorphous silicon移除

39. Oxide ESL Removal

然后通过etch移除Fin上面的oxide layer

40. Bottom Interface Oxide Layer Growth

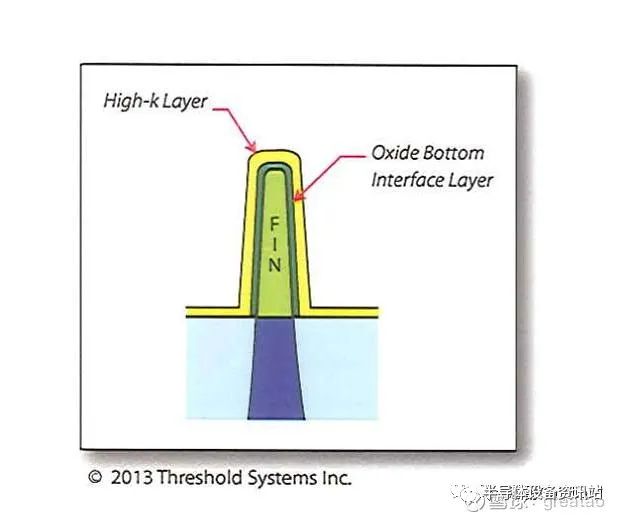

然后通过低温氧化反应在Fin表面形成一层oxide

中篇到此为止

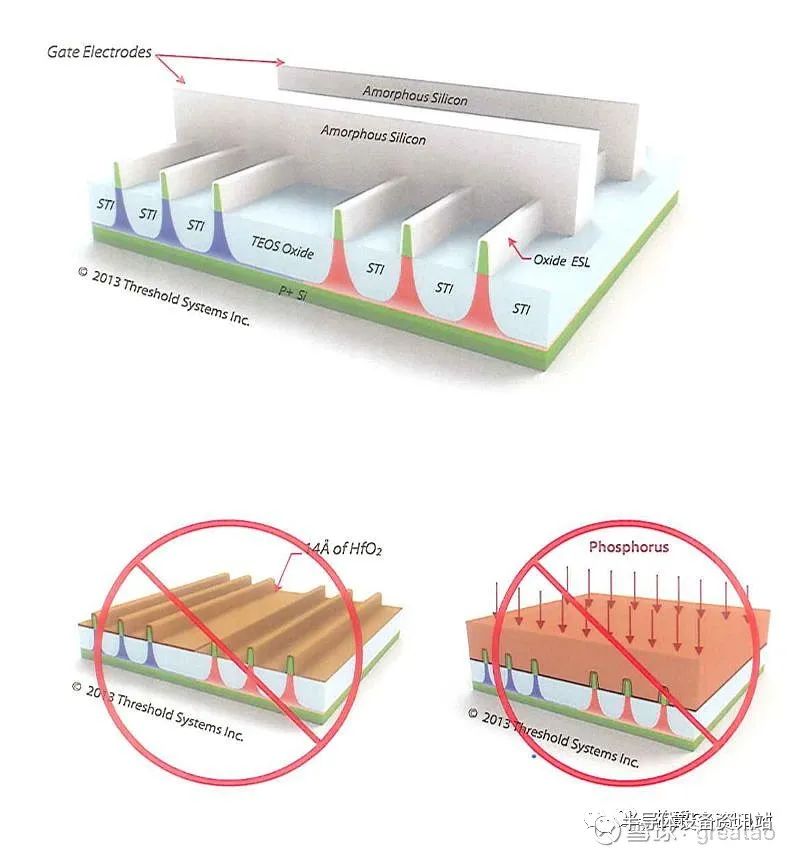

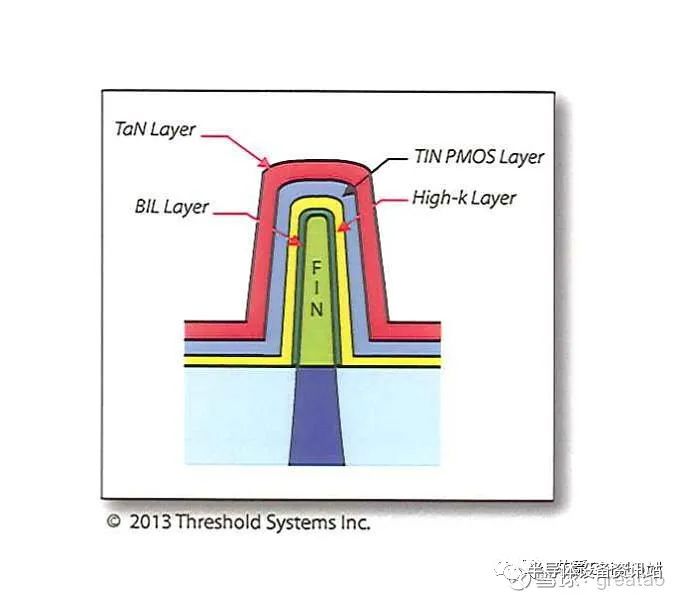

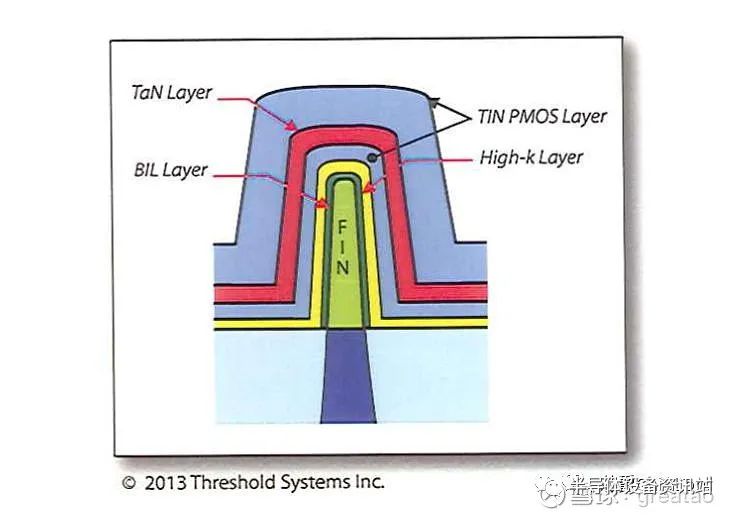

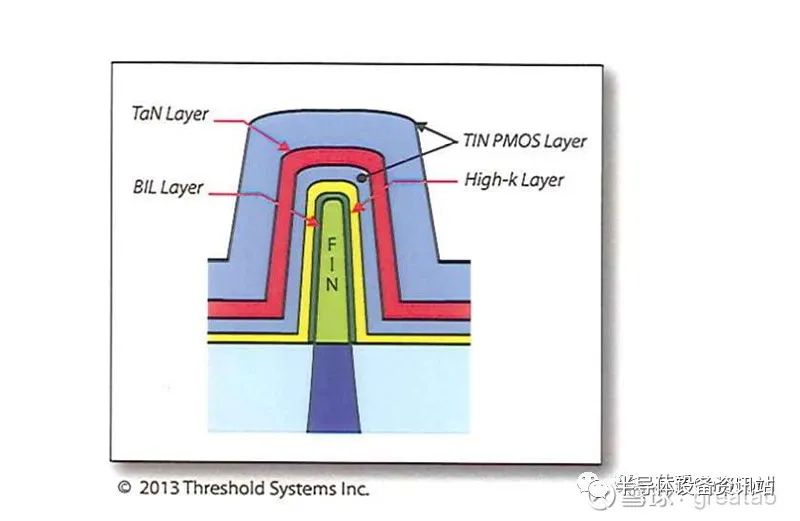

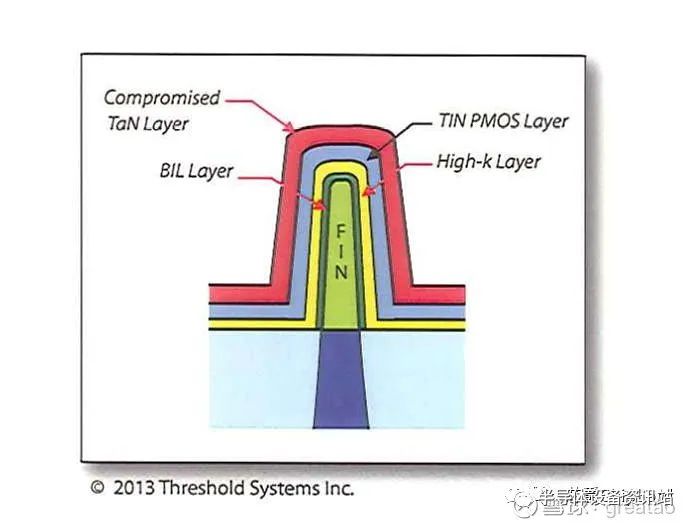

41.High-k Dielectric Deposition

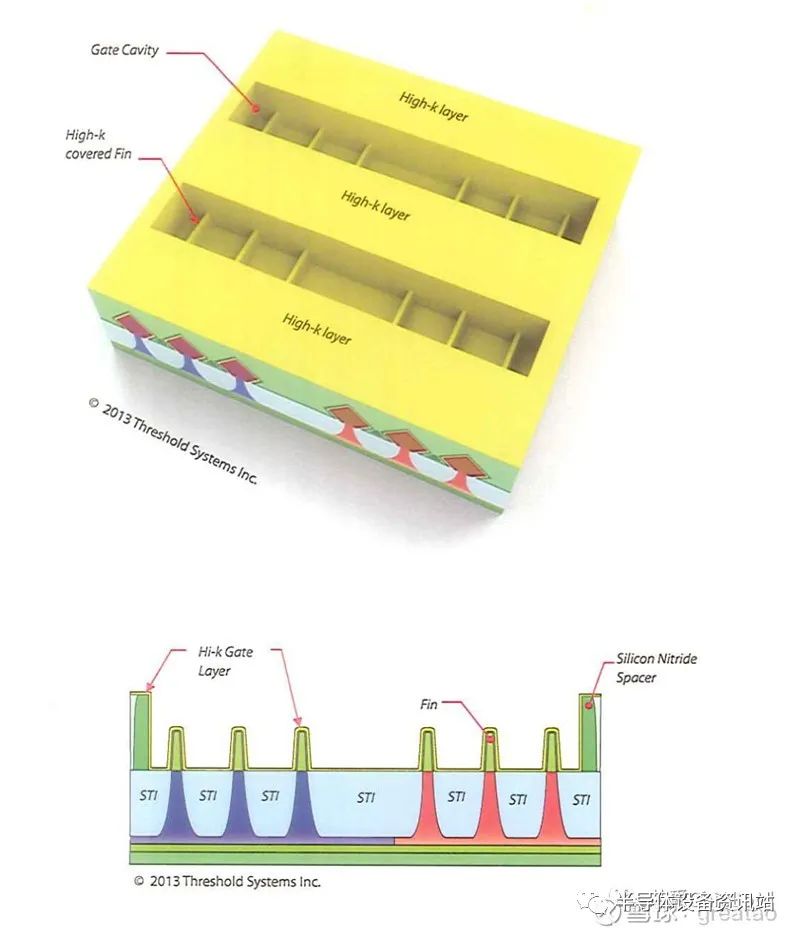

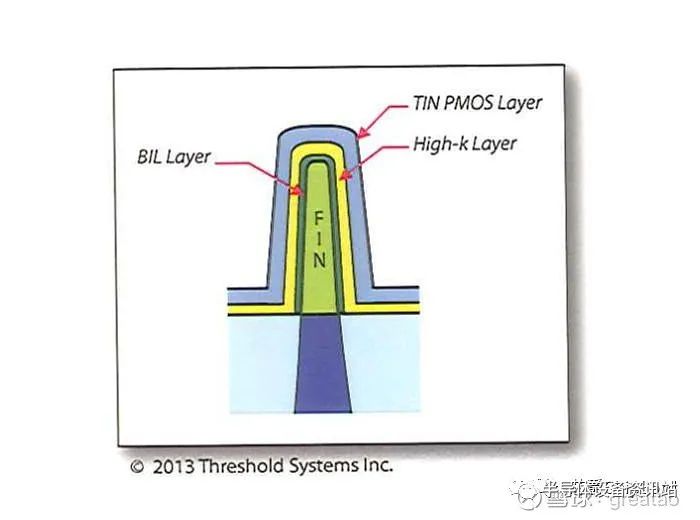

接下来ALD(Atomic Layer Deposition)工艺deposit一层High-k Hafnium oxide(氧化铪)做为电介质

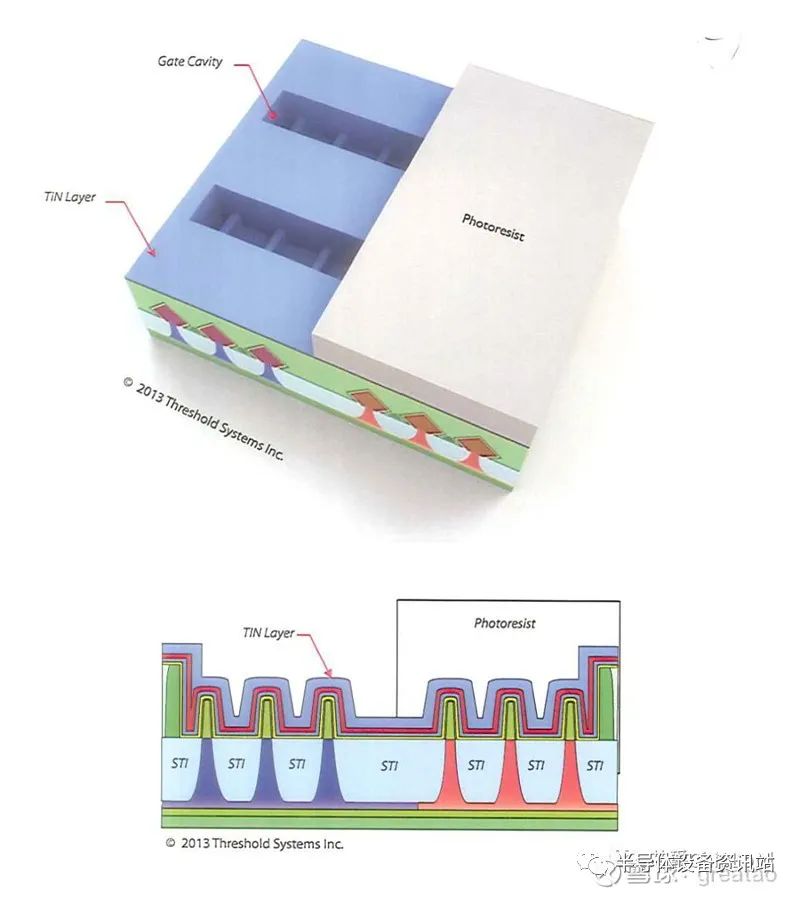

42. PMOS Metal(TiN) Deposition

ALD工艺在PMOS区域deposit一层功函数金属gate TiN

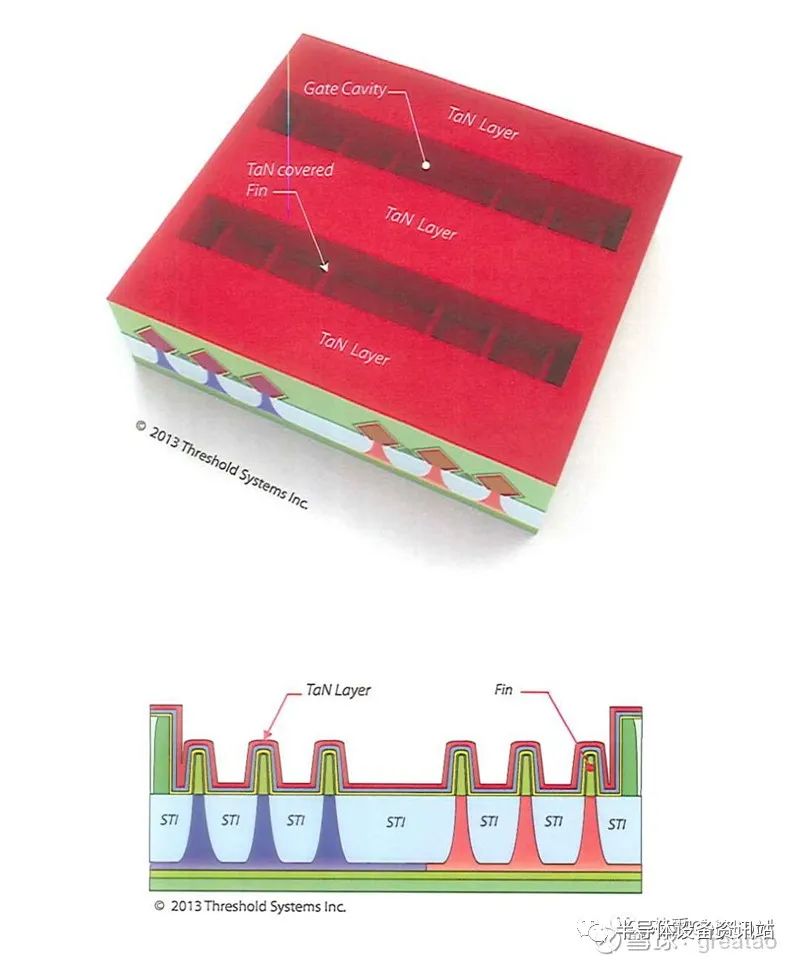

43. TaN Deposition

然后deposit一层TaN做为Etch Stop Layer

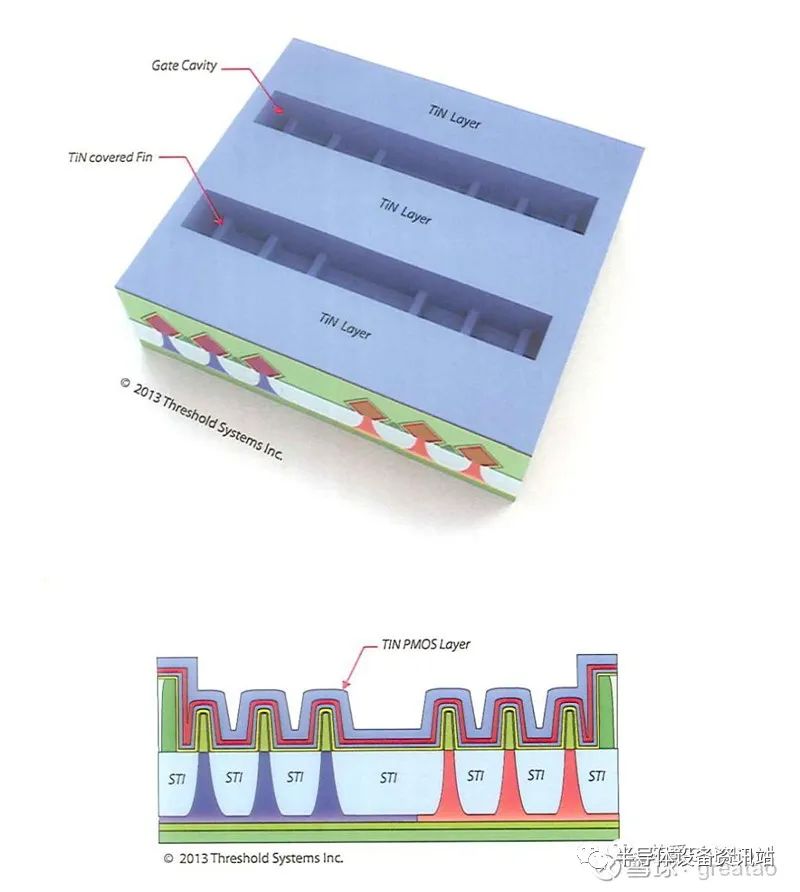

44.PMOS Metal(TiN)Deposition

同理

45. PMOS Metal Patterning

然后铺上一层PR

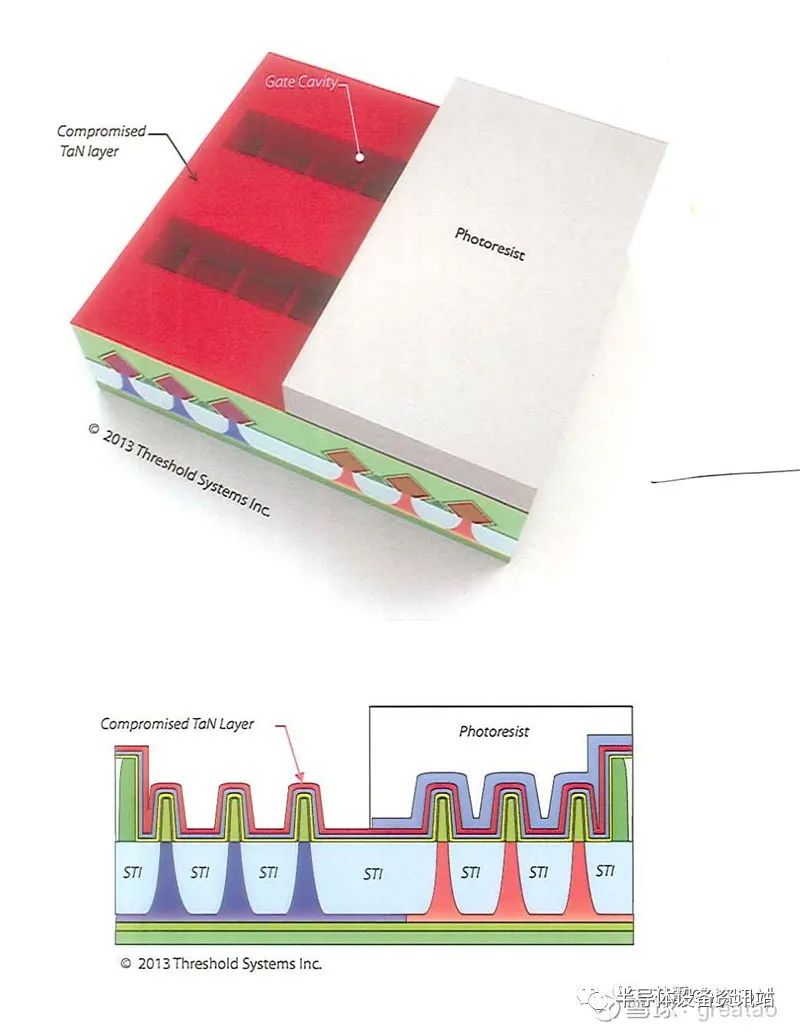

46. NMOS Metal Etch

NMOS区域的TiN Layer被etch完

47.Photoresist Strip

然后拔除PR

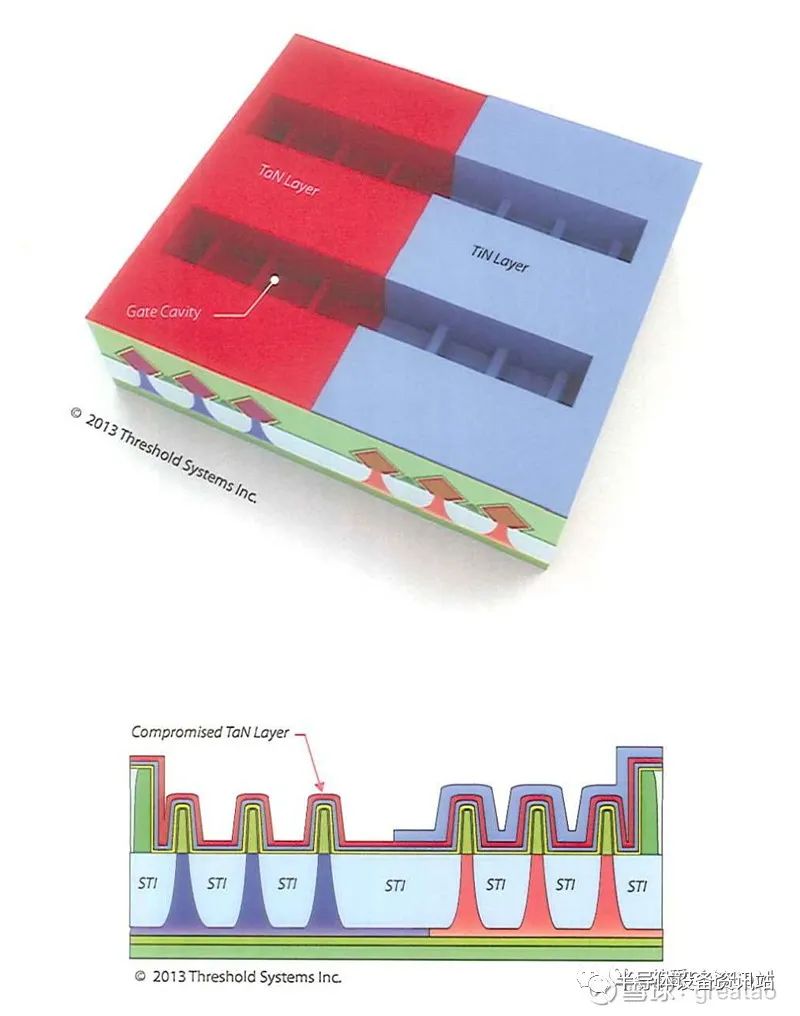

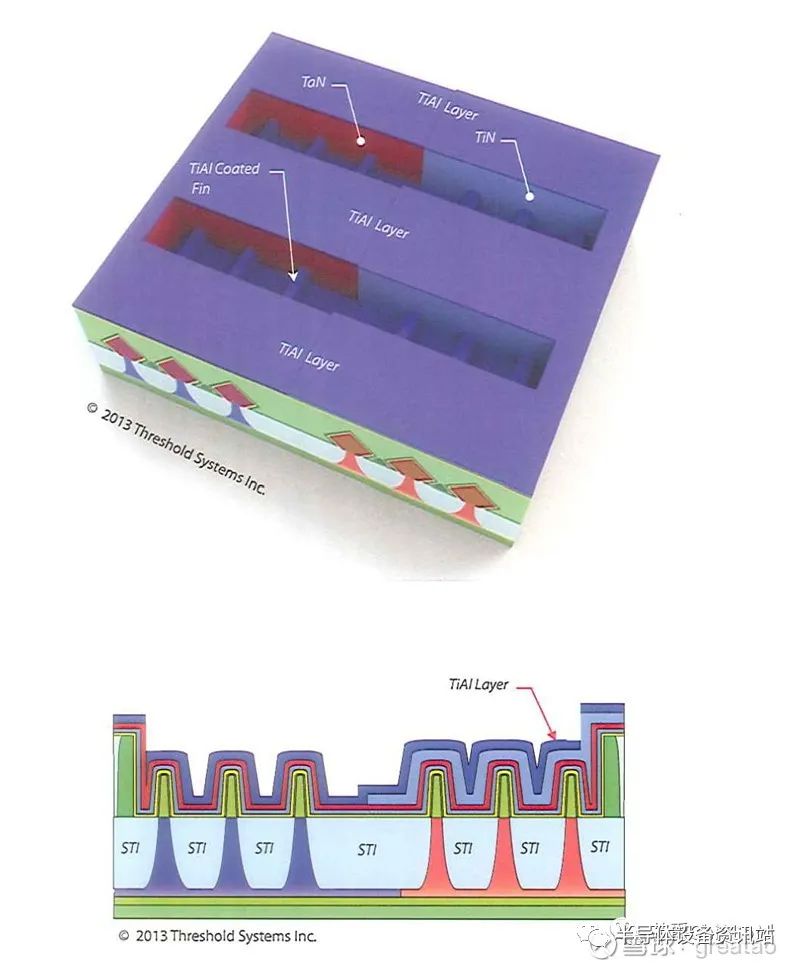

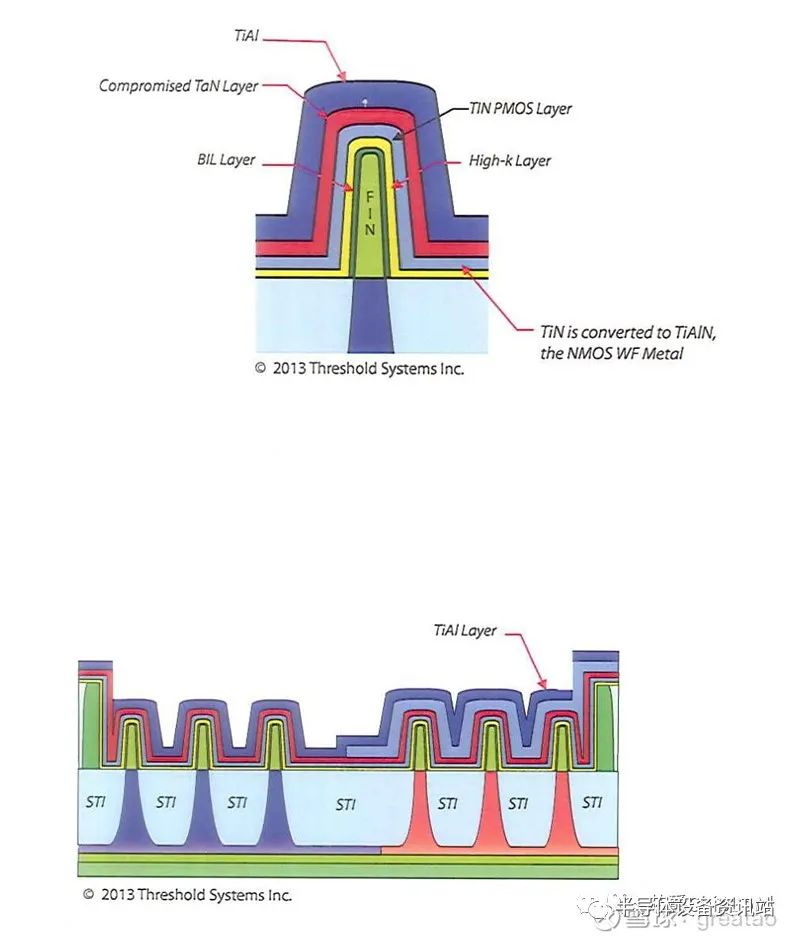

48. NMOS Metal Deposition

然后通过SIPVD(Self Inoizing Phsical Vapor Deposition)工艺在NMOS/PMOS区域deposit一层TiAl金属

49. NMOS Metal Anneal

在一定温度下

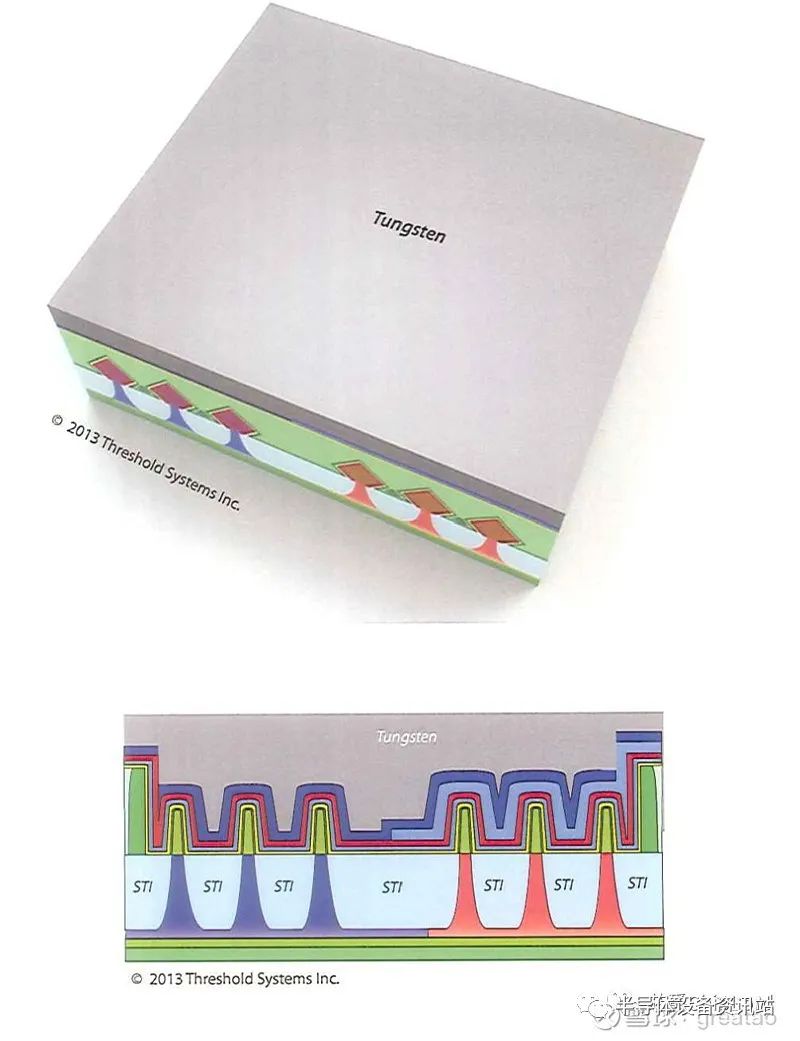

50. Tungsten Deposition Back-Fill

然后deposit一层厚厚的金属钨

51. Tungsten Metal Polish

然后CMP工艺磨平金属钨

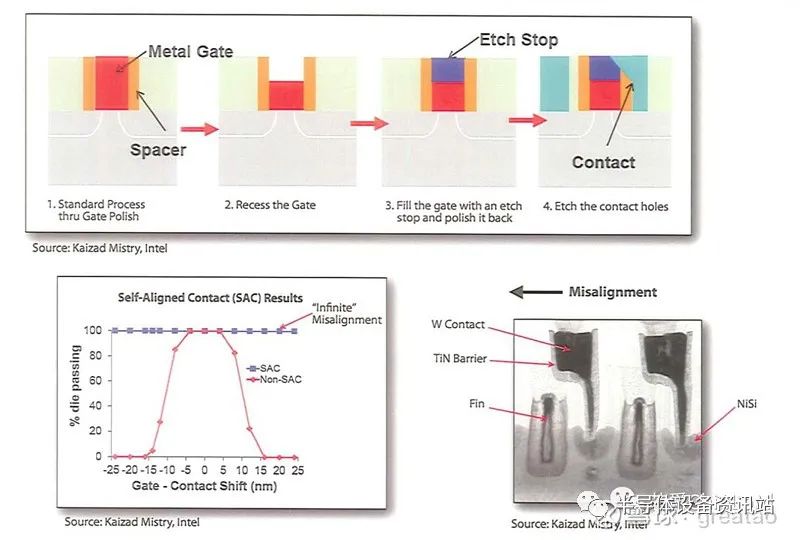

52. The FinFET Self Aligned Contacts

这里的contact用了SAC(Self-Aligned Contact)工艺

53. Gate Metal Etch-Back

金属钨和Metal gate被etch back

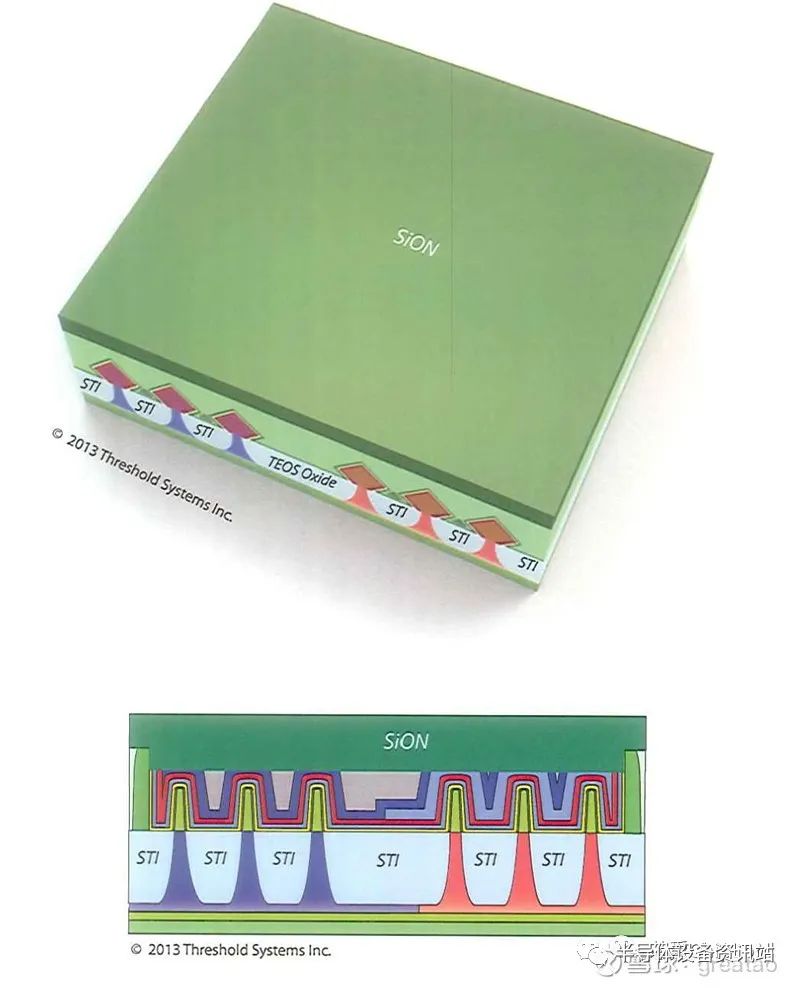

54. SiON Back-Fill

然后CVD deposit一层SiON

55. SiON Polish-Back

下一步是通过CMP磨平

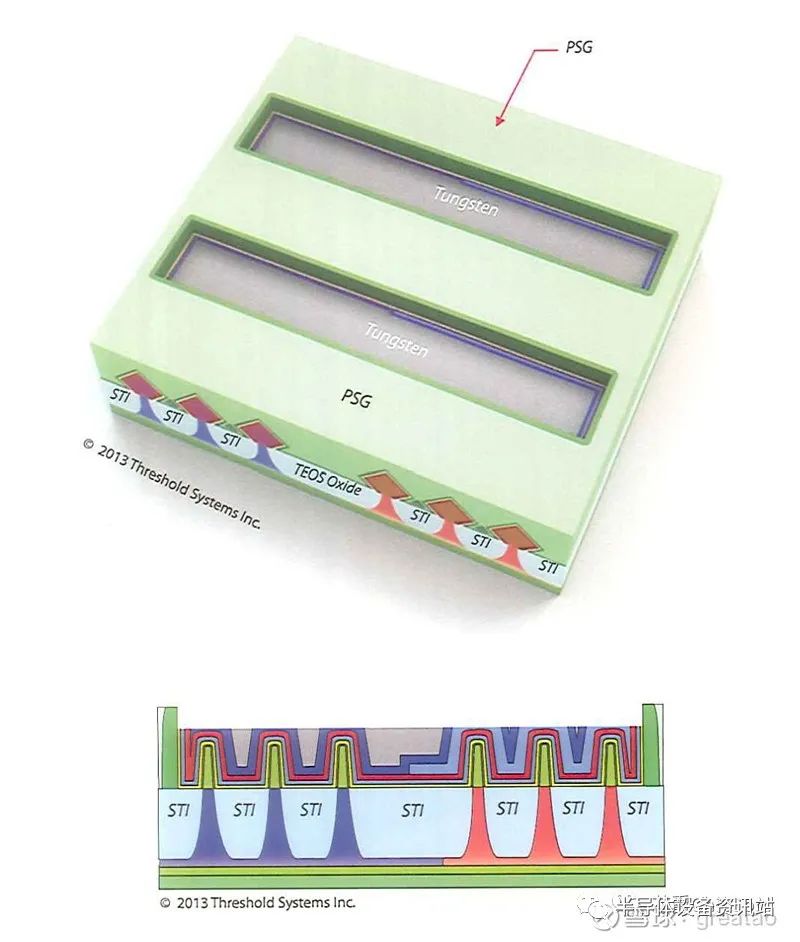

56. PMD Completion

然后再deposit一层厚厚的PSG做为PMD(Pre-Metal Dielectri)

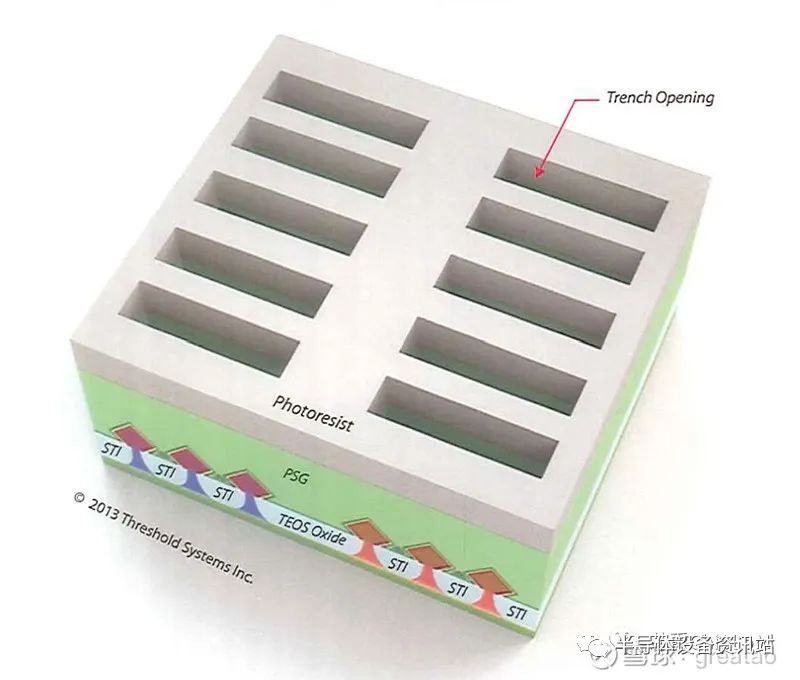

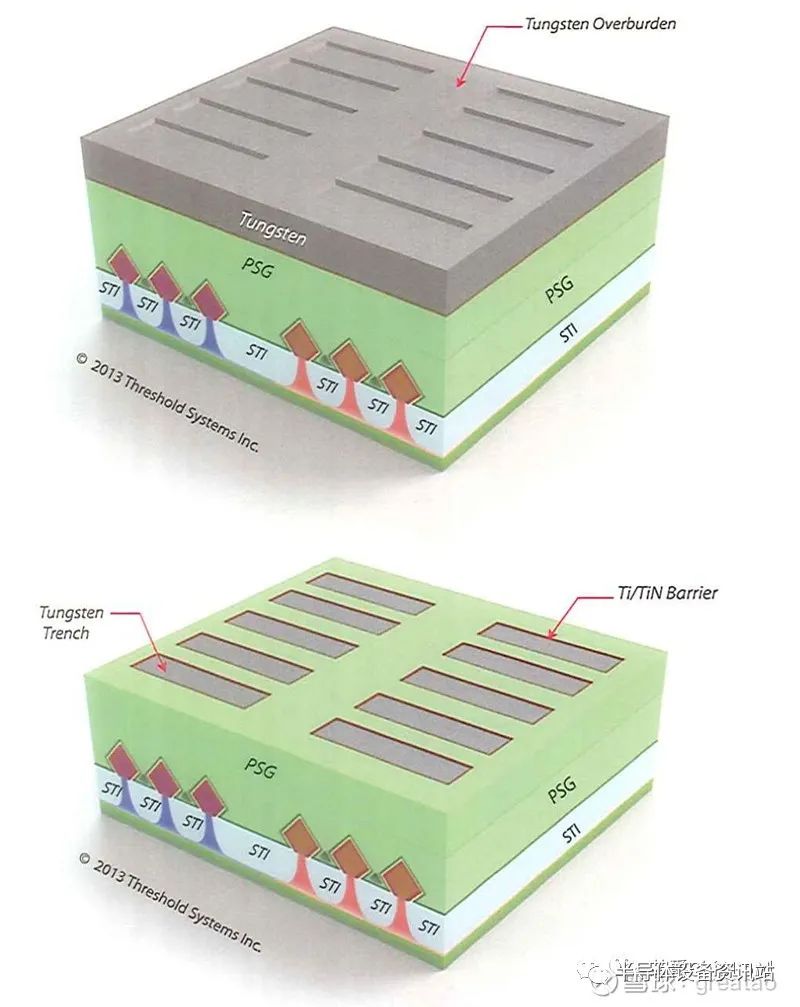

57.Tungsten Trench Contacts; Patterning

然后铺上PR

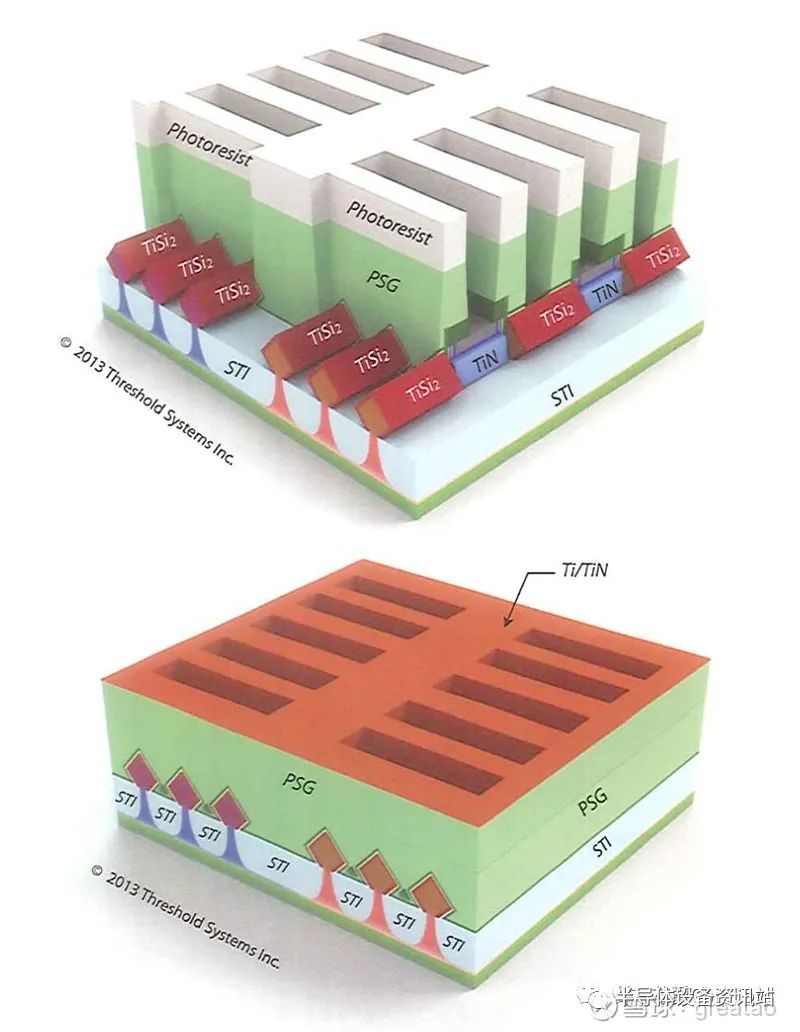

58.Ti/TiN Barrier Deposition

经过清洗干净后

59. Tungsten Deposition Polish-Back

然后开始通过CVD deposit一层厚厚的金属钨

到此为止

FinFET由美籍华人科学家胡正明(Chenming Hu)教授在1999年提出来

来自:公众号 芯爵