来源:SiP与先进封装技术

作者:Suny Li

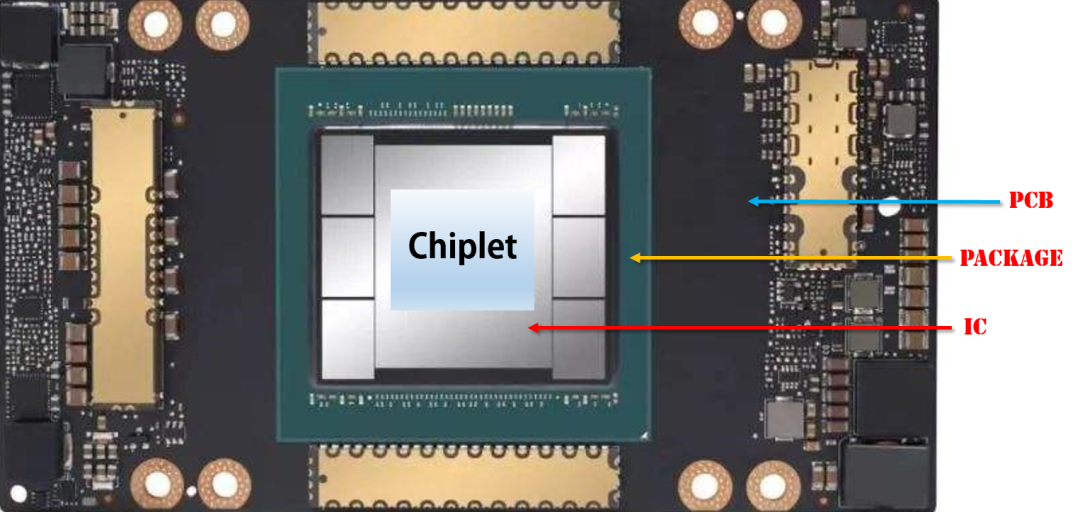

设计 | 仿真 | 生产 的数据一致性

对于现代电子产品来说,从精妙的构思到成为实际的产品,要经过成千上万个步骤,也需要不同团队之间的合作,根据产品的复杂程度不同,团队的大小也不同,小到几个人,大到成千上万人皆有可能。

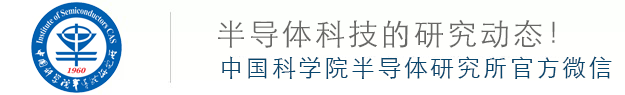

IC\传统封装\PCB

IC\先进封装\PCB

对于封装和PCB来说,其设计、仿真、生产的流程基本上是一致的,尤其当封装进化为SiP和先进封装之后,二者都属于电子集成技术,只是实现的层次不同。封装中的设计单元是裸芯片Chip或者Chiplet,而PCB中的设计单元是封装好的芯片,是前者集成的产出物。

因此,我们下面的讨论中,并不专门区分封装和PCB,而统一进行设计、仿真、生产的论述。

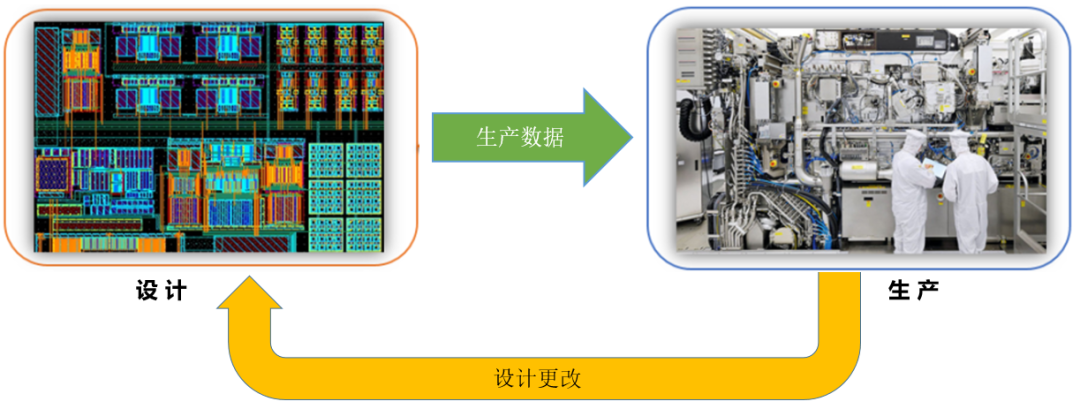

早先的产品研发,仿真环节相对比较淡化,设计完成后往往直接进行生产,然后再进行调试,修改,再生产,整个产品研发周期比较长,需要经过多次重复才能达到预期的目的。

随着设计复杂程度的提高,投产一次的成本也日益高涨,设计-->生产的模式已经无法满足产品的需求。生产之前,没有经过充分且完备的仿真分析,几乎是不可能做出成功的产品。

这就需要在设计和生产环节之间加入仿真环节,并且仿真的重要性日益提高。随着仿真技术的发展和日益成熟,出现了一些新的概念和名词,例如数字化样机,数字化双胞胎、数字孪生等概念,二者从本质上来讲都属于仿真的范畴。由此也可以看出业界对仿真环节的重视。

设计最终成为产品,生产环节至关重要,设计的目的就是为了生产,因此,从设计到生产的数据传递久经考验,是比较成熟稳定的,例如芯片从设计到生产常用的数据格式为GDSII,PCB从设计到生产常用的数据格式为Gerber,封装则较为特殊,从早先传统封装的DXF到SiP常用的Gerber再到先进封装常用的GDSII。

设计 | 仿真 | 生产 的数据一致性

对于从设计到仿真,其数据的传输方式则更为灵活和多样化,但其成熟度要稍逊于设计到生产的数据传递。

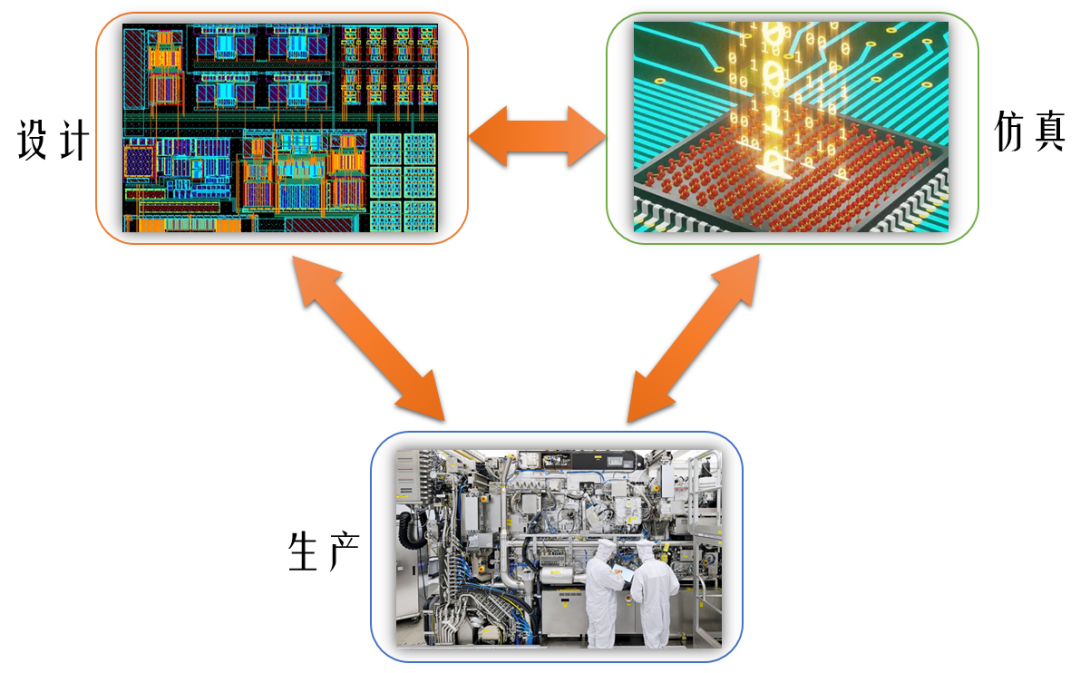

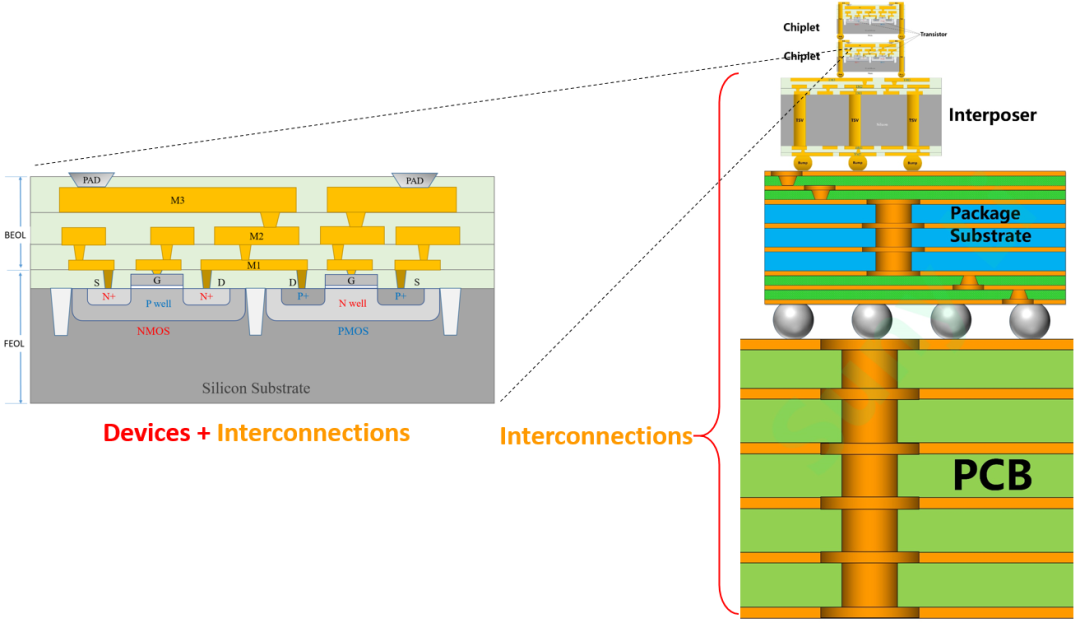

严格来说,从芯片到PCB的多级集成中,真正的器件模型只存在于第一个层次的集成中,即芯片中的晶体管模型,其他层次的集成如Interposer, Package、PCB中均为互连模型,如下图所示。

同时,有一点非常重要,就是:器件模型+互连模型=>新的器件模型,是对本层次的模型化描述,并作为模型应用在下一个层次的仿真中。

例如在芯片内部,用器件模型来描述晶体管,其他的互连线和RLC都被视为互连模型;到了封装层次,芯片整体作为一个器件模型,封装中的互连线,平面层,RLC等被视为互连模型;到了PCB层次,封装好的SiP或先进封装(里面包含多块芯片和它们之间的互连)作为器件模型,PCB上的互连线,平面层,RLC等被视为互连模型。

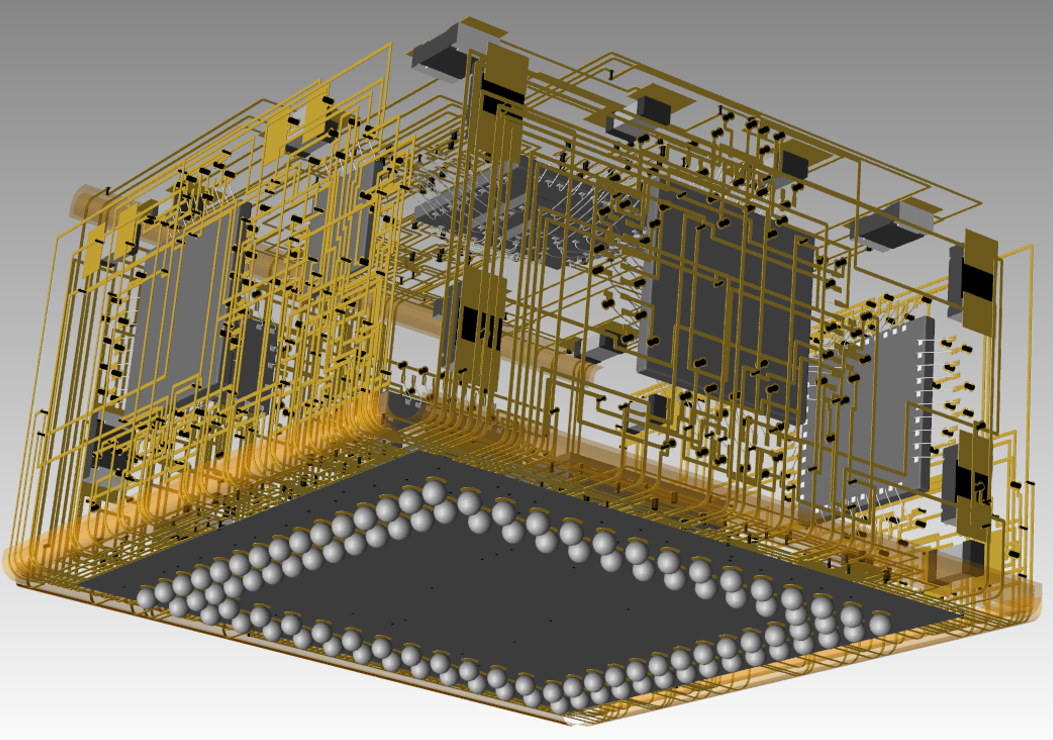

从下图中,我们可以看出,芯片中的晶体管和互连形成第一级别的模型,再加上Interposer上的互连和Bump形成第二级别的模型,再加上封装基板上的互连和BGA形成第三级别的模型。

不同级别的分类也可以根据实际需求进行灵活调整,例如将Interposer上的互连和封装基板的互连统一处理,形成芯片和封装两级模型。

从上面的描述,针对封装和PCB,我们可以得出如下结论:器件模型来源于上一层次的集成,在本层的集成主要是针对互连模型。

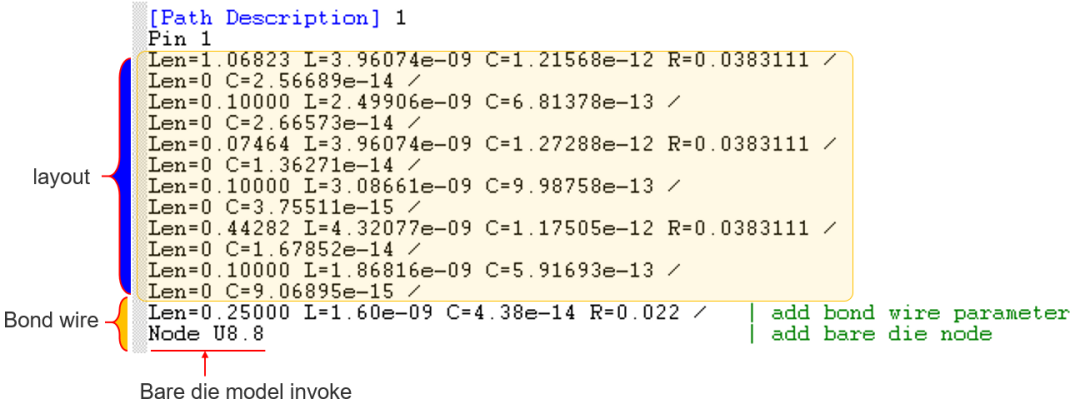

下面就是对典型封装互连模型描述的实例,分为基板上的布线Layout和键合线Bond wire,是通过RLC参数对不同段的Layout或者Bond wire进行描述。

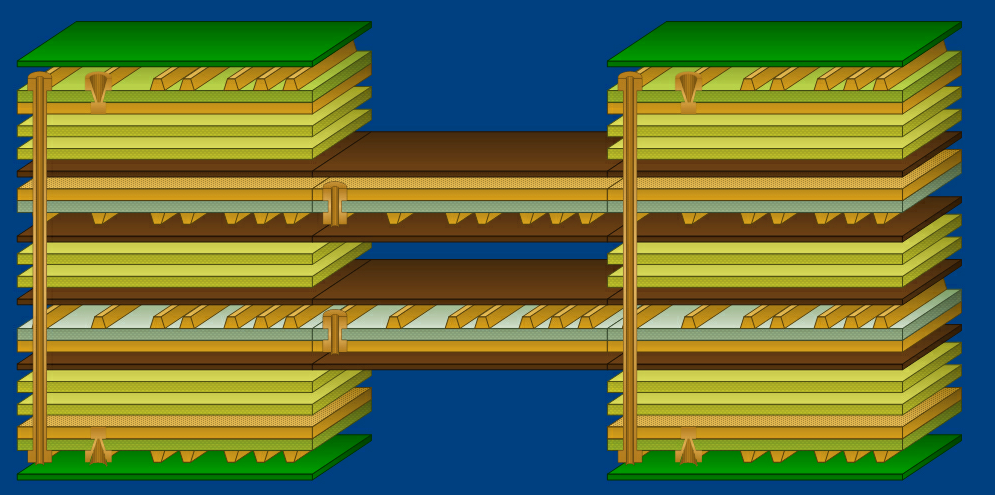

在封装和PCB的原理图和版图设计中,主要的任务就是进行正确的互连,原理图根据器件的功能对其逻辑互连关系进行定义,并传递到版图,版图依此是对物理互连分层绘制,并通过过孔或者TSV将各层连接起来。

生产则是将版图的每一个物理层制造出来并组合到一起,使器件的功能正常运行并实现设计的目标,为了保证这个目标顺利实现,在生产之前需要进行充分的仿真。

从设计数据到仿真数据,中间需要经过数据的传递和转换。

对于版图来说,需要传递的数据包括版图层叠结构、每一层的材料、厚度、物理参数等,随着设计复杂程度的提高,需要传递的数据愈发复杂。

然而,随着设计的日益复杂,能够正确识别设计数据就成为仿真工具的重大挑战,例如,设计工具可以准确地描述芯片堆叠、腔体、键合线,导入仿真工具后,不同的元素可能会出现错位,设计工具可以准确地描述多层叠结构、多区域、多个弯曲,导入仿真工具后,层叠、区域、弯曲均可能出现偏差,这些错位和偏差,轻则导致仿真精确度下降,严重则导致无法仿真。

从二维空间升级到三维空间,对设计、仿真和生产都带了挑战。

早先的EDA设计工具基本都是平面化的,从顶视图的角度去浏览每一层信息,现在设计工具逐渐走向3D化。就目前来说EDA工具的设计界面还是2D的,通常会有一个3D的浏览窗口,可以查看详细的3D信息。

转载内容仅代表作者观点