面对三星电子(Samsung Elcetronica )、台积电加速先进制程进进,重返晶圆代工战场,目标力夺制程技术王位的英特尔(Intel),进度也未见放缓,近日更近一步揭露Intel 4 (先前称为Intel 7nm)制程的技术细节。

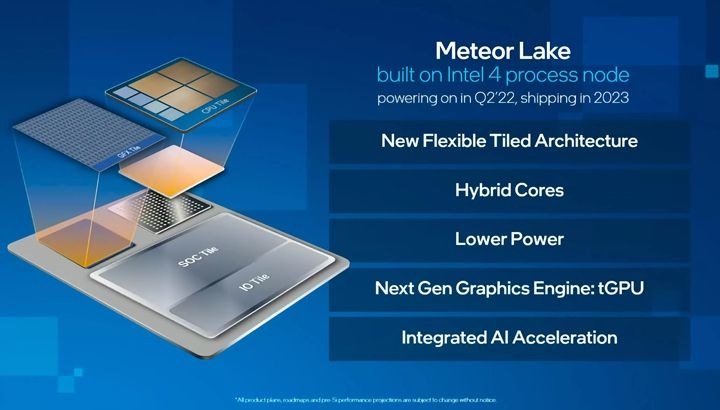

英特尔表示,相较于Intel 7(先前称10nm Enhanced SuperFin),Intel 4于相同功耗提升20%以上的效能,高效能元件库(library cell)的密度则是2倍,同时达成2项关键目标,除满足开发中产品的需求,包括PC客户端的Meteor Lake,同时也推进先进技术和制程模块,将带领英特尔2025年重回制程领先地位。

英特尔先前已揭露制程与封装技术的最新路线规划,未来5年及之后的产品都将按规划时程导入,甚至将提前。英特尔CEOPat Gelsinger先前就强调:「摩尔定律不死。英特尔对于下一个创新10年,规划清晰的道路走向1纳米及其未来。」

在新的制程节点命名方式与各节点的技术方面:「Intel 7」系基于FinFET最佳化,相较Intel 10nm SuperFin每瓦效能可提升大约10~15%;「Intel 4」为全面使用极紫外光(EUV)微影技术,透过超短波长的光,印制极小的形状。伴随每瓦效能提升约20%,以及面积改进,Intel 4将于2022年下半准备量产,2023年开始出货,client用户端Meteor Lake和数据中心Granite Rapids将率先采用。

Intel 3将进一步汲取FinFET最佳化优势与提升EUV使用比例,以及更多的面积改进, Intel 3较Intel 4约能够提供18%的每瓦效能成长幅度,将于2023年下半开始生产;Intel 20A(2纳米)则以RibbonFET和PowerVia技术开创埃米(angstrom)时代。

Intel 20A制程技术预计将于2024年逐步量产,已确定获得高通(Qualcomm)采用;改良自RibbonFET的Intel 18A已进入开发阶段,预计于2025年初问世。近日英特尔宣称,2024年初20A(2纳米)就会开始生产,18A(1.8纳米)亦提前在2024年下半面市。

在即将面市的Intel 4方面,英特尔也进一步说明了详细效能数据表现,Intel 4于鳍片间距、接点间距以及低层金属间距等关键尺寸(Critical Dimension),持续朝向微缩的方向前行,并同时导入设计技术偕同最佳化,缩小单一元件的尺寸。

透过FinFET材料与结构上的改良提升效能,Intel 4单一N型半导体或是P型半导体,其鳍片数量从Intel 7高效能元件库的4片降低至3片。综合上述技术,使得Intel 4能够大幅增加逻辑元件密度,并缩减路径延迟和降低功耗。

另外,Intel 7已导入自对准四重成像技术(SAQP)和主动元件闸极上接点(COAG)技术来提升逻辑密度。前者透过单次微影和两次沉积、蚀刻步骤,将晶圆上的微影图案缩小4倍,且没有多次微影层叠对准的问题;后者则是将闸极接点直接设在闸极上方,而非传统设在闸极的一侧,进而提升元件密度。

Intel 4更进一步加入网格布线方案(gridded layout scheme),简单化并规律化电路布线,提升效能同时并改善生产良率。随着制程微缩,晶体管上方的金属导线、接点也随之缩小;导线的电阻和线路直径呈现反比,该如何维持导线效能抑是需要克服的壁垒。

Intel 4采用新的金属配方称之为强化铜(Enhanced Cu),使用铜做为导线、接点的主体,取代Intel 7所使用的钴,外层再使用钴、钽包覆;此配方兼具铜的低电阻特性,并降低自由电子移动时撞击原子使其移位,进而让电路失效的电迁移(electromigration)现象,为Intel 3和未来的制程打下基础。

另一方面,将光罩图案成像至晶圆上的最重要改变,可能是在于广泛的使用EUV来简化制程。英特尔不仅在现有良好解决方案中的最关键层使用EUV,而且在Intel 4的较高互连层中使用EUV,以大幅度减少光罩数量和制程步骤。英特尔将在这些制程更广泛地使用EUV,更将导入全球第一款量产型高数值孔径(High-NA)EUV系统。

责任编辑:朱原弘