科技产品永远不缺天马行空的想象,设计师们脑洞大开,创造了各种既炫酷又实用的高科技电子产品,让我们的生活更加便利和有趣。因此,创新是电子行业经久不衰的长期逻辑根基,而这背后支撑创新的引擎的则是半导体产业的频繁迭代和工艺技术升级。

其实,半导体产品技术、工艺的升级就是在同样的硅片上堆积更多的电子元器件,用以实现产品的体积更小、功耗更小,功能更强大。可以看到,随着数据速率不断提升、系统芯片计算能力日益强大、IC微型化以及有限空间中有多种电源要求,组件和系统对ESD也愈加敏感。半导体工艺小型化趋势亦会导致ESD风险增加,因为较小的电压会损坏较薄的栅极氧化层。尽管面临这些挑战,但好在通过优化ESD保护概念,可以避免或大幅减少ESD造成的损坏或EOS(电气过应力)。

器件结构简述

PART 1.

回顾历史,早在上世纪六十年代,人们就开始注意到ESD在电子零件中产生的破坏性,并在包装材料中增加导电性材料来达到减弱静电的生成和积累。时至今天,ESD&EOS保护产品已经形成体系,并呈现多技术、多构架的特点。从产品工艺布局来看,半导体器件有横向和纵向布局;从技术平台来看,半导体器件有常规PN结结构、小骤回结构(shallow snapback)和大骤回结构(deep snapback)。

图1 常规PN结结构

图2 小骤回结构

图3 大骤回结构

作为一家深耕保护器件领域20多年的厂商,维安已经完全掌握了上述所有工艺技术平台。常规结构在同样的工作电压条件下击穿电压更低,启动更快;而骤回结构在同样的工作电压条件下钳位电压更低。

基于不同工艺平台的产品都有其特定的优势,如何才能让客户根据自己的实际应用选择一款最适合自己的产品呢?

理论简析

PART 2.

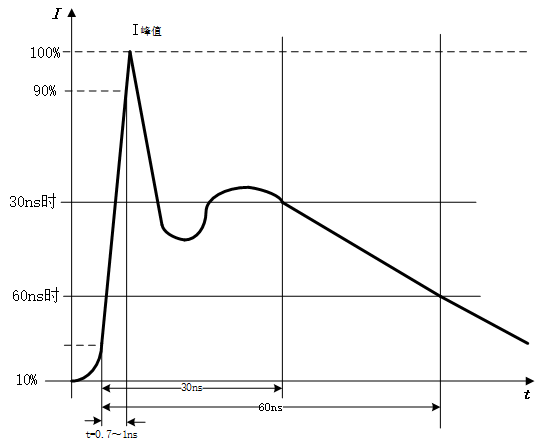

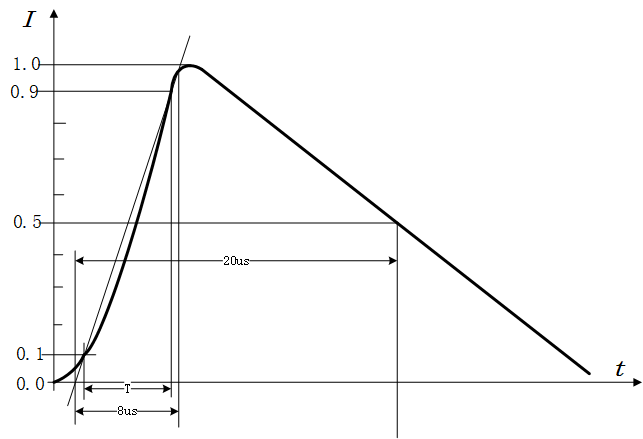

IEC61000-4-2标准波形图模拟了电路使用环境中遇到的ESD&EOS,从该图进行分析,似乎第一尖峰和第二尖峰都有损坏后端IC的可能。

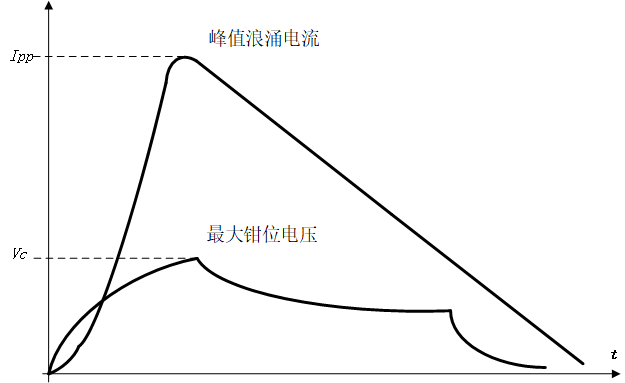

第一尖峰时间短,但是电压高;第二尖峰电压低,但是时间长(为了便于理解,这里直接采用标准中的电流波形乘以固定阻抗来类比,实际条件下电压会更复杂)。而ESD&EOS保护器件可在泄放浪涌电流的同时将电压钳位,使得后段IC仅需承受钳位电压而不至于损坏。

图4 IEC61000-4-2电流波形

图5 IEC61000-4-5电流波形

图6 EOS保护器件钳位电压波形图

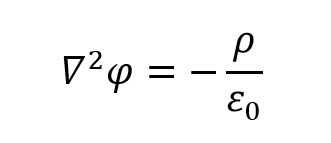

对于集成度越来越高的IC电路,其硅氧化层介质层的绝缘性能是抗ESD&EOS能力的关键。首先,用泊松方程来简单分析一下IC I/O端口介质层的物理击穿特性。

φ代表电势(单位为伏特), ρ是电荷体密度(单位为库仑/立方米),而ε0是真空电容率(单位为法拉/米)。

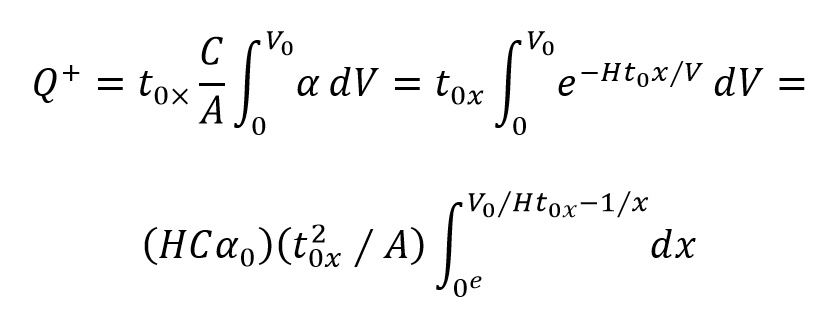

以泊松方程和电流方程得到介质表面俘获空穴电荷密度随时间变化的物理方程(注1):

从方程中可以看到,积累在介质表面(以氧化层为例)的电荷除了与时间τ有关系外,还与外加电场E有关系。考虑到IC I/O会受到外界的电压是非恒定的,时间单位可能是ns、us甚至是ms,所以电场E也是非恒定的。取HBM ESD脉冲条件下的氧化层俘获空穴密度,经过推导和计算得出:

当氧化层俘获空穴密度达到临界值时介质层发生击穿。从上式简单分析可知,发生击穿的临界值与所加电场强度、氧化层厚度tox和时间均有关系。

结束理论分析,我们得出,IC I/O端口在遭受外界能量时,有诸多不确定因素导致其损坏击穿。但是研发工程师在进行实际设计的时候,很难进行理论计算,也几乎没有芯片供应商会在IC规格书中详细注明其浪涌耐受能力和芯片制程等信息。

从通信端口的发展来看,最早出现的低速通信线电压幅值都比较高,端口耐压也相对较高;从保护的角度来看,端口的高耐压可以容忍较高的钳位电压;从通信速率看,低的通信速率可以接受的较大寄生电容。

综合上述两点,保护器件的钳位电压在一定范围内数值高低对保护效果影响不是很大,有很充裕的可选择性。随着通信速率的提高,信号线幅值和端口耐压在不断降低,对保护器件提出了新的挑战,一方面要求相同测试条件下的钳位电压要更低,还要做到超低的寄生电容,传统结构的器件已经不再满足客户的需求。

如HDMI端口接口芯片的耐压低,且不同厂家的耐压值也不同,要保证都测试通过,就要求保护器件兼容最低耐压,在工程应用中也存在着走线过长、接地不稳定等引起的μs级别甚至ms级别的高能量破坏性波形引入,骤回结构应用而生。

骤回结构可以做到低电容、高耐压且钳位电压非常低,超低电容在高速通信中不会对信号有较大的影响,高耐压可以避免误动作,钳位电压低可以有效保护在ESD打击下被保护器件不需要耐受过高的电压。从客户角度出发可以相对完美地解决低电容、低钳位电压的应用需求。

维安通过在实际应用和方案整改过程不断的归纳,总结出如下应用要点:

- 常规结构

几乎适用于所有的端口保护,具体参数与被保护的端口电特性相关联。但是对于一些耐压差的器件,可能会有测试失败的情况。

- 小骤回结构

适用于信号端口和部分较差工艺制程的电源IC接口。较常规结构相同测试条件下具有更低的钳位电压。选型需要注意VBO、IH和VH参数,防止浪涌电压小于VBO时的保护盲区和VH低于电源波动高电压时出现的闩锁。

- 大骤回结构

适用于高工艺制程的高速信号接口,具有超低电容和钳位电压,对耐压敏感型接口具有很好的保护作用,对电流源驱动型端口不建议使用。对于此类器件,关注参数较多,选型须慎重,可能会带来端口闩锁或失效。

具体案例分析

PART 3.

某客户需要在信号端口进行EOS测试和ESD测试。客户同时选取了A厂家的小骤回性器件α和维安公司的器件β。

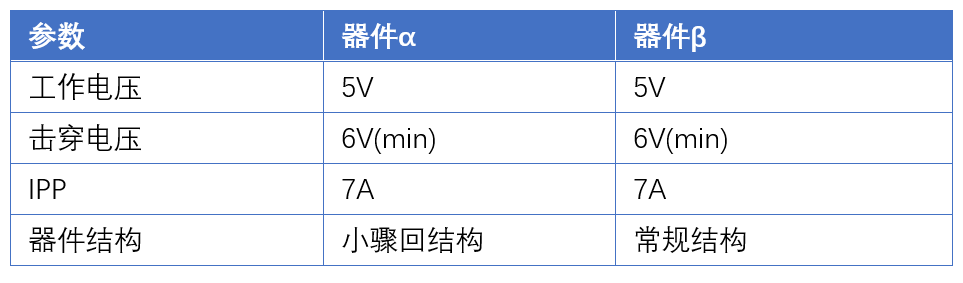

规格书数据如下:

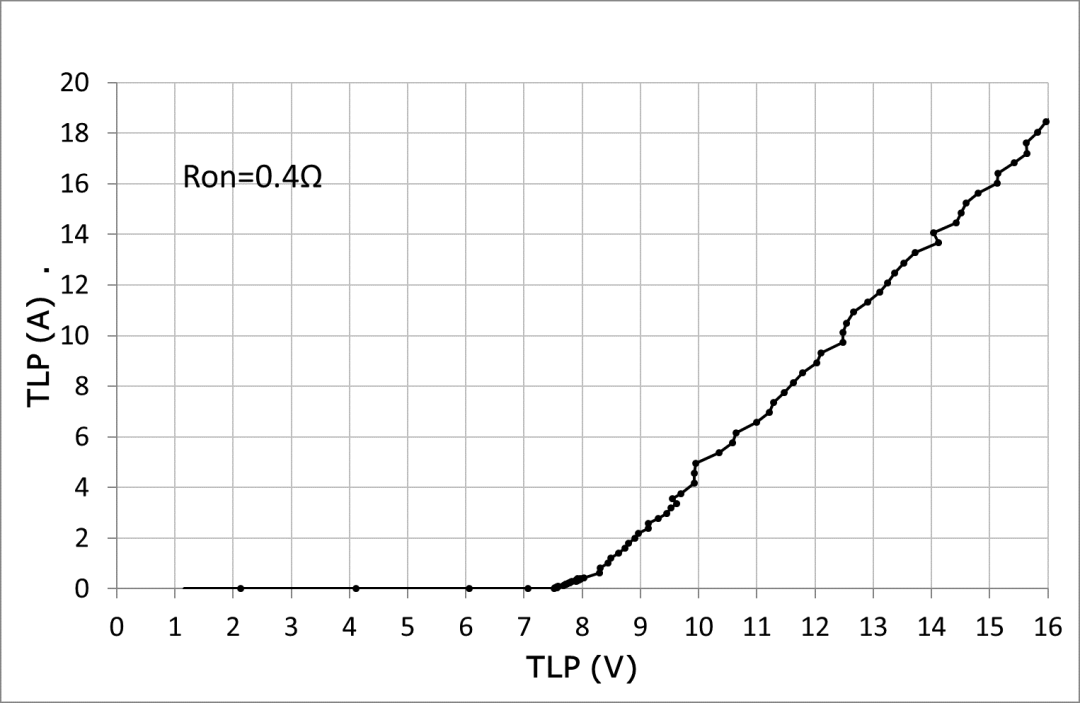

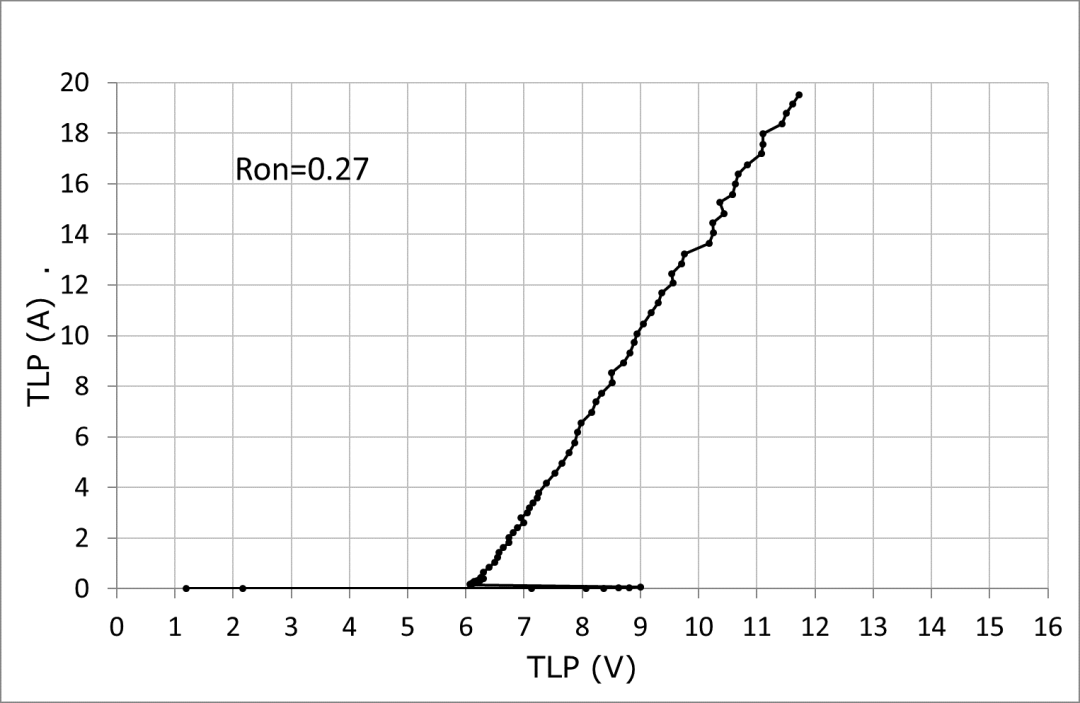

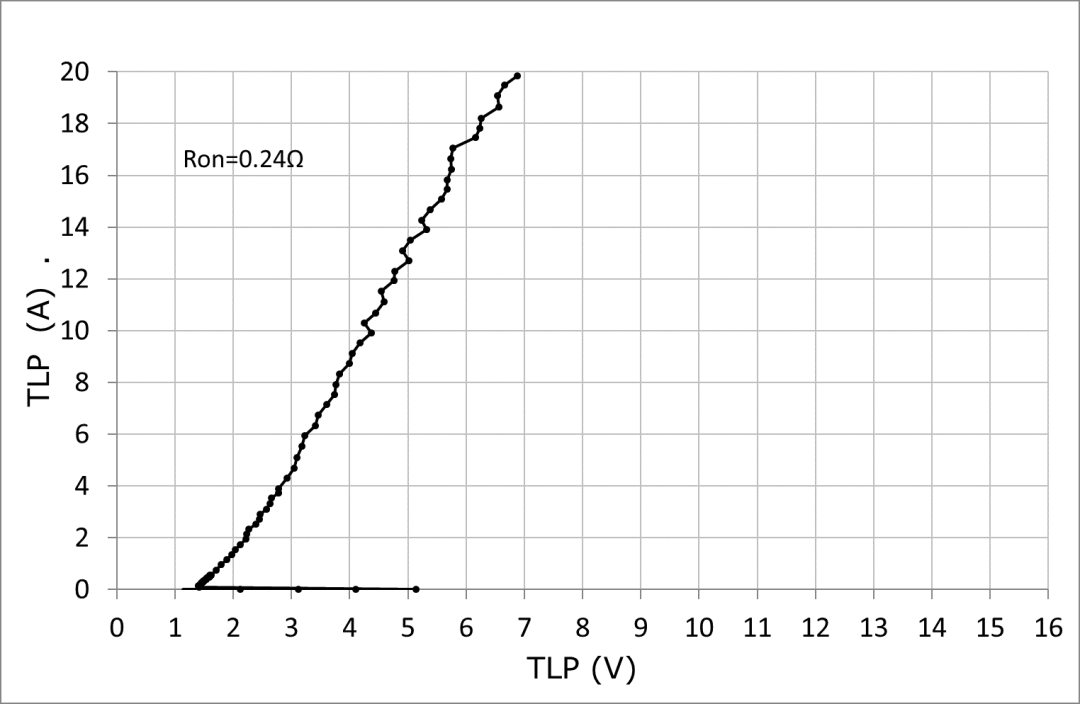

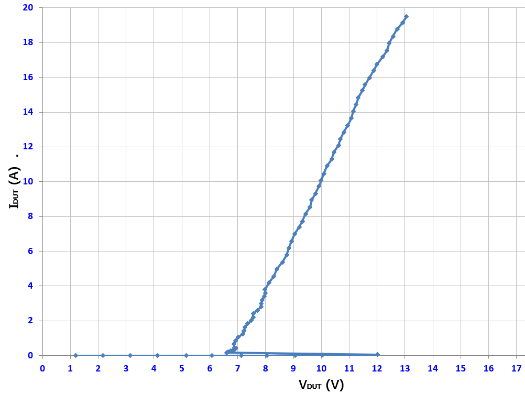

TLP曲线:

图7 器件α TLP曲线

图8 器件β TLP曲线

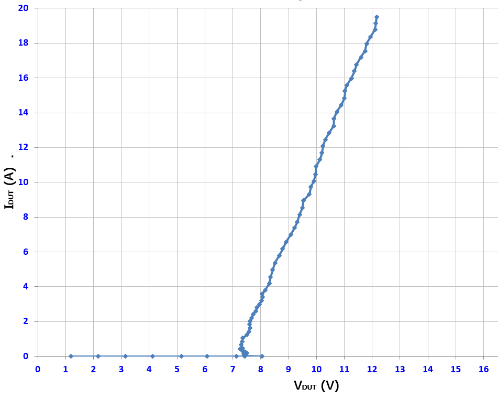

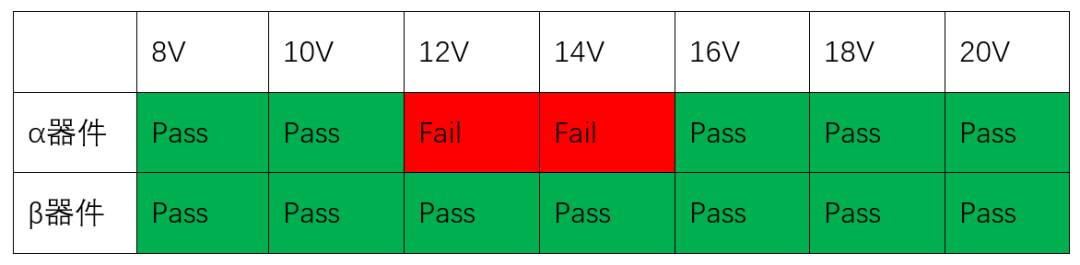

从规格书的部分参数可以得出,两家产品的性能比较接近,主要是结构不同。测试结果如下:

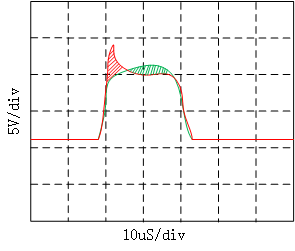

α器件能通过浪涌等级20V,但是在从8V开始的步进测试中,12V和14V却出现了后端IC失效的结果,当浪涌电压更高时,器件又起到了保护的作用;而β却能通过整个浪涌等级的测试。从器件规格书对比来看,α的VC比β要好。通过示波器抓取电压得到如下波形:

图9 器件钳位后的电压波形(红色α,绿色β)

从波形可以看出,红色阴影S红和绿色阴影S绿部分是两个器件的能量分布差异;α器件在12V附近的电压条件下,其由于促使器件trigger的打开时间偏长甚至是未打开,而后端的IC却无法承受施加的浪涌能量,导致后端IC失效。反观β器件,只要浪涌电压超过器件的击穿电压,器件就会动作,并迅速钳位电压,来达到保护后端IC的目的。

对于有经验的测试和研发人员来说,当外部施加的EOS浪涌更高时,比如16V以上,这时骤回结构的优点开始凸显,钳位效果也会更好。但是作为设备的可靠性保护,其保护范围是一定要保护等级定义下的全浪涌范围的保护,而不是有一个保护盲区。

总结

PART 4.

不同结构的TVS器件在保护后端设备时,呈现的结果并不是确定性的。除了器件本身的参数,研发人员在进行保护方案设计的时候需要清楚自己产品的特点,可能所遭受的环境能量估算和对保护器件的大致选择,以达到最好的产品保护的目的。

目前业内大部分厂家都是直接给推荐电路,直接告诉设计者答案选择哪个器件,却很少对选型过程提供理论推断、计算。大部分电子工程师针对ESD&EOS选型时,老人凭经验,新人凭参考,一旦更换厂家或者更换测试条件,就无从下手了。

维安依托优秀的FAE技术团队和完善的EMC实验室可进行方案设计、优化和整改,高质量的服务客户,为客户的产品提供强有力的保护。

注1:理论分析部分参考引用了朱可平教授的文章。