碳化硅 (SiC) 元件能够为电力输送系统实现更高的效率和可靠性,尤其是对并网型且几乎全天候运行的逆变器和有源整流器。由于行业正在寻找更环保的解决方案,例如太阳能和电动汽车 (EV) 充电领域,对于更高效率和更可靠元件的需求也愈发旺盛。

由于 SiC 技术的进步,并网型系统能够从更高的功率密度、更快的开关速度、更低的运行温度和更低的整体成本中获益。除了太阳能/风能/混合能和 EV 充电外,其他高功率应用,例如工业设备、不间断电源以及其他电源应用等也催生了对更高功率因数校正 (PFC) ,以及双向能量流动等其他能力的需求。

Wolfspeed 推出了多种创新产品和包含参考设计以及仿真软件的工具集,能够赋能并网型应用。本文将探讨如何选择与应用相匹配的器件和拓扑方式,以及能利用哪些 SiC 元器件(分立式器件或模块)和资源协助设计人员进行开发。

并网型应用的器件和拓扑选择

高功率应用对于 PFC 的需求增加已经持续数十年,始于包含 LC 元件的桥式(二极管)整流器。虽然传统配置实施起来非常简单,但性能和尺寸曾是关键限制因素。目前,有源升压 PFC 拓扑已被大部分应用所采用,它能够以合理的成本提供合适的性能,但是仅能提供单向功率流动(对其应用范围造成了限制),而且无法满足当今最新的高效标准。

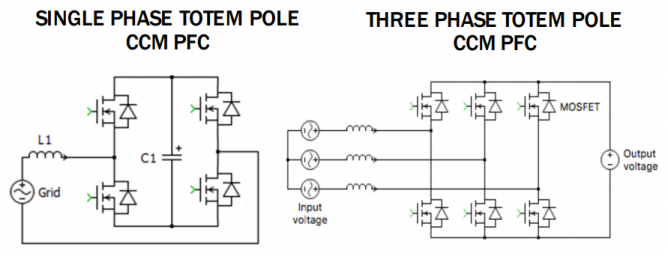

连续导通模式无桥图腾柱 PFC(图 1)实现了较低的损耗、双向功率流,并实现了高效性能,使得 SiC 技术能够为功率转换和传输市场实现转型。

▲ 图 1:无桥图腾柱 PFC ,单相(左侧)和三相(右侧)

Si MOSFET 体二极管拥有较高的反向恢复电荷和时间(最新款 15 mΩ / 650 V 超级结 Si MOSFET(带快速体二极管)在高温下的 Qrr 约为 10,000 nC,Trr 为 500 ns),而 SiC MOSFET 的体二极管的数值要低得多,例如最新款 25 mΩ / 650 V SiC MOSFET 的该数值分别为 293 nC 和 22 ns。因为图腾柱拓扑需要有出色的体二极管性能,Si MOSFET 由于其反向恢复时的 Qrr 和 Trr 较大,并不是实用的解决方案。虽然在单相和三相图腾柱拓扑中可以使用绝缘栅双极型晶体管 (IGBT),但是其开关损耗和导通损耗较高,限制了最大开关频率。多电平IGBT 变换器解决了部分开关问题,但需采用更复杂的控制方法,而且通常需要多个元器件和栅极驱动器,导致更高的系统成本。

SiC 可以实现简单高效的拓扑,例如单相和三相图腾柱拓扑,在实现更高的功率密度的基础上还可以具备更多功能。它能够降低开关损耗,可以运行更高的开关频率,并可以提高功率密度,降低磁性元件的重量、尺寸和成本。得益于较低的导通电阻RDS(on) ,效率可以高达 99%。同时,由于元件较少,且控制形式简单,能够降低整体系统成本。

Wolfspeed SiC 产品组合通过分立式元件(低功率应用)和功率模块(高功率应用)可支持多种功率应用(1 kW 至 600 kW 甚至更高)。电压范围涵盖 650 V 至 1700 V 的共 50 多种产品,具备较高的拓扑灵活度,能够满足功率密度、效率和可拓展解决方案的规格。

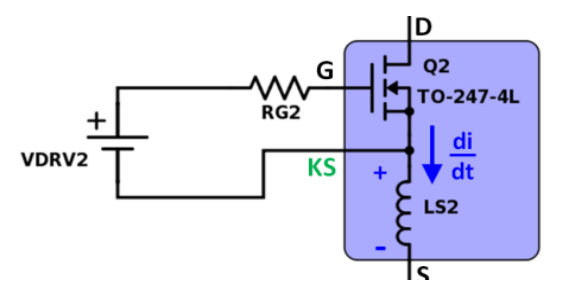

根据不同的具体应用,分立式 SiC 器件或 SiC 功率模块有助于实现基于不同功率等级和功能的设计。分立式 MOSFET 包含开尔文源极引脚,可以控制源极,使其旁路任何封装导致的寄生参数(在开关过程中产生感生电压)(见图 2,了解使用“KS”引脚优化控制的示例)。

▲ 图 2:经优化的 MOSFET 封装 (TO-247-4L),包含第四个开尔文源极引脚

对于高功率应用,WolfPACK 系列模块能够“直接”替换现有解决方案,同时充分利用经过优化的 SiC 性能,得到最大的载流能力(得益于杂散电感被最小化)。BM2、BM3、FM3 和 GM3 模块采用久经检验应用的封装形式,可以轻易的实现多货源供给,而 XM3 和 HM3 是专为优化性能而设计的定制模块,可发挥最佳性能,具备出色的电流能力。

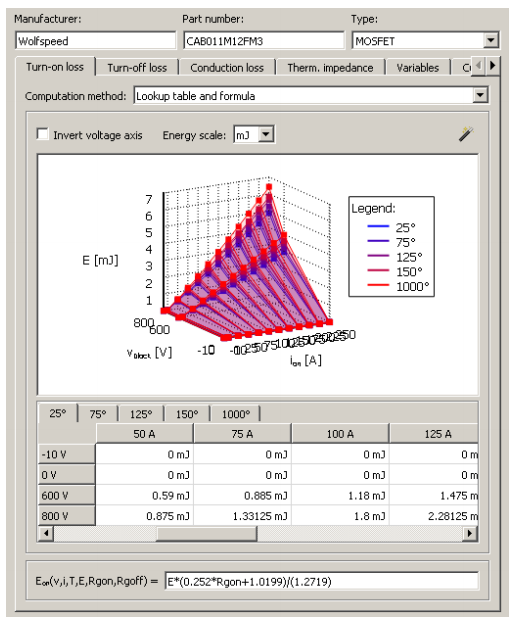

结合 PLECS 模型使用 SpeedFit,可以帮助设计人员建模并模拟完整的电力电子设备系统来找到匹配的器件,包括进行热/损耗建模并模拟数据表特征。这些仿真模型都是基于真实结果,可以提供获得预期性能的视觉化演示(见图 3)。

▲ 图 3:SiC MOSFET 开关能量与漏极电流视觉图像

此外,SpeedFit 可进行网络在线仿真,它包含完整的模型库,可通过额外的软件实现设计灵活性。多种常用拓扑都已预加载,可使用准确的损耗模型快速仿真,从而验证设计。

在为 SiC MOSFET 设计栅极驱动器时,必须考虑多个关键因素。下方列出了一些满足 Wolfspeed SiC MOSFET 应用的典型规格:

隔离:共模瞬变抗扰度 (CMTI) 大于 100 kV/µs

绝缘:最大工作绝缘电压 (VIORM)

驱动能力:达 5 A

传输延迟时间:50 ns 或更佳

通道失配时间:10 ns 或更佳

有源米勒钳位

栅极电源电压:15 V / -4 V

为了满足这些标准,Wolfspeed 同时还提供了评估工具和资源,以帮助设计人员选择合适的拓扑方式和器件。例如,Analog Devices 的 ADI AduM4146 是一款包含隔离单通道驱动器的参考设计,可驱动 Wolfspeed 的 SiC MOSFET,还包含 Silicon Labs 的 Si823Hx 隔离双通道驱动器(可用于半桥方案)。Texas Instruments 的 UCC21710 能够提供达 10 A 的驱动能力。所有这些组件集成在现成、即插即用的平台上,可评估 Wolfspeed SiC MOSFET。

Wolfspeed 参考设计/套件,以及 SiC 与 IGBT 的比较

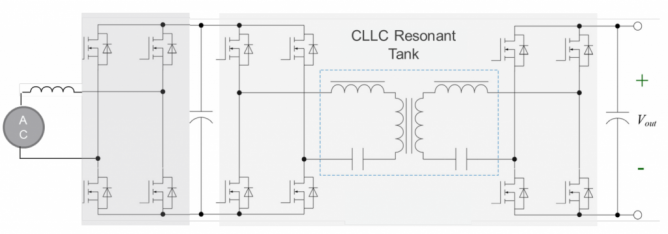

CRD-06600FF065N-K 是一款可配置为电动汽车充电应用的单相 6.6 kW 双向车载充电机 (OBC) 的参考设计,同时还可作为“可并网”的电力储能装置。其包含图腾柱 PFC (AC/DC) 级和隔离双向 CLLC DC/DC 级,系统峰值效率可达 96.5%,功率密度达 3.3 kW/L(见图 4)。对于正在开发中的电动汽车和并网储能应用来说,这款设计是绝佳的出发点,其能够对 Wolfspeed 分立元件进行完整的评估和测试,同时包含一套设计文件,包括设计原理图/布局图以及相关硬件。

▲ 图 4:CRD-06600FF06N-K 参考设计图 单相 6.6 kW 双向 OBC

在开发过程中,还可参考另一款高效(在 22 kW 时为 98.5%)高功率、三相双向充电机设计,可用于评估分立式元件并提供设计指南。这款设计包含 Wolfspeed 的 1,200 V 32 mΩ SiC MOSFET,配置在两电平六开关 PFC/逆变器中。

对于需要使用多个 MOSFET 的高功率应用,可以考虑使用 WolfPACK 功率模块。例如,25 kW 有源前端 (AFE) 可以使用 FM3 系列模块(包含六个 SiC MOSFET),可与适当的散热片、磁性元件、栅极驱动器、电压/电流传感器以及控制器配合使用。此外,建议添加一些安全相关的功能,例如软启动、保险丝以及 EMI/EMC 滤波器。图 5 示出了该配置图(MOSFET 位于“功率级”)。采用相同的配置,对 WolfPACK FM3 模块以及Si IGBT进行对比测试,测试发现,SiC 的开关频率可以高达 5 倍(最高达100 kHz),其损耗降低超过 400 W(运行条件为 25 kW,480 V 输入和 800 V 输出)。采用 SiC 获得的性能提升还带来了一些额外优势,例如滤波器尺寸更小、整体效率更高(比 IGBT 高 2%),运营成本更低。

▲ 图 5:WolfPACK FM3 功率模块(左侧) 以及适用该模块的 25 kW AFE 配置

对更高功率 (200 kW) 的 AFE/逆变器进行了类似的比较实验。与现有 Si IGBT 解决方案相比,CAB400M12XM3 SiC 模块能够显著降低损耗、尺寸和成本,这是由于其开关频率升高且元件(磁性元件、电容器和散热元件)尺寸更小。比较性能后我们发现,当运行在 100 kW 到 300 kW 条件中时,XM3 模块的整体损耗较为平稳,约为不到 1,000 W。同时,在 200 kW 输出条件下,效率提高约 0.75%。XM3 组件可以作为核心元件进行购买,包括散热、驱动器、控制器和传感元件。图 6 为使用 SiC 技术的 200kW AFE / 逆变器和目前使用 Si IGBT 元件解决方案的尺寸比较。

▲ 图 6:Si IGBT 解决方案(左)和 SiC 解决方案(右)的尺寸比较

磁性元件、PCB/系统布局,以及如何优化以获得最佳效率

在开发高功率电源的过程中,需要考虑磁性元件对于功率密度和效率的影响。在高开关频率运行下(由 SiC 实现),磁芯和绕组的功率密度会提高,而损耗会降低,这就意味着效率更高。通常情况下,考虑到性能和系统成本时往往需要折中,但使用 SiC MOSFET 有助于提高性能,降低损耗。在选择应用的电感时,需要考虑材磁芯料和构造。一些构造欠佳的电感会有明显的“边缘效应”,会由于涡流而带来额外的功率损耗。

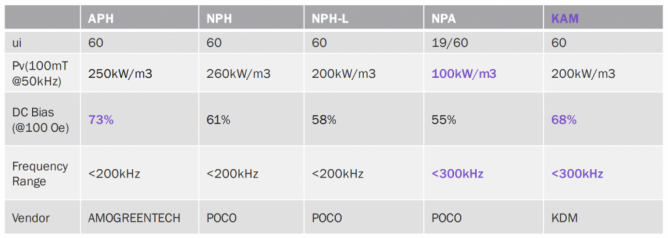

图 7 为电感器及其参数和性能的比较列表。在磁芯损耗、直流偏压、频率范围和功能之间需要进行折中。

▲ 图 7:电感器参数和性能比较

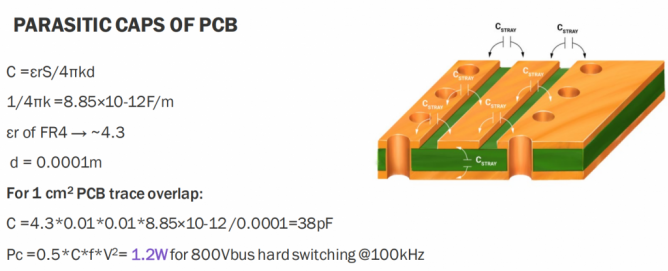

高能量的开关行为会造成 PCB 走线和节点的 dV/dt 和 di/dt 显著变化。在设计 PCB 布局时,将漏极节点的Pad尺寸最小化,以降低耦合及寄生电容,同时使敏感信号源远离高 dV/dt 走线/节点以及磁场(例如 PFC 扼流圈),这十分重要。

当高功率漏极平面靠近栅极走线线/pad时,会形成寄生电容,导致严重的功率损耗。例如,800 V 母线 上的 1 cm2 的 PCB 走线重叠区域在 100 kHz 运行条件下会造成 38 pF 的寄生电容,造成 1.2 W 的损耗(见图 8)。而开关损耗由于栅极电荷的升高而升高,最终会影响效率。当栅极附近(栅极分别与源极和漏极之间)存在杂散电容时,且当两者之间的比例较大时,会形成串扰,导致直通和更高的电压尖峰。栅极信号处增加电容(外部栅极电阻的另一端)会加剧栅极震荡,降低整体可靠性。通过减少走线长度、留意敏感走线和可能出现的高 dV/dt 和 di/dt、妥善布置功率元件,避免在栅极、栅极驱动电路、栅极驱动器电源和 MOSFET 漏极之间形成重叠,便能够将这些杂散电容最小化。上述参考设计是 SiC 应用经优化布局实践的良好示例。

▲ 图 8:PCB 上的寄生电容的解释(带 SiC MOSFET 信号)

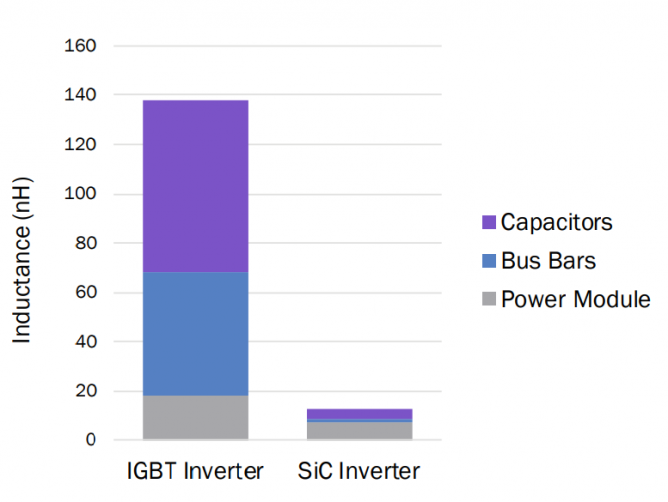

对于包含功率模块的系统,可以使用同样的优化方法。在使用以较高开关速度运行的功率模块和汇流排时,最小化整体杂散电感,从而尽可能提高效率,这十分重要。对于 IGBT 逆变器,由于开关速度有限,杂散电感不会有如此重大影响,但对于 SiC 逆变器,应优化母线排和电容器的设计和选择,从而充分利用其优势;图 9 的图表比较了这两者,显示了创新设计选择如何能够显著降低杂散电感。

▲ 图 9:比较 SiC 和 IGBT 逆变器功率元件的典型杂散电感图表

此外,在布局功率模块以及其它系统元件时,建议将每个模块和电容器之间的电感保持相同,同时采用较大的表面积,从而帮助散热。最好能为直流汇流排采用叠层铜排(反向抵消效应)。

结论

Wolfspeed SiC 分立式和功率模块能够为并网型转换器应用带来出色的系统级优势,包括承载更高的电压、更快的开关频率、更高的功率密度和载流能力,能够整体提高系统效率,同时降低无源器件件的材料清单成本。Wolfspeed 拥有适用于多种不同应用的丰富器件和网络在线工具,能够帮助客户评估器件,还能提供诸多参考设计,加速产品上市时间,让设计人员倍感心安。

英文原稿:https://www.wolfspeed.com/knowledge-center/article/silicon-carbide-in-grid-tied-applications/