挺长时间没有更新了,正巧昨天有朋友来问怎么报出同一根net上没有打满via的地方,或者漏打via的地方。

现在很多工具都有相关的检查了,这里推荐下cc (customCompiler)的via check功能,使用非常方便,无需自己定制rule。

下面分享几个常用的calibre的定制rule, 因为没有环境验证,下面格式供参考。

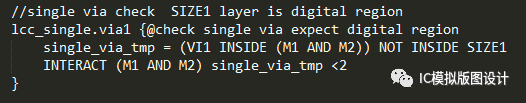

第一:DFM rule的单孔检查 并排除掉数字区域检查(SIZE1 所overlap的区域)

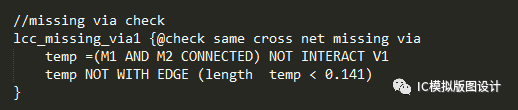

第二:相同net上的缺孔检查,排除掉打不下孔的地方

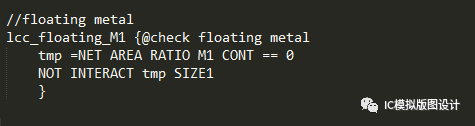

第三:floating metal的检查,排除掉数字区域(SIZE1 所overlap的区域)

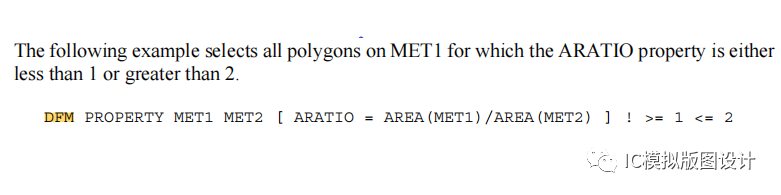

第四:相同net上孔没有打满密度不够的问题

tempa=(M1 AND M2 CONNECTED)INTERACT V1

Tempb = V1 AND tempa

结合下面DFM的示例

这个不给完整code,感兴趣的可以自己尝试下。