第一步,找出需要进行clock gating check的cell

首先,工具会沿着时钟源去trace它的fanout,并找出消耗时钟的网络。所谓消耗时钟,是指时钟信号在这些地方确实是被当成了时钟使用。

而电路中消耗时钟的点主要有以下三种情况:

时序逻辑的clock pin;

输出或双向端口(port);

以该时钟作为主时钟生成了其它时钟。

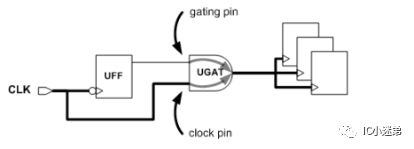

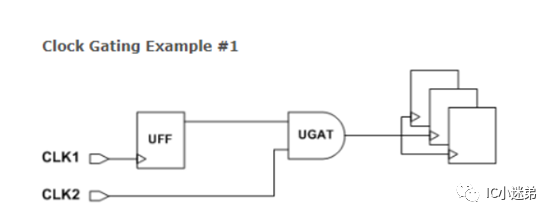

如果一个时钟信号被触发器的D引脚捕获,那么该时钟不会被认为是一个“被消耗的时钟”;相反,它只是作为一个正常的数据信号被捕获。在图1中,CLK是被加粗部分消耗了的。

图1.时钟门电路示例

接着,工具会在上面的网络中找出具有关闭时钟功能的cell,如上图中的与门UGAT。与门中的两个pin分别是clock pin和gating pin。如果这些cell的gating pin满足“不是一个时钟,或者是一个不被消耗的时钟”这一条件,那么工具就会对它进行clock gating check。

下面举两个比较特殊的例子。

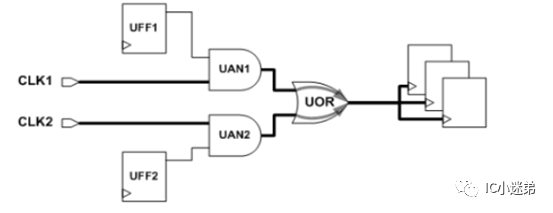

图2.组合时钟

在图2这个电路中,你可以看到,两个时钟首先用AND门进行门控,然后到达OR门。这时,工具会对两个AND门进行clock gating check,但不会对OR门进行clock gating check。这是因为OR门不符合gating pin的要求。

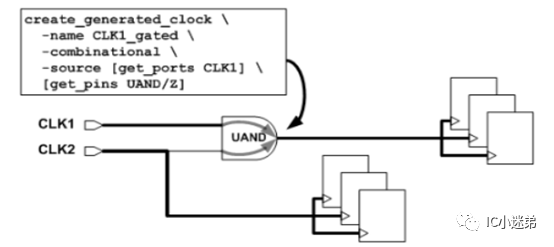

图3.使用一个时钟对另一个时钟进行门控

而图3中,在AND门的输出端产生了一个CLK1的时钟。这个生成时钟的存在导致CLK2的传播在AND门的输出被阻断。因此,CLK2到达了AND门,但实际上没有作为下游的时钟被消耗。在这种特殊情况下,PrimeTime推断CLK1是时钟信号(因为它作为下游的时钟被消耗),CLK2是门控信号(因为它没有作为下游的时钟被消耗),并据此推断出门控检查。

第二步,推断出clock gating check的检查方式

Clock gating check的检查有两种:低有效时钟门控检查和高有效时钟门控检查。这里的低有效和高有效分别是指当gatingpin为低电平和高电平时,时钟才能穿过去。例如,图1中的与门就是典型的高有效时钟门控;而或门就是典型的低有效时钟门控。

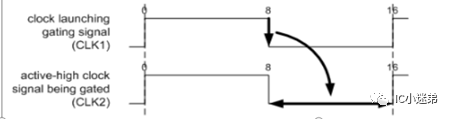

如图4,对于高有效时钟门控电路,当gating pin在时钟高电平期间跳变时,会在输出时钟上产生毛刺,所以工具在check时,必须保证gating pin的跳变是在时钟低电平期间,这样才能得到完整的时钟。

图4.门控电路波形示例

同理,对于低有效时钟门控电路,gating pin的跳变必须在时钟高电平期间才能得到完整的时钟。

工具会根据以下两种情况推断出使用哪种检查:

根据pin上的set_clock_gating_check约束进行推断;

根据电路的功能进行推断。

其中第一种方式的优先级要高于第二种,具体表现如下:

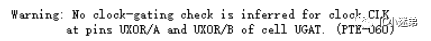

当pin上没有set_clock_gating_check的约束,工具会检查电路中cell的功能。如果cell具备AND或NAND功能,则推断为高有效时钟门控检查;如果cell具备OR或NOR功能,则推断为低有效时钟门控检查;如果cell的门控关系不明显(如MUX或XOR弧),PrimeTime会发出PTE-060警告。

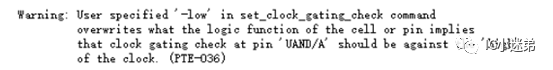

如果pin上有set_clock_gating_check的约束,则按照约束上进行检查。此时,如果约束上检查方式与cell功能推断出来的不一致,PrimeTime会报PTE-036警告。

第三步,trace时钟gating pin的发起点,并进行clock gating check。

除了推断出clock gating check的方式,工具还必须根据电路结构去trace出 gating pin的发起点,才能够进行准确的clock gating check。下面我们以与门进行说明。

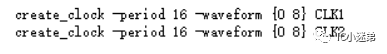

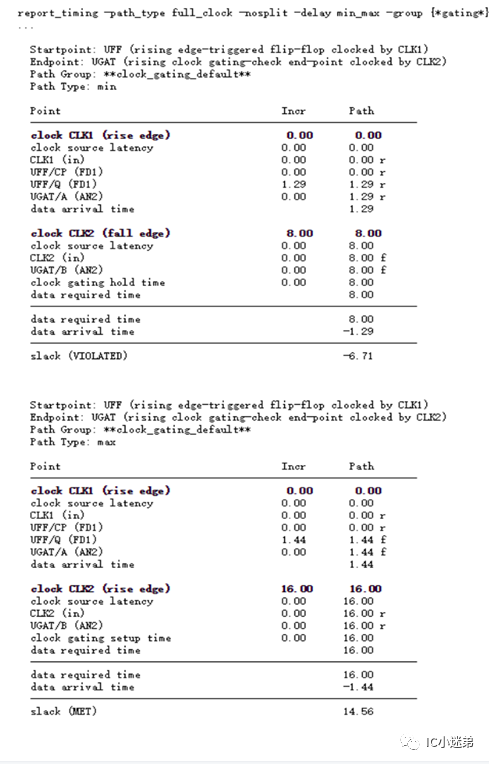

如上图,在这个例子中,设置CLK1和CLK2具有相同的波形:

门控信号是由CLK1的上升沿发送的。被门控的时钟是CLK2。因为门控CLK2的单元是一个AND门,所以时钟被推断为高电平有效,而时钟波形的非活动部分是低电平部分。假设CLK1在0 ns的上升沿发送的时钟门控信号。根据上面的分析,要得到完整的时钟信号,那么就要求门控信号必须在CLK2的8ns(下降)和16ns(上升)之间到达与门的gating pin中。换句话说,门控信号最早要在8ns之后到达,最晚要在16ns之前到达。

这里的最早和最晚分别对应的clock gating check的hold和setup检查。在PT中看到的timing报告如下:

从上面的例子中可以看出,对于与门这种高电平有效门控来说,如果门控信号是在时钟上时钟上升沿发送,那么对于Hold的收敛是一个很大的调整,特别是对于频率比较低的时钟。

同样的约束,如果将门控信号改成由时钟下降沿发出,如上图。假设在CLK1的8ns处发出,那么timing报告如下。显然,这对hold的收敛是由好处的。

举一反三:

本文给出了高电平有效(与门)的例子,那么对于低电平有效(或门)的clock gating check又会是怎样的呢?

为了方便大家更好的理解时钟门控,Martin特意搭了一个学习环境,直接拷贝到虚拟机上即可使用。虚拟机和这个学习环境可到知识星球上下载。

参考文献:

S司solvnet的一篇文章。有条件的可以上去download原文。链接如下:https://solvnet.synopsys.com/retrieve/015769.html?otSearchResultSrc=advSearch&otSearchResultNumber=5&otPageNum=1