台积电、英特尔(Intel)、ARM等全球十余家重要半导体业者日前共同发起,促进开放式晶粒到晶粒(die-to-die)互连标准和小芯片生态系的UCIe产业联盟,分析师预期,该联盟将为未来芯片发展奠定基石。

TechSpot与Seeking Alpha报导,科技谘询和市场研究业者TECHnalysis Research表示,随着芯片制程微缩因面临物理性限制而趋缓,以往透过缩小晶体管来使单体(monolithic)芯片配备晶体管数量增加,以提高芯片效能的传统做法也愈来愈不适用,许多业者开始关注其他想法和芯片设计概念。

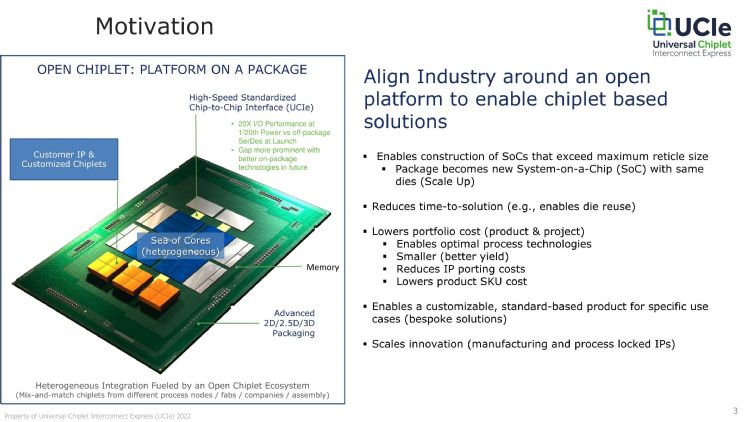

其中一种主要想法是将大型单体芯片分解为更小的元件或小芯片(chiplet),然後透过巧妙互连与封装将这些小芯片结合在一起。ARM的大小核(Big.little)芯片设计,高通(Qualcomm)整合CPU、GPU、ISP与基带的系统单芯片(SoC),以及超微(AMD)Zen微架构芯片等都是基於上述概念的运用与发展。这为芯片架构、互连与封装带来了许多重要突破。

然而大部分业者所采行的互连与封装技术都仅适用於自家产品,这意味这些芯片只能混搭自家元件。为使来自不同业者的元件也能够混搭在一起,尤其是在高效能服务器应用上,促成了开放性工业标准互连标准CXL联盟的成立与发展。

虽然CXL标准已开始运用在实际产品,但CXL还是未能真的如同积木般混搭由不同业者采用不同类型和尺寸制造技术所制造的各种不同小芯片。这也是UCIe联盟要克服之处。

UCIe建立在CXL和PCIe 5.0标准上,并且对物理实体互连和软件逻辑标准做出明确规范。这使得各业者能够据此设计和制造自家理想中的芯片。这意味着,开发出结合英特尔CPU、超微GPU、高通基带、Google TPU AI加速器,及微软(Microsoft)Pluton安全处理器的单一封装芯片将不再是梦想。

透过UCIe,不但可为芯片设计与制造业者开创出全新的机会,也为整体半导体产业创造出许多新选项。在设计业者方面,预期会有助於仅专注於非常专业小芯片,或专注於将各种小芯片巧妙组合在一起来实现特定性能的较小业者的成立和生存。

在制造方面,不是所有芯片都适合采用如4或3纳米先进节点制程制造,尤其是类比信号处理芯片,像格芯(GlobalFoundries)和其他没有最先进节点制程,但专注於独特制程或封装技术的业者,也能够在小芯片技术市场中拥有光明的未来。此外,小芯片进行混搭也会为市场带来 更多竞争,有望减少供应链中断的情况发生。

然而,要确保小芯片混搭能够顺利和无缝工作,还有很多工作要做。UCIe联盟发起成员涵盖台积电、英特尔、三星电子(Samsung Electronics)、日月光、ARM、超微、高通、Meta、微软(Microsoft)、Google Cloud等重要业者,应有助於推动如NVIDIA与苹果(Apple)等知名业者,以及其他较鲜为人知的业者参与。

责任编辑:朱原弘