SPI数据通信是常用的一种中低速芯片级的数据通信。SPI数据通信协议简单,连线不多,而且是全双工通信,因此广泛用于实现数据转换和数据存储等功能。本章简要介绍SPI数据通信的协议及主端与从端的VerilogHDL建模与仿真。

SPI数据通信协议

SPI是英文Serial Peripheral Interface的首字母缩写,中文可以翻译为串行外围设备接口。SPI 是Motorola公司首先推出的一种同步串行接口。它用于CPU或者FPGA与各种外围器件进行全双工、同步串行数据通信。SPI 通信接口简单,只需要4根线:clk同步时钟信号、mosi主端输出/从端输人数据信号、miso主端输人/从端输出数据信号、cs从端片选信号(如果有多个从端,则需要有多个cs从端片选信号与之相对应)。SPI数据通信的同步串行传输顺序是高位先传、低位后传。

四种SPI通信模式

SPI数据通信有4种模式,分别称为模式1至模式4。不同的模式是由开始数据采样的边沿及时钟的空闲状态决定的。

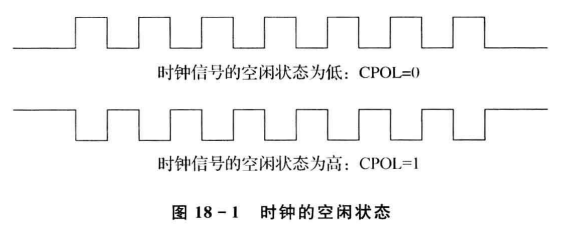

时钟的空闲状态有2种,即高电平与低电平,分别对应CPOL=1与CPOL=0,如图18-1所示。

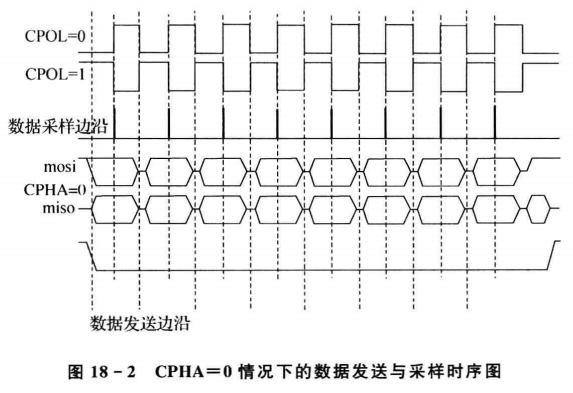

发送与接收数据的时钟边沿的情况也有2种:数据开始采样发生在时钟的第一个边沿(也可理解为奇数边沿进行数据采样)与数据开始发送发生在时钟的第二个边沿(也可理解为偶数边沿进行数据发送),分别对应 CPHA=0与CPHA=1,如图18-2与图18-3所示。

根据CPOL与CPHA的值,SPI的传输就可分为4种模式:模式0是CPOL=0,CPHA=0;模式1是CPOL= 1,CPHA=0;模式2是CPOL=0,CPHA=1;模式3是CPOL=1,CPHA=1。本章以模式0为例进行介绍。

对应图18-2,分析在片选信号下降沿有效时开始发送最高位数据,其余的数据在时钟信号的下降沿发送,最后一个时钟下降沿不发送数据。而数据采样发生在时钟信号的上升沿。

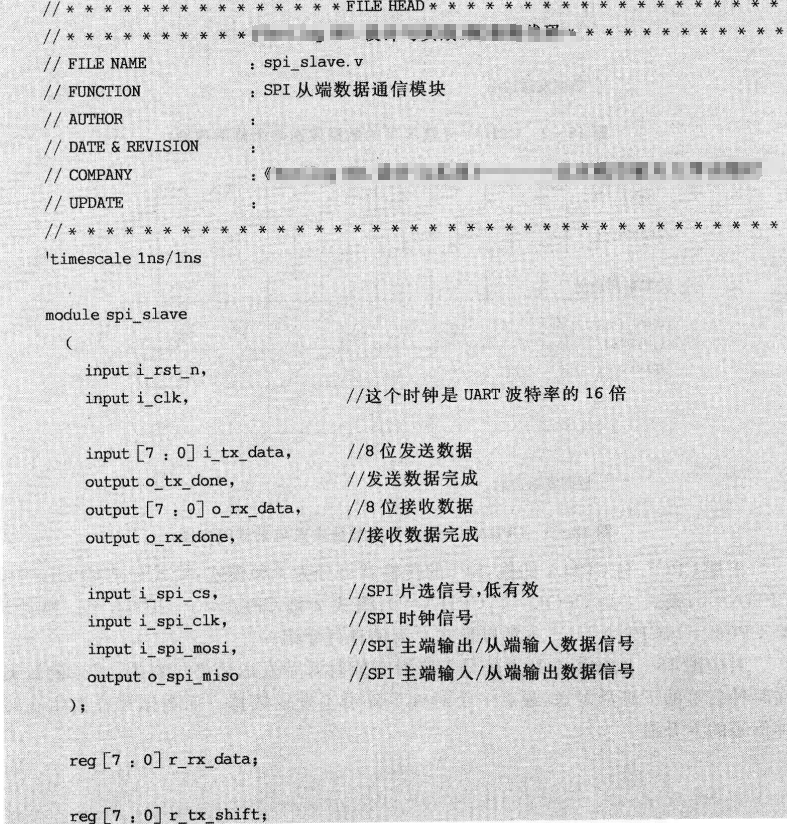

SPI从端数据通信模块

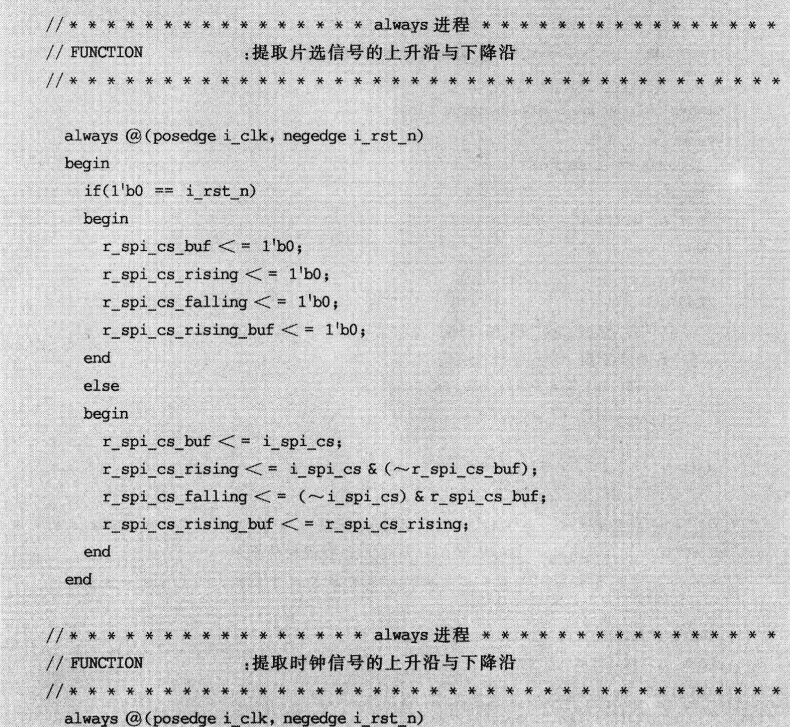

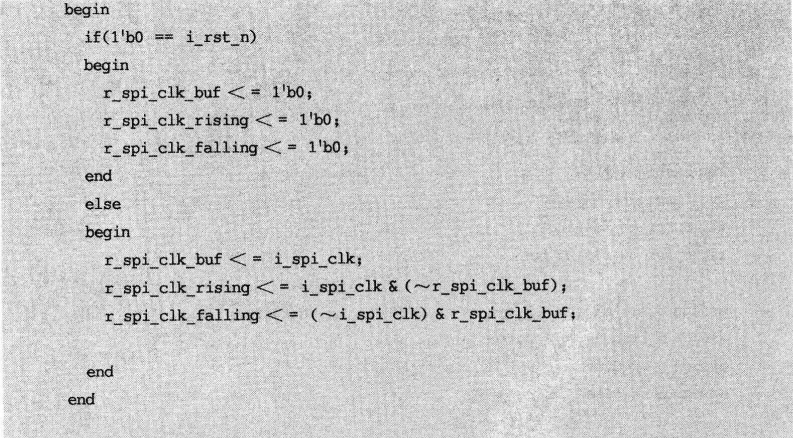

SPI从端数据通信模块建模

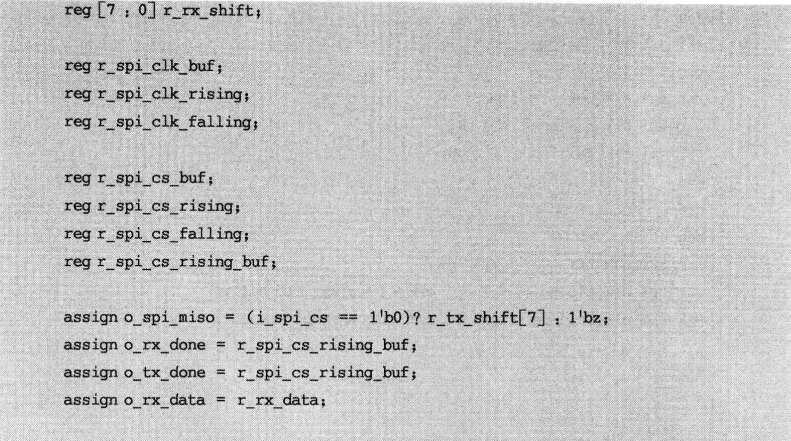

SPI数据通信分主端与从端,从端被动地进行数据通信的接收与发送。从端被动的数据通信是根据时钟信号与片选信号的边沿进行判断的。当片选信号的下降沿有效时发送最高位数据,当时钟信号上升沿有效时进行数据采样接收数据。根据以上分析设计Verilog HDL代码如【代码18-1】所列。

【代码18-1】

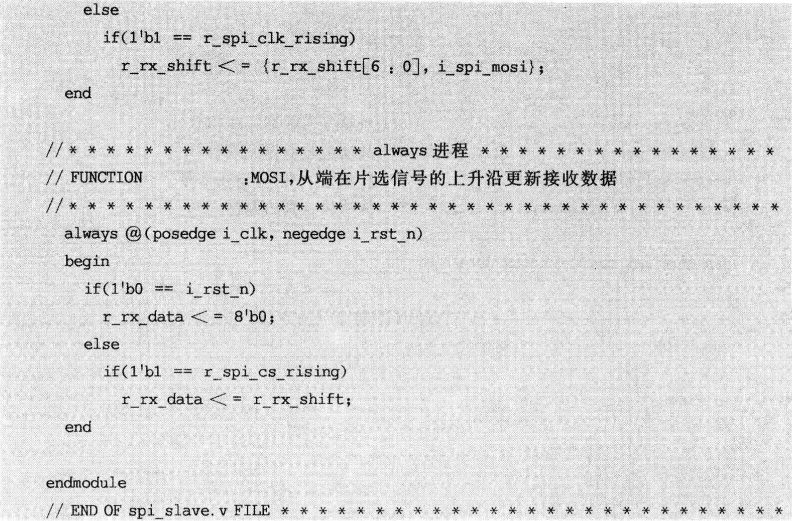

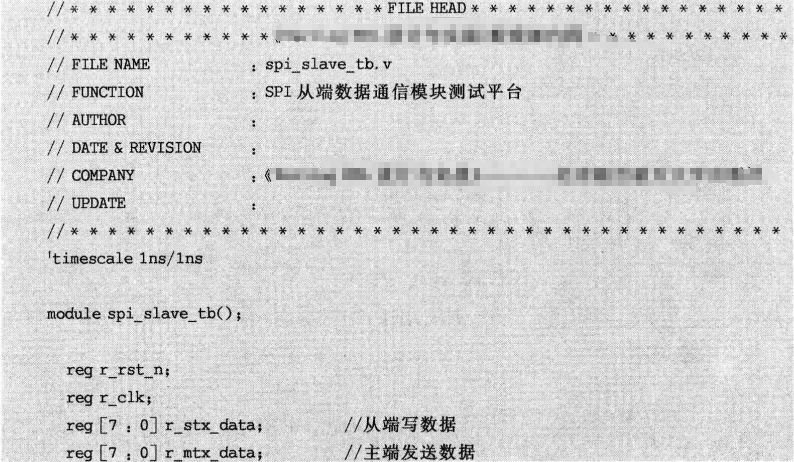

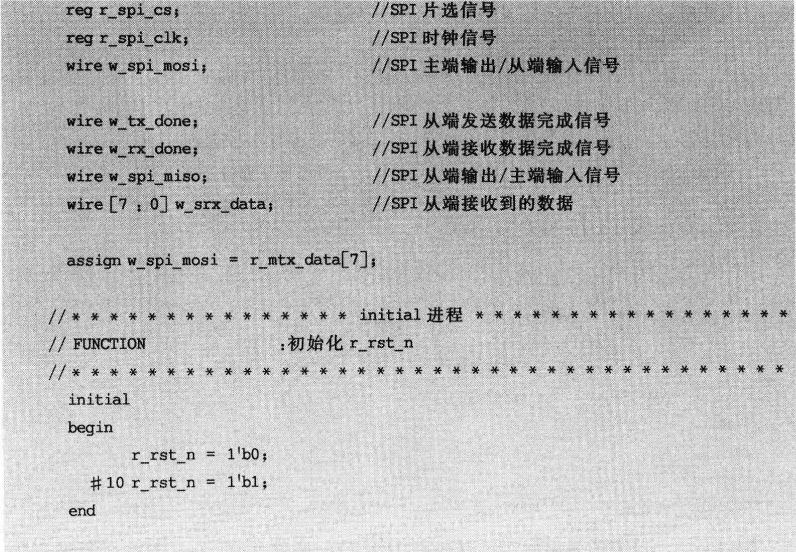

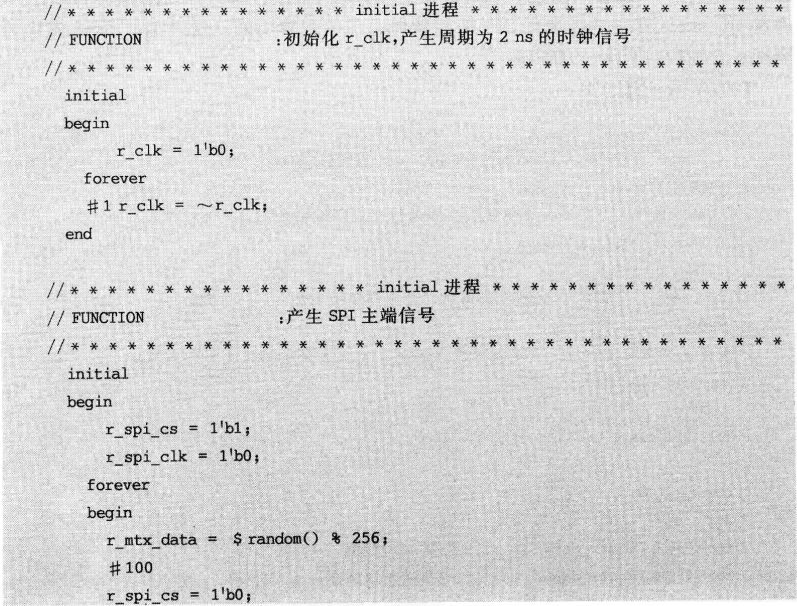

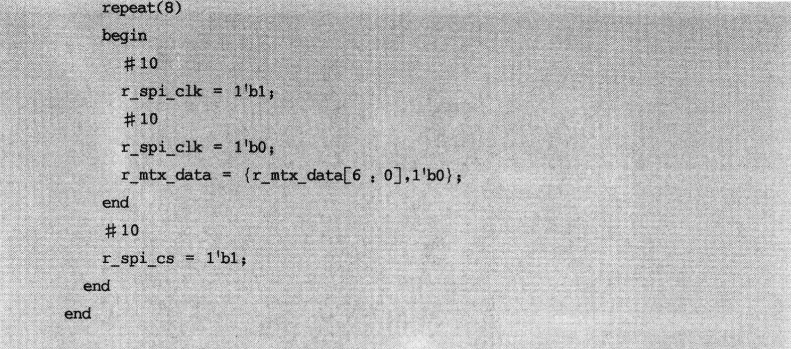

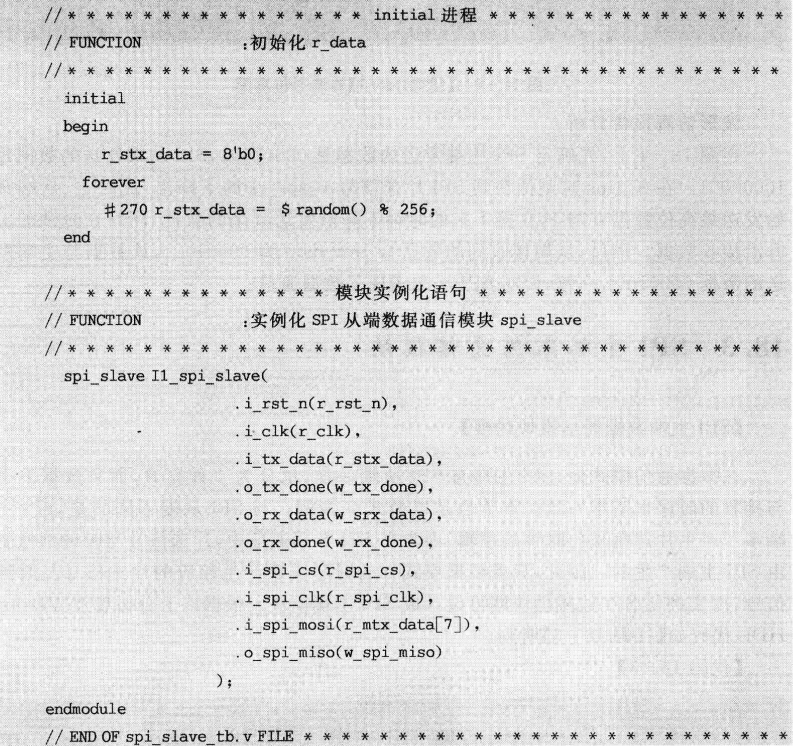

【代码18-1】编译无误后,设计【代码18-1】的测试平台,通过观察分析波形来确定spi_slave模块是否满足SPI从端数据通信的逻辑功能。设计spi_slave模块的测试平台如【代码18-2】所列。

【代码18-2】

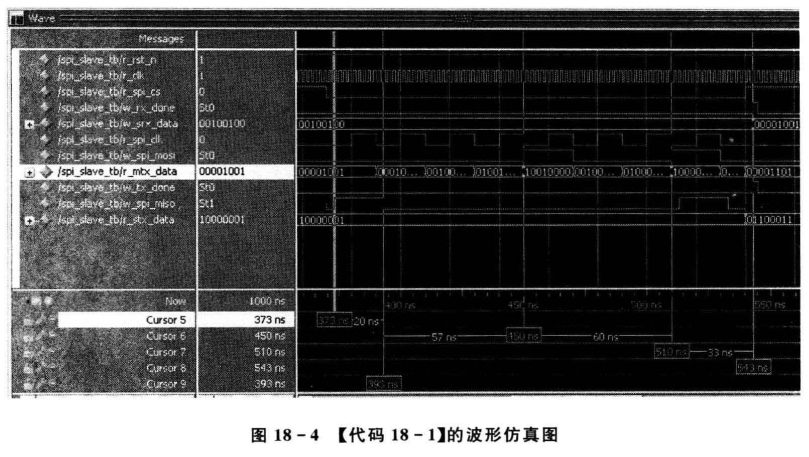

在ModelSim软件中对【代码18-1】进行波形仿真,如图18-4所示。

波形仿真报告分析

在图18-4上,先确定SPI主端发送的数据是00001001,SPI从端发送的数据是10000001。在373 ns时刻捕获到SPI片选信号r_spi_cs的下沿,此时主、从端开始发送最高位数据0与1,在接下来的时钟下降沿发送其余的数据,同时在时钟的上升沿接收数据。最后,从端接收到的数据w_ srx_data为00001001,该数据与主端发送的数据00001001一致,说明SPI从端实现了数据通信。

SPI主端数据通佶模块

SPI主端数据通信模块建模

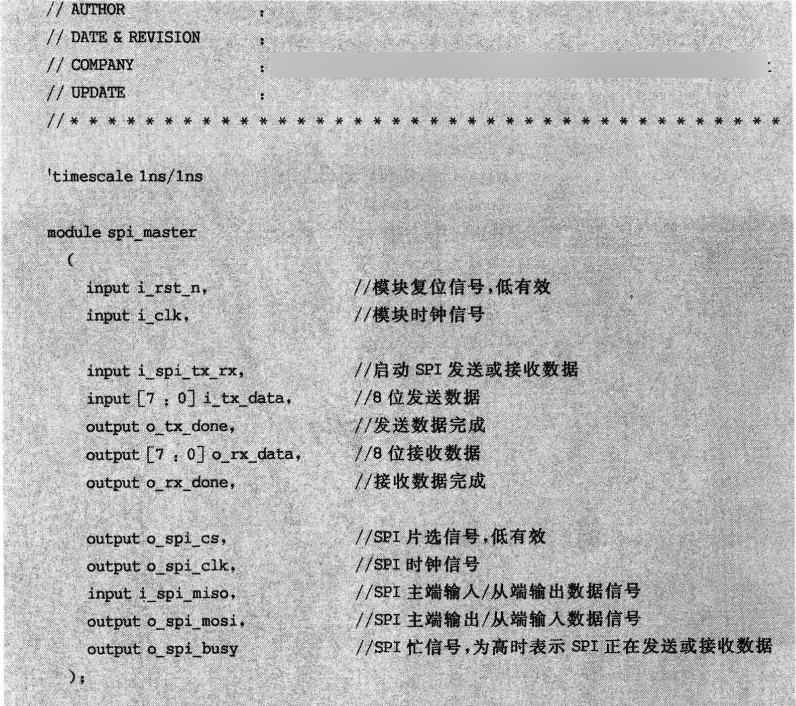

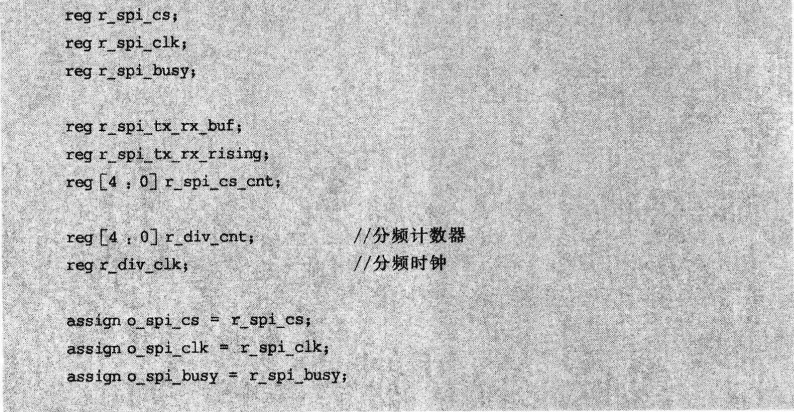

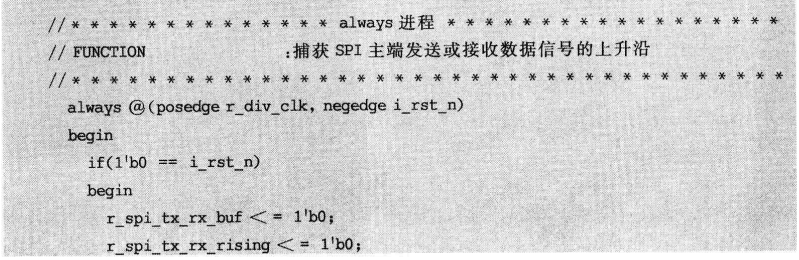

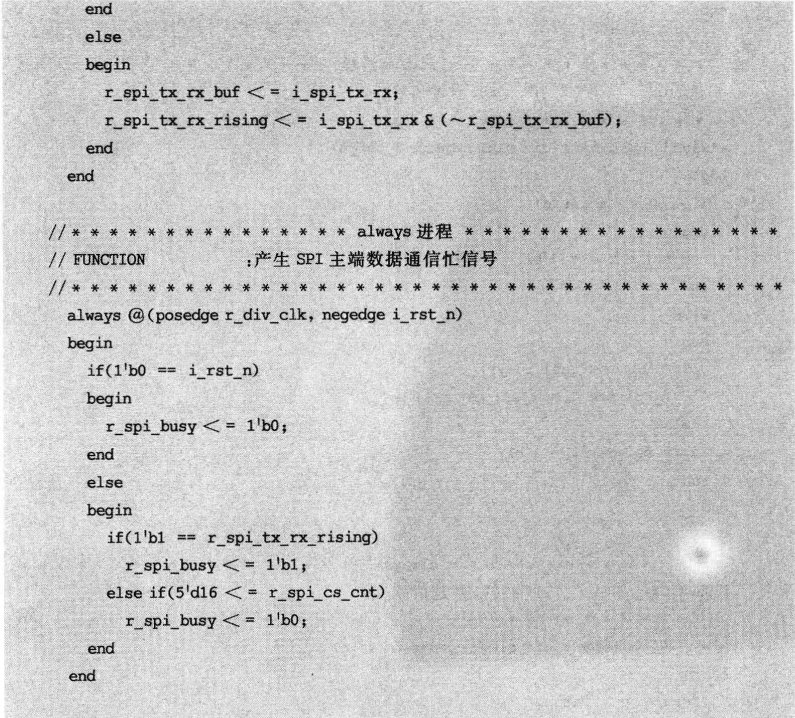

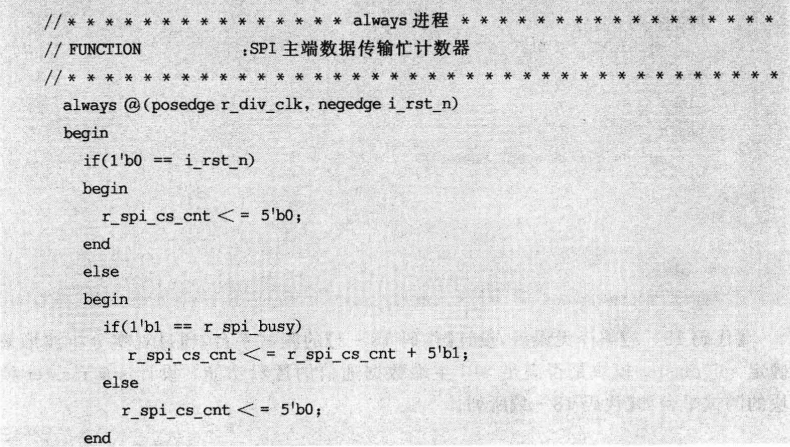

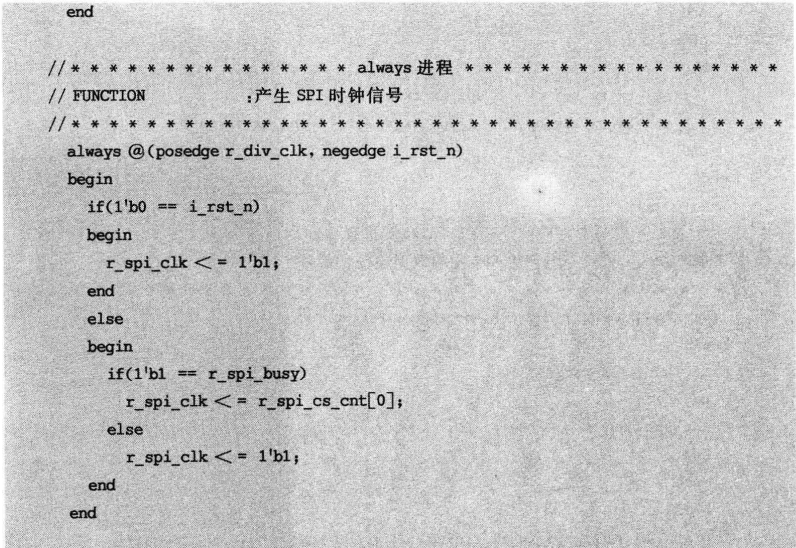

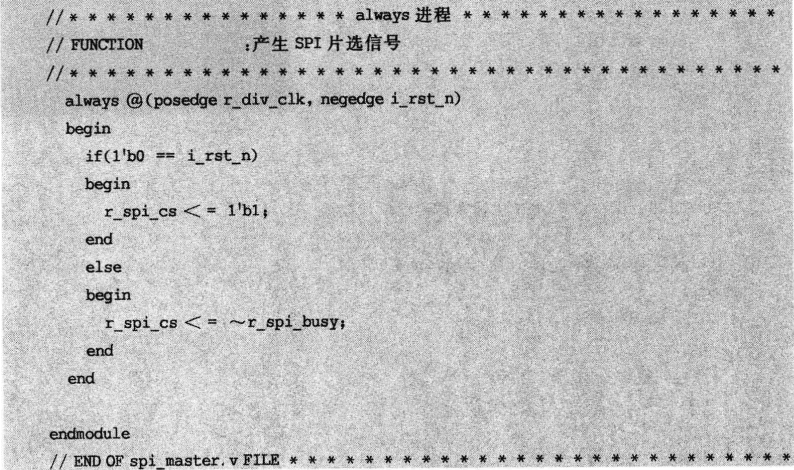

在数据通信模式上,SPI主端与SPI从端一样,也分为4种模式,而且数据发送与接收的时序也基本一致。本节也是以模式0为例。与SPI从端不同的是,SPI主端多了产生片选信号与时钟的逻辑,因为在SPI数据通信中,片选信号与时钟信号是由SPI主端产生的。因此,只要根据模式0的时序关系产生相应的片选信号与时钟信号,再实例化SPI从端模块即可设计成SPI主端模块。根据以上分析设计Verilog HDL代码如【代码18-3】所列。

【代码18-3】

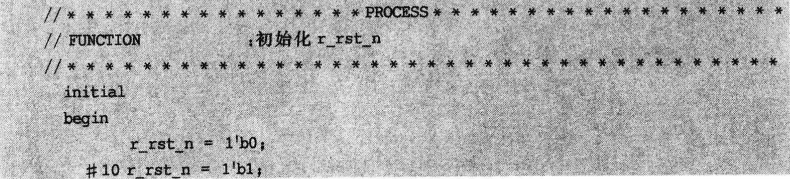

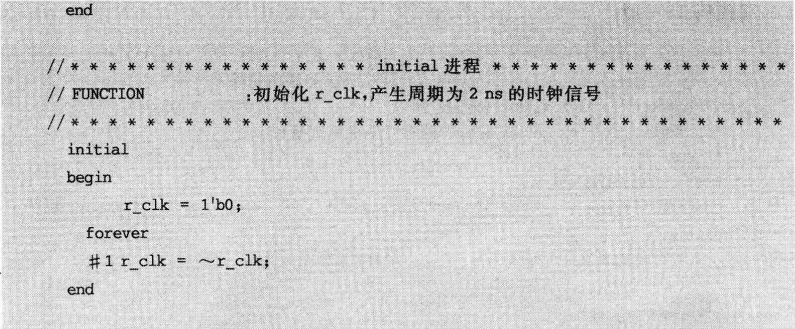

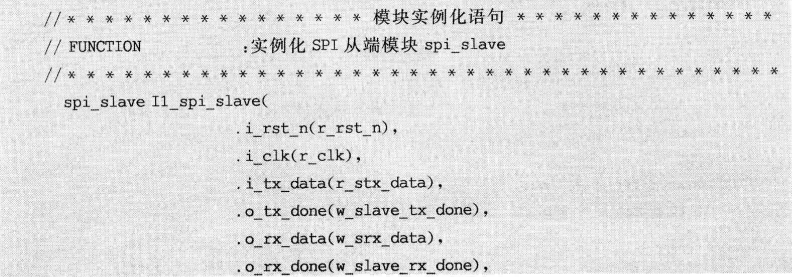

【代码18-3】编译无误后,设计【代码18-3】的测试平台,通过观察分析波形来确定spi_master模块是否满足SPI主端数据通信的逻辑功能。设计spi_master模块的测试平台如【代码18-4】所列。

【代码18-4】

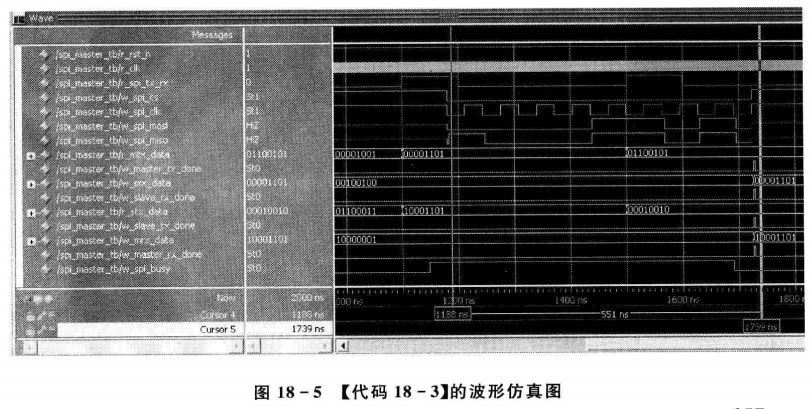

在ModelSim软件中对【代码18-3】进行波形仿真,如图18-5所示。

波形仿真报告分析

在图18-5上,先确定SPI主端发送的数据r_mtx_data是00001101,SPI从端发送的数据r_stx_data是00001101。经过8个SPI时钟周期之后,主、从端都接收到数据00001101,说明SPI主、从端实现了数据通信。

本篇知识点主要介绍有关SPI主、从端数据通信建模方面的内容,包括什么是SPI数据通信,四种SPI通信模式,以及SPI主、从端通信模块建模的具体方法。另外,我们还讲到如何基于Qsys的最小Nios II系统的搭建,基于其自带的IP模块的使用,包括了PIO模块、UART模块、定时器模块以及SPI模块等,基于Qsys的自定义外设、自定义指令的应用实例。

为了方便大家学习,编者这边给大家提供了非常系统的《Verilog HDL设计实战指导》书籍资料,并配套了全书完整实践项目课后练习源码,想系统学习了解的童鞋,可以扫码进群下载喔~