LPC2104/05/06基于16位/32位ARM7TDMI-S CPU,该CPU支持实时仿真和嵌入式跟踪,并拥有128 KB的嵌入式高速Flash存储器。128位存储器接口和独特的加速架构使得32位代码可在最高时钟速率下执行。对代码大小要求严格的应用程序,可选用的16位Thumb模式以最小的性能损失换取超过30%的代码压缩。

由于尺寸小,功耗低,对于小型化是一项关键要求的应用(如门禁控制和销售点),这些微控制器是理想之选。它们具有各种串行通信接口和高达64 KB的片内SRAM选项,非常适合于通信网关和协议转换器、软调制解调器、语言识别和低端成像,提供大缓冲容量和高处理能力两大优势。多个32位定时器、PWM通道和32个GPIO线使得这些微控制器尤其适用于工业控制和医疗系统领域。

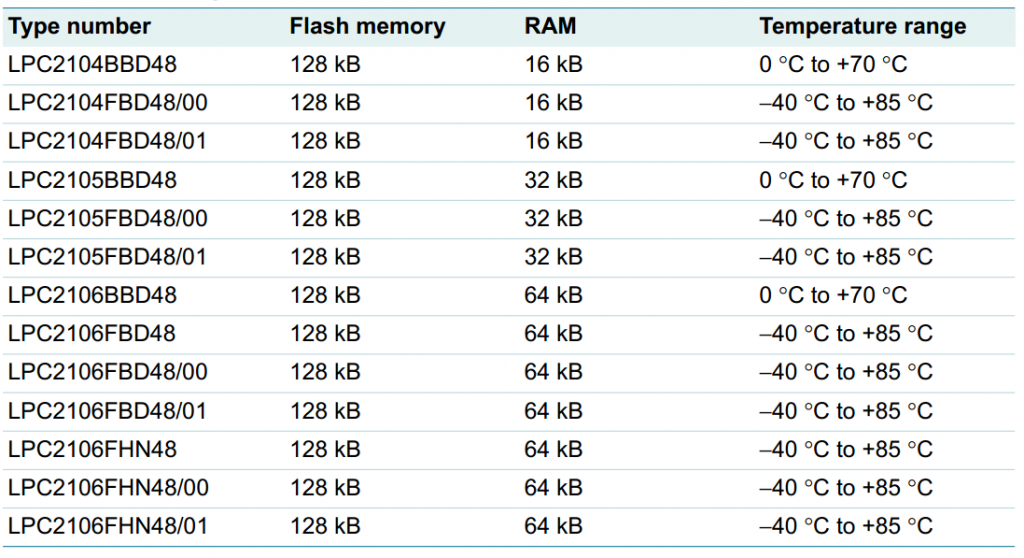

注:在整个数据表中,无论器件是否以/00和/01为后缀,LPC2104/2105/2106都将适用。后缀将用于区分包含新特性的器件。

存储器

Flash 0x0000 0000 ~ 0x0001 FFFF128KB

SRAM0x4000 0000 ~ 0x4000 3FFF16KB LPC2104

SRAM0x4000 0000 ~ 0x4000 7FFF32KB LPC2105

SRAM 0x4000 0000 ~ 0x4000 FFFF64KB LPC2106

ISP

管脚P0.14作为ISP 硬件请求时要特别注意。由于P0.14 在复位后处于高速模式,用户需要提供外部硬件(上拉电阻或其它器件)使管脚处于一个确定的状态。否则可能导致非预期的进入ISP 模式。

JTAG

LPC2106 存在主次两个JTAG。

主JTAG引脚:

引脚

功能

P0.17

TRST

P0.18

TMS

P0.19

TCK

P0.20

TDI

P0.21

TDO

RTCK (Pin26)

RTCK

DBGSEL (Pin27)

RESET(Pin6)

次JTAG引脚:

引脚

功能

P0.27

TRST

P0.28

TMS

P0.29

TCK

P0.30

TDI

P0.31

TDO

RTCK (Pin26)

RTCK

DBGSEL (Pin27)

RESET(Pin6)

JTAG 管脚选择

DBGSEL(复位后)

锁存的RTCK

主JTAG

次JTAG

ETM

1

1

是

否

是

0

1

否

软件配置

否

1

0

否

软件配置

否

0

0

否

软件配置

否

Flash 中的启动代码应当通过设定PINSEL1 寄存器当中的相应位将管脚P0.27~P0. 31 配置为JTAG功能。 JTAG 端口和ETM可选择只用于调试,见图40。

当DBGSEL和RTCK 管脚在复位时为高电平时,主要JTAG RTCK 只要有一个在复位时为低电平,主要JT AG端口或ETM都无法使能,而在以后的如果DBGSEL 和调试中也不能使用它们。但用户应用程序可将次要JT AG 功能分配给管脚P0.27~P0. 31 。当用户使用次要JTAG端口进行通信时,ETM功能将被禁止,因为ETM和次要JTAG共用相同的管脚,它们之间是互斥关系。

时钟计算

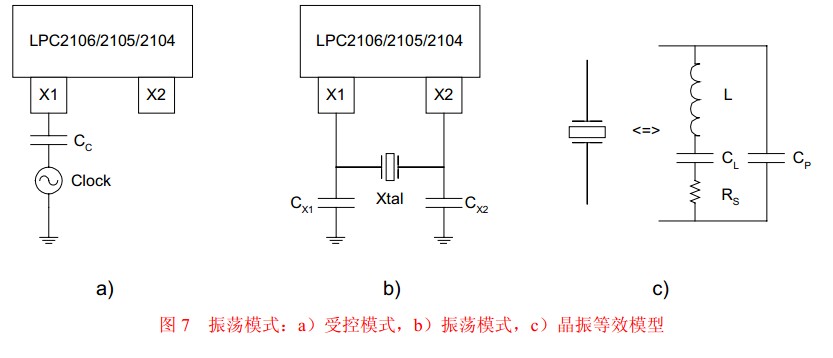

晶体振荡器

晶体振荡器 Cx1/Cx2的建议值

基本的振荡频率

晶振负载电容

CL

晶振最大串联电阻

RS

外部负载电容CX1, CX2

10~15MHz

10pF

< 300?

18pF, 18pF

20pF

< 220?

38pF, 38pF

30pF

< 140?

58pF, 58pF

15~20MHz

10pF

< 220?

18pF, 18pF

20pF

< 140?

38pF, 38pF

30pF

< 80?

58pF, 58pF

20~25MHz

10pF

< 160?

18pF, 18pF

20pF

< 90?

38pF, 38pF

30pF

< 50?

58pF, 58pF

系统时钟

M (1~32) 4

P (1,2,4,8) 2

Fosc(10MHz~25MHz) 14.7456MHz

Fcco(156MHz~320MHz) 235.9296MHz

Fcclk(10MHz~60MHz) 58.9824MHz

外设时钟

VPBDIC 1/4 14.7456MHz 00:(1/4) 01:(1) 10:(1/2) 11:(xx)

XCLKDIV

串口波特率

UARTnb = PCLK / 16 * (256 * UnDLM × UnDLL)