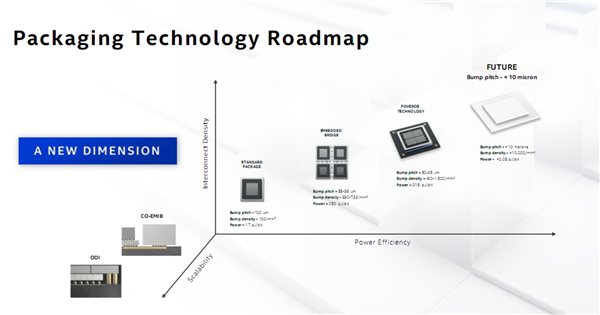

在Intel的六大技术支柱中,封装技术和制程工艺并列,是基础中的基础,这两年Intel也不断展示自己的各种先进封装技术,包括Foveros、Co-EMIB、ODI、MDIO等等。

本文引用地址:http://www.eepw.com.cn/article/202008/417173.htmIntel又宣布了全新的“混合结合”(Hybrid Bonding),可取代当今大多数封装技术中使用的“热压结合”(thermocompression bonding)。

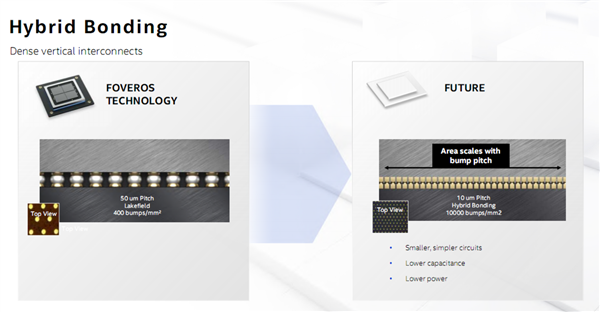

据介绍,混合结合技术能够加速实现10微米及以下的凸点间距(Pitch),提供更高的互连密度、更小更简单的电路、更大的带宽、更低的电容、更低的功耗(每比特不到0.05皮焦耳)。

Intel目前的3D Foveros立体封装技术,可以实现50微米左右的凸点间距,每平方毫米集成大约400个凸点,而应用新的混合结合技术,不但凸点间距能缩小到1/5,每平方毫米的凸点数量也能超过1万,增加足足25倍。

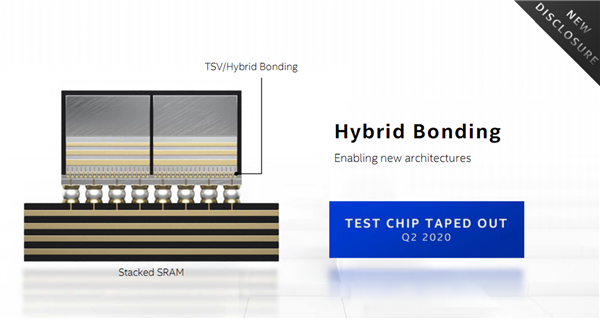

采用混合结合封装技术的测试芯片已在2020年第二季度流片,但是Intel没有披露未来会在什么产品上商用。

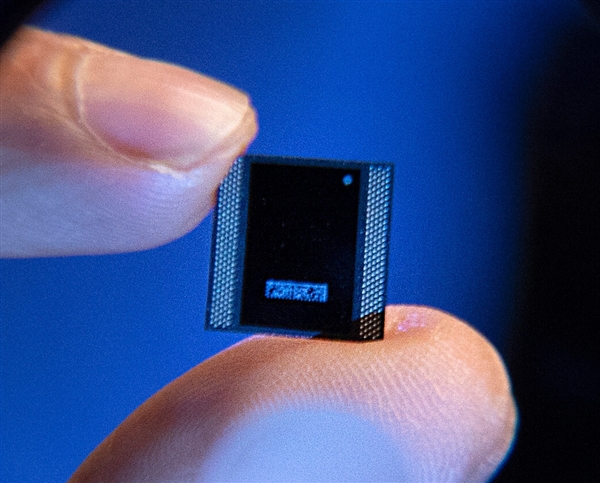

Foveros封装的Lakefield